Windows下verilog仿真环境的搭建

2、Windows下仿真环境的搭建

2.1 Debussy

Debussy是NOVAS Software, Inc(思源科技)发展的HDL Debug & Analysis tool,这套软体主要不是用来跑模拟或看波形,它最强大的功能是:能够在HDL source code、schematic diagram、waveform、state bubble diagram之间,即时做trace,协助工程师debug。当然你有Verdi更好,下面是Verdi和Debussy的比较:

(1) Debussy是Windows的版本,Verdi是Linux的版本,Debussy不支持64位Windows;

(2) Debussy & Verdi都是debug工具,不带仿真功能,仿真生成的vcd、vpd和fsdb都需要仿真工具;

(3) 使用Debussy & Verdi debug过程中,调入相同层次的波形文件就能debug,不需要跑仿真,不需要换代码;

(4) Debussy是早期的Windows版本,后期只在Linux中更新软件,即更新Verdi;

这是我下载Debussy的网址:

https://blog.csdn.net/immeatea_aun/article/details/80338390

2.2 Modelsim

Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。

Modelsim的具体使用教程可以参考以下网址,我只用到了功能仿真部分,时序仿真我没有涉及:http://m.elecfans.com/article/605114.html

这是我下载32位modelsim 10.1的网址:

https://www.cnblogs.com/emouse/archive/2012/05/05/2484481.html

2.3 Iverilog & GTKWave

Icarus Verilog is a Verilog simulation and synthesis tool. It operates as a compiler, compiling source code written in Verilog (IEEE-1364) into some target format. For batch simulation, the compiler can generate an intermediate form called vvp assembly. This intermediate form is executed by the “vvp” command. For synthesis, the compiler generates netlists in the desired format.

介绍的网址:http://iverilog.icarus.com/

下载的地址:http://bleyer.org/icarus/

注意一定要下载windows版本,因为windows版本才有-g2012的选项,该选项是支持system verilog的,若没有-g2012,rocket-chip的代码无法仿真,因为rocket-chip中带有了部分system verilog的语法。我下载的是iverilog-10.0-x86_setup版本。

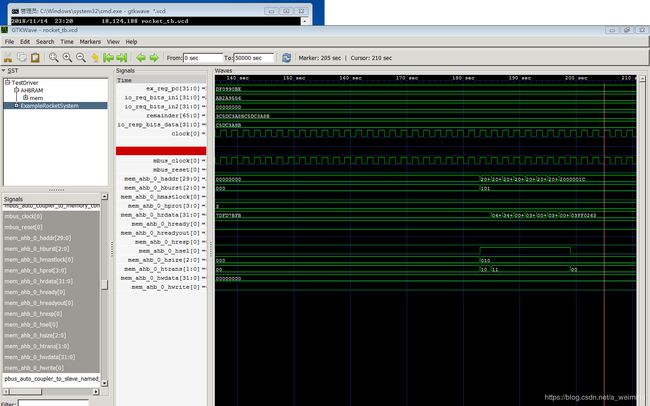

GTKWave is a fully featured GTK+ based wave viewer for Unix, Win32, and Mac OSX which reads LXT, LXT2, VZT, FST, and GHW files as well as standard Verilog VCD/EVCD files and allows their viewing.

介绍&下载的网址:http://gtkwave.sourceforge.net/

GTKWave有专门的user’s guide,有时间的大家可以研究一下。

运行Iverilog & GTKWave的步骤(cmd中可以自己粘贴windows下的复制):

1、利用VMwave生成rocket-chip的rtl和test的hex文件(此步以后会详细介绍);

2、利用cmd进入相应测试的目录;利用cmd进入相应测试的目录;

3、先运行iverilog,命令如下:先运行iverilog,命令如下:

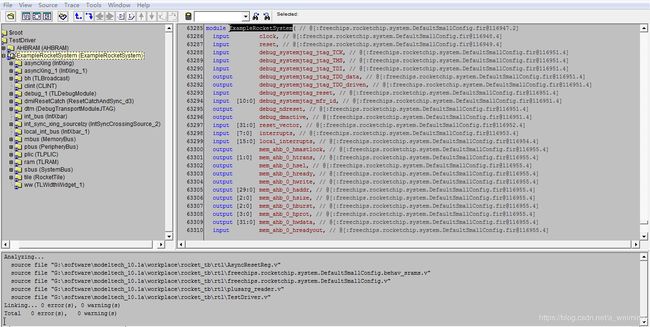

iverilog -g2012 -D SYNTHESIS -D RANDOMIZE_REG_INIT -D RANDOMIZE_MEM_INIT -D RANDOMIZE_GARBAGE_ASSIGN -D RANDOMIZE_INVALID_ASSIGN -o rocket_tb rtl/freechips.rocketchip.system.DefaultSmallConfig.v rtl/TestDriver.v rtl/AsyncResetReg.v rtl/plusarg_reader.v rtl/freechips.rocketchip.system.DefaultSmallConfig.behav_srams.v

选项说明:

-g2012:指定使用verilog的版本,基本的SystemVerilog语法都支持。

-D:引入宏定义,如果要运行rocket-chip的仿真,上面的宏定义必须带上,都是初始化的宏。

-o:输出文件的命名。

最后的是rtl的输入,要包括路径。

4、运行仿真,命令如下:

vvp -n rocket_tb -lxt2

5、观察波形:

gtkwave *.vcd