- Java pdf转jpg

tanzongbiao

Javajavaeureka开发语言

org.apache.pdfboxfontbox2.0.26org.apache.pdfboxpdfbox2.0.26PdfToJpgUtil.jpgpackagecom.qyj.utils;importorg.apache.pdfbox.pdmodel.PDDocument;importorg.apache.pdfbox.pdmodel.PDPageTree;importorg.apache.p

- C# 实现傅里叶变化(DFT)

大浪淘沙胡

C#c#开发语言DFT

1、DFT函数类usingSystem;usingSystem.Collections.Generic;usingSystem.Linq;usingSystem.Text;usingSystem.Threading.Tasks;namespaceDFT_FFTApp.Utils{publicclassDFT{//////DFT/////////publicstaticList>DFTNative(

- FTP服务基础搭建

时迁10

服务器linux运维

环境:两台rockyLinux虚拟机,yum仓库与时钟同步均已配置完成,firewalld与selinux均以关闭;server作为服务器端,client作为客户端。一、FTP理论FTP:文件传输协议(FileTransferProtocol简称FTP),采用c/s模式工作控制端口:21数据端口:20FTP工作原理:1、主动模式standardFTP客户端从任意一个非特权端口N(N>1024)发送

- 如何免费、免下载且完整地把PDF转换为Word

追思人别後

目前很多小伙伴们在工作或学习中会遇到PDF转换成word的需求,目前常见的方法一般都是让你下载软件,然后一堆广告,垃圾软件都进入你的电脑,然后提示你需要购买,需要注册,精疲力尽,头疼脑大。接下来小编就介绍如何免费、免下载并且完整地把PDF转换成Word。小编在这里推荐3款在线pdf转换平台:转转大师、www.bianjiepdf.com和www.PDFtodoc.cn。这3款PDF在线转换平台均只

- C语言编写FFT程序

唐维康

c语言FFT

徐士良老师编写的c语言算法程序下载链接:https://pan.baidu.com/s/1zDV6iLeYeXmZaoZlP4yRAA提取码:8opo一、什么是FFT?FFT(FastFourierTransformation)是离散傅氏变换(DFT)的快速算法。即为快速傅氏变换。它是根据离散傅氏变换的奇、偶、虚、实等特性,对离散傅立叶变换的算法进行改进获得的。二、FFT的作用FFT可以用来加速多

- [转载]构造Wannier90函数的要点

沺源

构造Wannier90函数的要点URL(以下内容最初来自“材料基因论坛”的Brook斑竹,本人只是内容进行了排版,如有不妥可以联系我进行删帖,具体可以参考帖子URLⅠ.构造Wannier函数通常要仔细调节以下三大参数:总能带数Num_bands,你需要有足够多的DFT能带数,以至于能够覆盖住你所需要研究的能带以及覆盖你投影子具有投影成分的能带。投影子projector。选择投影子之前,请彻底做一次

- FileZilla Server 1.8.1内网搭建

ZBzibing

FTPFileZilla

配置环境服务器服务器下载服务器配置服务器配置Server-ConfigureServerListeners-Port协议设置ProtocolssettingsFTPandFTPoverTLS(FTPS)Rightsmanagement(权利管理)Users(用户)客户端建立连接配置环境服务器处于局域网内:客户端公网路由器服务器服务器服务器下载下载地址:DownloadFileZillaServer

- Vsftpd服务器

Real_man

FTP是很常用的在计算机直接传输文件的协议,一方作为服务器,一方作为客户端。这里主要说下在Linux上一个常见的FTP服务器——vsftpdFTP工作方式FTP是有状态的协议,在FTP会话期间,客户端和服务端保持开放状态。客户端可以通过命令从服务端上传或者下载文件。有两种类型的连接:控制连接:也叫做命令连接数据连接当我们登陆FTP服务器的21端口时,发送用户名和密码进行认证,这个连接叫做控制连接。

- SpyGlass

飞奔的大虎

SpyGlass,这是一个很强大的RTL验证级工具。它不仅仅能检查sdc的错误,还能做以下各种检查:LowPower,DFT,CDC(CrossDomainCheck)。其中用得最多的就是CDC,到底什么是CrossDomainCheck呢?在一个设计中,通常都会有好几个clockdomain。这样就可能存在从一个clockdomain到另一个clockdomain的data或者control信号

- FFTW库安装与使用(3.3.5版本)

jhon-ranble

工具使用数字信号处理

FFTW库安装与使用一、FFTW库介绍与下载二、FFTW库安装三、FFTW库测试一、FFTW库介绍与下载 FFTW(theFasterFourierTransformintheWest)是一个快速计算离散傅里叶变换的标准C语言程序集,其由MIT的M.Frigo和S.Johnson开发。可计算一维或多维实和复数据以及任意规模的DFT,且运行速度比Eigen和opencv自带的FFT库函数快10倍以

- VCS后仿调试记录(Pre-PR)

小破同学

IC验证技术芯片经验分享

文章目录环境调整仿真参数UCLI命令X态清理仿真时间主要问题记录在项目搭建和调试后仿环境时做了很多工作,因此希望总结一下使用VCS做芯片后仿的步骤和遇到的一些主要问题。芯片后仿真又可分为PR前仿真(综合后)和PR后仿真(布局布线后),本文记录Pre-PR仿真的部分。环境调整PR前门仿采用的是RTL插入DFT后的综合网表,因此首先需要修改filelist,将原有top及各子模块RTL替换为综合后的网

- 芯片设计中的ECO

smartvxworks

芯片设计eco芯片芯片设计

如标题所写,我们今天聊一聊IC设计种的ECO。在展开关于ECO的概念之前,我们先大致捋下数字IC设计的流程,有助于我们后面的讨论。数字IC设计流程简述1、确定项目需求根据市场或者芯片功能要求,设计芯片的spec,得到可行的芯片设计方案。2、系统级设计用系统建模语言对各模块进行描述3、前端设计RTL设计、功能仿真、硬件原型验证、电路综合、DFT、STA4、后端设计版图设计、物理验证、后仿真在复杂的设

- Python将pdf转图片,下载照片/视频,编写Gui界面

程序媛一枚~

PythonOpenCVPython进阶图像处理pythonpdf音视频pdf2imagePythonGui界面

Python将pdf转图片,下载照片/视频,编写Gui界面效果图1.pdf转图片2.下载照片3.编写Gui界面参考效果图1.pdf转图片#PDFtoImages#pdf2image.py#pipinstallPyMuPDF#pipinstalltoolsimportosimportfitz#方法1defpdf_to_images(pdf_file):doc=fitz.open(pdf_file)f

- pdf转图片,nodejs图片切割、opencv处理图片灰度,批量扫描二维码

beforeDesotry

工具pdfopencvjavascriptpythonnode.js

项目场景:需求:公司做会员卡实体卡的项目,需要扫码绑定用户,制卡商给了一个pdf文件里面包含2000张会员卡要求确认印刷,需要扫描出二维码内容并确定问题描述这个任务被安排到我身上(本人前端),领导让手动扫码,作为一个程序员怎么可能干这么蠢的事呢,想着写个脚本解决一下,以下为解决步骤:1.首先要把pdf的每一页分开有一个很方便的网站iLovePDF|OnlinePDFtoolsforPDFlover

- STM32 KEIL-MDK DFP包下载

咸鱼丶的自我修养

单片机stm32

https://www.keil.com/dd2/pack/#/eula-container在网页下面找到STM32相应的DFT包直接下载即可

- Docker磁盘空间清理

margu_168

dockerdocker容器运维

Docker磁盘空间清理使用dockersystem命令清除*dockersystemdf命令,类似于Linux上的df命令,用于查看Docker的磁盘使用情况:[root@k8s-m1~]#dockersystemdfTYPETOTALACTIVESIZERECLAIMABLEImages14123.072GB744.8MB(24%)Containers2813621.1MB621.1MB(99

- Ubuntu18.04搭建ftp服务(亲测通过)

Echo_Xiaozhi

linux服务器ubuntu

安装:sudoapt-getinstallvsftpd#设置开机启动并启动ftp服务systemctlenablevsftpdsystemctlstartvsftpd启动:#查看其运行状态systemctlstatusvsftpd#重启服务systemctlrestartvsftpdftp用户:(需要主动创建非必须可用已有用户)sudouseradd-d/home/ftp/ftp_root-mft

- 使用C#读取PDF中所有文本内容

搬砖的诗人Z

C#c#pdf开发语言

先安装如下包usingiTextSharp.text.pdf;usingSystem;usingSystem.Collections.Generic;usingSystem.IO;usingSystem.Linq;usingSystem.Text;namespaceReadPdfText{classProgram{staticvoidMain(string[]args){stringpath="0

- CountVectorizer与TfidfVectorizer

卷心菜呀

导入fromskleran.feature_extraction.textimportCountVectorizer,TfidfTransformerfromsklearn.feature_extraction.textimportTfidfVectorizerCountVectorizer+TfidfTransformerCountVectorizer会将文本中的词语转换为词频矩阵,它通过fit

- Kubernetes实战(二十)-集群节点磁盘清理

alden_ygq

#Kubernetes系列kubernetesjava容器

1清理无用的镜像和关闭的容器1.1使用dockersystemdf查询Docker的磁盘使用情况$dockersystemdfTYPETOTALACTIVESIZERECLAIMABLEImages000B0BContainers000B0BLocalVolumes000B0BTYPE列出了Docker使用磁盘的4种类型:Images:所有镜像占用的空间,包括拉取下来的镜像,和本地构建的。Cont

- 频谱细化-----CZT算法介绍及MATLAB实现

YHCANDOU

频谱细化matlab算法开发语言

CZT变换采用FFT算法可以很快算出全部N点DFT值,即Z变换X(z)X\left(z\right)X(z)在Z平面单位圆上的全部等间隔取样值。实际中,也许不需要计算整个单位圆上Z变换的取样,如对于窄带信号,只需要对信号所在的一段频带进行分析,这时希望频谱的采样集中在这一频带内,以获得较高的分辨率,而频带以外的部分可不考虑,或者对其他围线上的Z变换取样感兴趣,例如语音信号处理中,需要知道Z变换的极

- 使用matlab写二维数字波束形成程序并输出

不卡不卡

matlab开发语言算法机器学习人工智能

使用MATLAB写二维数字波束形成程序的步骤是:1.使用离散傅立叶变换(DFT)计算输入信号的频谱;2.计算波束形成器的权重矩阵;3.使用矩阵乘法计算输出信号的频谱;4.使用逆离散傅立叶变换(IDFT)计算输出信号。最后,输出信号就是二维数字波束形成程序的结果。

- 芯片跨时钟域设计(二)

全栈芯片工程师

SoCrisc-v芯片芯片设计全流程培训数字芯片

芯片培训(真实项目)介绍:低功耗景芯SoC前端、中端、后端全流程实战培训(火爆订购中)DDR4/3项目实战培训ARMCortex-A72处理器12nmPR实战培训ARMCortex-A72处理器12nmDFT实战培训ARMCortex-A7处理器28nmPR实战培训(火爆价格战)RISC-VMCU40nm全芯片PR实战培训跨时钟域RTL设计与CDC实战UPF设计与低功耗仿真实战芯片DesignSe

- vue3 el-table-column 使用tooltip

hzxOnlineOk

vuevue.jsjavascriptecmascript

{{scope.row.dftParamVal}}

- pdf怎么转成高清图?pdf在线转换器推荐分享

喝奶茶嘛

pdf

在日常的工作或者学习中,有时候会需要将编辑好的pdf转高清图片,这样更方便我们后续使用,那么怎么将pdf转图片(https://www.yasuotu.com/pdftopic)还能保持清晰呢?下面介绍一款pdf转换工具,支持pdf在线转图片,我们可以直接在浏览器中就能将pdf转换成jpg图片格式了,一起来看看是如何操作的吧。打开压缩图网站,点击“PDF转换-PDF转图片”功能。上传PDF文档,点

- 集成电路可测性设计DFT技术入门概论--MBIST技术报告

也许只有四五次

芯片后端

集成电路DFT技术入门概论–MBIST技术报告1技术发展背景2国内外研究发展现状2.1国外研究发展现状2.2中国国内研究发展现状3基本MBIST算法4存储器的故障类型分类及相应测试方法1技术发展背景理想的测试追求测试成本低、故障覆盖率高。测试的主要目的其一是协助工艺厂商提升芯片良率,其二是为了在产品交付给客户之前剔除缺陷芯片。衡量芯片良率的重要指标称为缺陷级别(DefectLevel),它通过一个

- CRG设计之复位

biaobiao_hust

单片机fpga开发嵌入式硬件

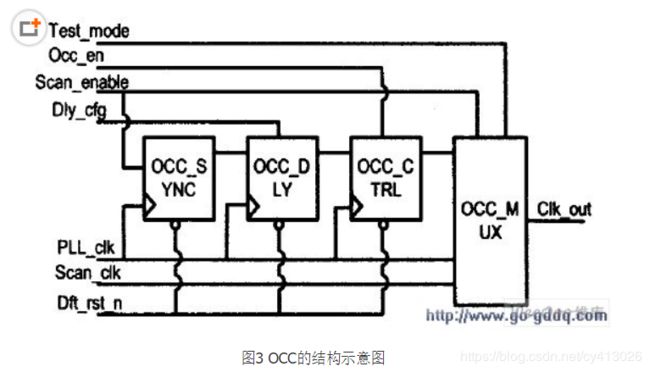

1.前言CRG(ClockandResetGeneration,时钟复位生成模块)模块扮演着关键角色。这个模块负责为整个系统提供稳定可靠的时钟信号,同时在系统上电或出现故障时生成复位信号,确保各个模块按预期运行。简而言之,CRG模块就像是SoC系统的心脏,提供着整个系统需要的时钟和复位信号。出于时钟复位结构规范设计和DFT可控的目的,一般会把相关电路放在一个集中的模块中管理,由专门的设计人员按需求

- 自然语言处理 TF-IDF

小嗷犬

深度学习自然语言处理tf-idf人工智能

✅作者简介:人工智能专业本科在读,喜欢计算机与编程,写博客记录自己的学习历程。个人主页:小嗷犬的个人主页个人网站:小嗷犬的技术小站个人信条:为天地立心,为生民立命,为往圣继绝学,为万世开太平。本文目录TF-IDF简介TF-IDF算法TFIDFTF-IDFTF-IDF的缺点TF-IDF简介TF-IDF(TermFrequency-InverseDocumentFrequency,词频-逆文档频率)是

- MATLAB实现图像变换

deleteeee

matlab计算机视觉图像处理经验分享笔记

1.目的使用MATLAB对图像进行频域变换操作2.原理1.二维离散傅里叶变换及反变换图像尺寸为M×N的函数f(x,y)的DFT为:u=0,1,2,…,M-1,v=0,1,2,…,N-1给出F(u,v),可通过反DFT得到f(x,y):x=0,1,2,…,M-1,y=0,1,2,…,N-1注:u和v是频率变量,x和y是空间域图像变量F(0,0)表示:2.二维DCT变换:f(i,j)是原始的信号,F(

- FFT海水学习笔记

胡说ba道

学习笔记线性代数

学习笔记信号分析原理DFT:IDFT:F(μ)为转换后的频域函数,μ为频率,f(x)为时域函数用欧拉公式展开得https://www.bilibili.com/video/av49238862欧拉公式的理解http://k.sina.com.cn/article_6367168142_17b83468e001004j89.html?sudaref=graph.qq.com&display=0&re

- Enum 枚举

120153216

enum枚举

原文地址:http://www.cnblogs.com/Kavlez/p/4268601.html Enumeration

于Java 1.5增加的enum type...enum type是由一组固定的常量组成的类型,比如四个季节、扑克花色。在出现enum type之前,通常用一组int常量表示枚举类型。比如这样:

public static final int APPLE_FUJI = 0

- Java8简明教程

bijian1013

javajdk1.8

Java 8已于2014年3月18日正式发布了,新版本带来了诸多改进,包括Lambda表达式、Streams、日期时间API等等。本文就带你领略Java 8的全新特性。

一.允许在接口中有默认方法实现

Java 8 允许我们使用default关键字,为接口声明添

- Oracle表维护 快速备份删除数据

cuisuqiang

oracle索引快速备份删除

我知道oracle表分区,不过那是数据库设计阶段的事情,目前是远水解不了近渴。

当前的数据库表,要求保留一个月数据,且表存在大量录入更新,不存在程序删除。

为了解决频繁查询和更新的瓶颈,我在oracle内根据需要创建了索引。但是随着数据量的增加,一个半月数据就要超千万,此时就算有索引,对高并发的查询和更新来说,让然有所拖累。

为了解决这个问题,我一般一个月会进行一次数据库维护,主要工作就是备

- java多态内存分析

麦田的设计者

java内存分析多态原理接口和抽象类

“ 时针如果可以回头,熟悉那张脸,重温嬉戏这乐园,墙壁的松脱涂鸦已经褪色才明白存在的价值归于记忆。街角小店尚存在吗?这大时代会不会牵挂,过去现在花开怎么会等待。

但有种意外不管痛不痛都有伤害,光阴远远离开,那笑声徘徊与脑海。但这一秒可笑不再可爱,当天心

- Xshell实现Windows上传文件到Linux主机

被触发

windows

经常有这样的需求,我们在Windows下载的软件包,如何上传到远程Linux主机上?还有如何从Linux主机下载软件包到Windows下;之前我的做法现在看来好笨好繁琐,不过也达到了目的,笨人有本方法嘛;

我是怎么操作的:

1、打开一台本地Linux虚拟机,使用mount 挂载Windows的共享文件夹到Linux上,然后拷贝数据到Linux虚拟机里面;(经常第一步都不顺利,无法挂载Windo

- 类的加载ClassLoader

肆无忌惮_

ClassLoader

类加载器ClassLoader是用来将java的类加载到虚拟机中,类加载器负责读取class字节文件到内存中,并将它转为Class的对象(类对象),通过此实例的 newInstance()方法就可以创建出该类的一个对象。

其中重要的方法为findClass(String name)。

如何写一个自己的类加载器呢?

首先写一个便于测试的类Student

- html5写的玫瑰花

知了ing

html5

<html>

<head>

<title>I Love You!</title>

<meta charset="utf-8" />

</head>

<body>

<canvas id="c"></canvas>

- google的ConcurrentLinkedHashmap源代码解析

矮蛋蛋

LRU

原文地址:

http://janeky.iteye.com/blog/1534352

简述

ConcurrentLinkedHashMap 是google团队提供的一个容器。它有什么用呢?其实它本身是对

ConcurrentHashMap的封装,可以用来实现一个基于LRU策略的缓存。详细介绍可以参见

http://code.google.com/p/concurrentlinke

- webservice获取访问服务的ip地址

alleni123

webservice

1. 首先注入javax.xml.ws.WebServiceContext,

@Resource

private WebServiceContext context;

2. 在方法中获取交换请求的对象。

javax.xml.ws.handler.MessageContext mc=context.getMessageContext();

com.sun.net.http

- 菜鸟的java基础提升之道——————>是否值得拥有

百合不是茶

1,c++,java是面向对象编程的语言,将万事万物都看成是对象;java做一件事情关注的是人物,java是c++继承过来的,java没有直接更改地址的权限但是可以通过引用来传值操作地址,java也没有c++中繁琐的操作,java以其优越的可移植型,平台的安全型,高效性赢得了广泛的认同,全世界越来越多的人去学习java,我也是其中的一员

java组成:

- 通过修改Linux服务自动启动指定应用程序

bijian1013

linux

Linux中修改系统服务的命令是chkconfig (check config),命令的详细解释如下: chkconfig

功能说明:检查,设置系统的各种服务。

语 法:chkconfig [ -- add][ -- del][ -- list][系统服务] 或 chkconfig [ -- level <</SPAN>

- spring拦截器的一个简单实例

bijian1013

javaspring拦截器Interceptor

Purview接口

package aop;

public interface Purview {

void checkLogin();

}

Purview接口的实现类PurviesImpl.java

package aop;

public class PurviewImpl implements Purview {

public void check

- [Velocity二]自定义Velocity指令

bit1129

velocity

什么是Velocity指令

在Velocity中,#set,#if, #foreach, #elseif, #parse等,以#开头的称之为指令,Velocity内置的这些指令可以用来做赋值,条件判断,循环控制等脚本语言必备的逻辑控制等语句,Velocity的指令是可扩展的,即用户可以根据实际的需要自定义Velocity指令

自定义指令(Directive)的一般步骤

&nbs

- 【Hive十】Programming Hive学习笔记

bit1129

programming

第二章 Getting Started

1.Hive最大的局限性是什么?一是不支持行级别的增删改(insert, delete, update)二是查询性能非常差(基于Hadoop MapReduce),不适合延迟小的交互式任务三是不支持事务2. Hive MetaStore是干什么的?Hive persists table schemas and other system metadata.

- nginx有选择性进行限制

ronin47

nginx 动静 限制

http {

limit_conn_zone $binary_remote_addr zone=addr:10m;

limit_req_zone $binary_remote_addr zone=one:10m rate=5r/s;...

server {...

location ~.*\.(gif|png|css|js|icon)$ {

- java-4.-在二元树中找出和为某一值的所有路径 .

bylijinnan

java

/*

* 0.use a TwoWayLinkedList to store the path.when the node can't be path,you should/can delete it.

* 1.curSum==exceptedSum:if the lastNode is TreeNode,printPath();delete the node otherwise

- Netty学习笔记

bylijinnan

javanetty

本文是阅读以下两篇文章时:

http://seeallhearall.blogspot.com/2012/05/netty-tutorial-part-1-introduction-to.html

http://seeallhearall.blogspot.com/2012/06/netty-tutorial-part-15-on-channel.html

我的一些笔记

===

- js获取项目路径

cngolon

js

//js获取项目根路径,如: http://localhost:8083/uimcardprj

function getRootPath(){

//获取当前网址,如: http://localhost:8083/uimcardprj/share/meun.jsp

var curWwwPath=window.document.locati

- oracle 的性能优化

cuishikuan

oracleSQL Server

在网上搜索了一些Oracle性能优化的文章,为了更加深层次的巩固[边写边记],也为了可以随时查看,所以发表这篇文章。

1.ORACLE采用自下而上的顺序解析WHERE子句,根据这个原理,表之间的连接必须写在其他WHERE条件之前,那些可以过滤掉最大数量记录的条件必须写在WHERE子句的末尾。(这点本人曾经做过实例验证过,的确如此哦!

- Shell变量和数组使用详解

daizj

linuxshell变量数组

Shell 变量

定义变量时,变量名不加美元符号($,PHP语言中变量需要),如:

your_name="w3cschool.cc"

注意,变量名和等号之间不能有空格,这可能和你熟悉的所有编程语言都不一样。同时,变量名的命名须遵循如下规则:

首个字符必须为字母(a-z,A-Z)。

中间不能有空格,可以使用下划线(_)。

不能使用标点符号。

不能使用ba

- 编程中的一些概念,KISS、DRY、MVC、OOP、REST

dcj3sjt126com

REST

KISS、DRY、MVC、OOP、REST (1)KISS是指Keep It Simple,Stupid(摘自wikipedia),指设计时要坚持简约原则,避免不必要的复杂化。 (2)DRY是指Don't Repeat Yourself(摘自wikipedia),特指在程序设计以及计算中避免重复代码,因为这样会降低灵活性、简洁性,并且可能导致代码之间的矛盾。 (3)OOP 即Object-Orie

- [Android]设置Activity为全屏显示的两种方法

dcj3sjt126com

Activity

1. 方法1:AndroidManifest.xml 里,Activity的 android:theme 指定为" @android:style/Theme.NoTitleBar.Fullscreen" 示例: <application

- solrcloud 部署方式比较

eksliang

solrCloud

solrcloud 的部署其实有两种方式可选,那么我们在实践开发中应该怎样选择呢? 第一种:当启动solr服务器时,内嵌的启动一个Zookeeper服务器,然后将这些内嵌的Zookeeper服务器组成一个集群。 第二种:将Zookeeper服务器独立的配置一个集群,然后将solr交给Zookeeper进行管理

谈谈第一种:每启动一个solr服务器就内嵌的启动一个Zoo

- Java synchronized关键字详解

gqdy365

synchronized

转载自:http://www.cnblogs.com/mengdd/archive/2013/02/16/2913806.html

多线程的同步机制对资源进行加锁,使得在同一个时间,只有一个线程可以进行操作,同步用以解决多个线程同时访问时可能出现的问题。

同步机制可以使用synchronized关键字实现。

当synchronized关键字修饰一个方法的时候,该方法叫做同步方法。

当s

- js实现登录时记住用户名

hw1287789687

记住我记住密码cookie记住用户名记住账号

在页面中如何获取cookie值呢?

如果是JSP的话,可以通过servlet的对象request 获取cookie,可以

参考:http://hw1287789687.iteye.com/blog/2050040

如果要求登录页面是html呢?html页面中如何获取cookie呢?

直接上代码了

页面:loginInput.html

代码:

<!DOCTYPE html PUB

- 开发者必备的 Chrome 扩展

justjavac

chrome

Firebug:不用多介绍了吧https://chrome.google.com/webstore/detail/bmagokdooijbeehmkpknfglimnifench

ChromeSnifferPlus:Chrome 探测器,可以探测正在使用的开源软件或者 js 类库https://chrome.google.com/webstore/detail/chrome-sniffer-pl

- 算法机试题

李亚飞

java算法机试题

在面试机试时,遇到一个算法题,当时没能写出来,最后是同学帮忙解决的。

这道题大致意思是:输入一个数,比如4,。这时会输出:

&n

- 正确配置Linux系统ulimit值

字符串

ulimit

在Linux下面部 署应用的时候,有时候会遇上Socket/File: Can’t open so many files的问题;这个值也会影响服务器的最大并发数,其实Linux是有文件句柄限制的,而且Linux默认不是很高,一般都是1024,生产服务器用 其实很容易就达到这个数量。下面说的是,如何通过正解配置来改正这个系统默认值。因为这个问题是我配置Nginx+php5时遇到了,所以我将这篇归纳进

- hibernate调用返回游标的存储过程

Supanccy2013

javaDAOoracleHibernatejdbc

注:原创作品,转载请注明出处。

上篇博文介绍的是hibernate调用返回单值的存储过程,本片博文说的是hibernate调用返回游标的存储过程。

此此扁博文的存储过程的功能相当于是jdbc调用select 的作用。

1,创建oracle中的包,并在该包中创建的游标类型。

---创建oracle的程

- Spring 4.2新特性-更简单的Application Event

wiselyman

application

1.1 Application Event

Spring 4.1的写法请参考10点睛Spring4.1-Application Event

请对比10点睛Spring4.1-Application Event

使用一个@EventListener取代了实现ApplicationListener接口,使耦合度降低;

1.2 示例

包依赖

<p