并口定义

一,管脚定义

| 管脚序号 |

管脚定义 |

方向 |

| 1,C0 | /STROBE ,数据选通,低电平有效 | Output |

| 2~9,D0~7 | DATA0~7,数据通道0~7 | 双向 |

| 10,S6 | /ACK,确认,低电平有效 | Input |

| 11,S7 | BUSY,表示打印机不能接收新的数据 | Input |

| 12,S5 | Paper End,表示没有打印纸 | Input |

| 13,S4 | Select,高电平表示联机,低电平表示脱机 | Input |

| 14,C1 | /AutoReed ,自动换行 | Output |

| 15,S3 | /ERROR,表示打印机出错、缺纸或者脱机状态 | Input |

| 16,C2 | /Initialize, 初始化,低电平有效 | Output |

| 17,C3 | Select In,低电平有效,表示数据可输入打印机 | Output |

| 18~25,G0~7 | GND,地 | Ground |

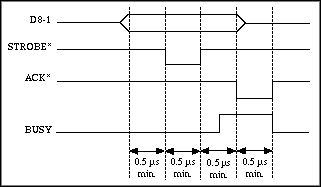

二、基本的SPP 模式的时序

三、寄存器

| 寄存器地址 | 寄存器 |

| 0x378 | SPP数据寄存器,DATA0~7的输入输出,依次对应管脚(9、8、7、6、5、4、3、2) |

| 0x379 | SPP状态寄存器,输入,依次对应管脚(11、10、12、13、15、x、x、x) |

| 0x37A | SPP控制寄存器,输出,依次对应管脚(x、x、x、并口中断允许位、17、16、14、1) |

| 0x37B | EPP地址寄存器(一般不用),可读可写 |

| 0x37C | EPP扩展数据寄存器(一般不用),可读可写 |

也就是说PC的0x378可以用来做输入和输出,0x37A的低4位可以用来输出,0x379是输入。这样就可以用并口模拟很多接口时序,比如I2C、SMI、JTAG、SPI等,也可以用来当做开关控制其他设备。这个时候不用管第一节中的Centronics打印机标准接口的那些信号定义,只用处理输入输出D0~7,输出C0~3,输入S3~7即可。

注:现在市面上很多PC已经没有并口了,需要购买PCIe转并口的转接卡,这时并口的基地址不再是0x378,而可能是0xD050或者0xE050等,此时只需寄存器地址修改即可。

四、硬件接口

并行接口输出的是TTL标准的逻辑电平,输入信号也要符合TTL标准。这种特性可以使接口容易应用在电子设计中。大部分的PC并行接口能吸收和输出12mA左右的电流,如应用时小于或大于这个值,应使用缓冲电路。

为了保持与早期的Centronics 接口兼容,使用OC(open collector)驱动器,使用上拉电阻(pull-up resistor)标准电阻值为2.2k欧或4.7k欧。控制线与状态线仅要求上拉电阻Rp,数据线和Strobe线还要求串联电阻Rs来匹配线路阻抗,调整串联电阻值使其与驱动器的输出阻抗之和等于45欧到55欧的线路阻抗。比如驱动IC输出阻抗为15欧,则需要33欧的串联电阻。

五、并口编程

一般利用现成的inpout32.dll或者WinIo.dll动态链接库来做。

参考资料:

https://blog.csdn.net/xyk0318/article/details/52033878

http://www.elecfans.com/baike/computer/taishiji/20100309183757.html?v=pc