STM32F103 SDIO(一)

void SD_LowLevel_DeInit(void)

主要软件设置SDIO时钟和电源失能同时恢复SDIO缺省值,使SDIO时钟失能并SD卡数据,时钟,命令端口浮空

{

GPIO_InitTypeDef GPIO_InitStructure;

/*!< Disable SDIO Clock */

SDIO_ClockCmd(DISABLE);

/*!< Set Power State to OFF */

SDIO_SetPowerState(SDIO_PowerState_OFF);

/*!< DeInitializes the SDIO peripheral */

SDIO_DeInit();

/*!< Disable the SDIO AHB Clock */

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_SDIO, DISABLE);

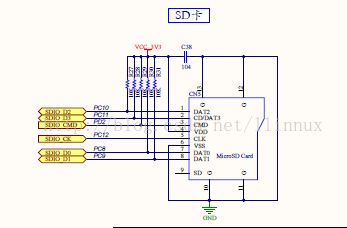

/*!< Configure PC.08, PC.09, PC.10, PC.11, PC.12 pin: D0, D1, D2, D3, CLK pin */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 | GPIO_Pin_11 | GPIO_Pin_12;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING;

GPIO_Init(GPIOC, &GPIO_InitStructure);

/*!< Configure PD.02 CMD line */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2;

GPIO_Init(GPIOD, &GPIO_InitStructure);

}

void SD_LowLevel_Init(void)

主要是配置SD卡数据,时钟,命令端口,同时使能SDIO时钟,并开启DMA2时钟

{

GPIO_InitTypeDef GPIO_InitStructure;

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOC | RCC_APB2Periph_GPIOD, ENABLE);

/*!< Configure PC.08, PC.09, PC.10, PC.11, PC.12 pin: D0, D1, D2, D3, CLK pin */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 | GPIO_Pin_11 | GPIO_Pin_12;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOC, &GPIO_InitStructure);

/*!< Configure PD.02 CMD line */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2;

GPIO_Init(GPIOD, &GPIO_InitStructure);

/*!< Enable the SDIO AHB Clock */

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_SDIO, ENABLE);

/*!< Enable the DMA2 Clock */

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_DMA2, ENABLE);

}

void SD_LowLevel_DMA_TxConfig(uint32_t *BufferSRC, uint32_t BufferSize)

首先清除DMA2_FLAG_TC4 通道4传输完成标志位 DMA2_FLAG_TE4 通道4传输错误标志位 DMA2_FLAG_HT4 通道4传输过半标志位 DMA2_FLAG_GL4通道4全局标志位;然后失能DMA14通道,再进行DMA14通道初始化,使能DMA14通道的中断

{

DMA_InitTypeDef DMA_InitStructure;

DMA_ClearFlag(SD_SDIO_DMA_FLAG_TC | SD_SDIO_DMA_FLAG_TE | SD_SDIO_DMA_FLAG_HT | SD_SDIO_DMA_FLAG_GL);

/*!< DMA2 Channel4 disable */

DMA_Cmd(SD_SDIO_DMA_CHANNEL, DISABLE);

/*!< SDIO DMA CHANNEL Config */

DMA_InitStructure.DMA_PeripheralBaseAddr = (uint32_t)SDIO_FIFO_ADDRESS; #define SDIO_FIFO_ADDRESS ((uint32_t)0x40018080)

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

DMA_InitStructure.DMA_MemoryBaseAddr = (uint32_t)BufferSRC;

DMA_InitStructure.DMA_DIR = DMA_DIR_PeripheralDST;

DMA_InitStructure.DMA_BufferSize = BufferSize / 4;

DMA_InitStructure.DMA_PeripheralInc = DMA_PeripheralInc_Disable;

DMA_InitStructure.DMA_MemoryInc = DMA_MemoryInc_Enable;

DMA_InitStructure.DMA_PeripheralDataSize = DMA_PeripheralDataSize_Word;

DMA_InitStructure.DMA_MemoryDataSize = DMA_MemoryDataSize_Word;

DMA_InitStructure.DMA_Mode = DMA_Mode_Normal;

DMA_InitStructure.DMA_Priority = DMA_Priority_High;

DMA_InitStructure.DMA_M2M = DMA_M2M_Disable;

DMA_Init(SD_SDIO_DMA_CHANNEL, &DMA_InitStructure);

DMA_ITConfig( DMA2_Channel4, DMA_IT_TC, ENABLE);

/*!< SDIO DMA CHANNEL enable */

DMA_Cmd( DMA2_Channel4, ENABLE);

}

引用:FIFO

有关FIFO的资料参考:异步FIFO的FPGA实现

数据FIFO(先进先出)子单元是一个具有发送和接收单元的数据缓冲区。

FIFO包含一个每字32位宽、共32个字的数据缓冲区,和发送与接收电路。因为数据FIFO工作在AHB 时钟区域(HCLK/2),所有与SDIO时钟区域(SDIOCLK)连接的信号都进行了重新同步。依据TXACT和RXACT标志,可以关闭FIFO、使能发送或使能接收。TXACT和RXACT 由数据通道子单元设置而且是互斥的:

─ 当 TXACT 有效时,发送 FIFO 代表发送电路和数据缓冲区

─ 当 RXACT 有效时,接收 FIFO 代表接收电路和数据缓冲区