FPGA QuartusII 13.0.1+ModelSim SE 10.1a联合仿真以及Hello World测试程序

一、实验环境(蓝色粗体字为特别注意内容)

1,环境:Windows 7 Ultimate 32 bit、QuartusII 13.0.1 win32、ModelSim SE 10.1a win32

2,参考文献:

①http://bbs.eeworld.com.cn/thread-530964-1-1.html

②https://www.cnblogs.com/Jezze/archive/2012/09/14/2684333.html

③https://www.cnblogs.com/yuesheng/archive/2011/06/25/2090385.html ④https://www.cnblogs.com/luckybag/articles/3803991.html

⑤http://www.eefocus.com/nightseas/blog/12-03/242395_7df71.html ⑥https://blog.csdn.net/ocean1171597779/article/details/25885105 ⑦https://www.jb51.net/softs/561414.html ⑧https://blog.csdn.net/qq_18649781/article/details/81025650

二、详细步骤

2.1 QuartusII 13.0.1安装&破解

1)按照参考文献⑧的步骤,到度盘链接:https://pan.baidu.com/s/1I_6-9f0wvEpF_utkTjjsUQ 密码:u6ef,将QuartusSetup-13.0.1.232还有破解器下载到电脑本地磁盘(cyclone好像不用下,QuartusSetup自带,如果实在需要再下载,反正我下载下来安装的时候提示我已经安装过了,无语。。。)。

2)双击QuartusSetup-13.0.1.232.exe,选择安装位置,一路next将Quartus安装到本地磁盘。最后,done!

3)如果你的电脑是32位,将破解器中的“Quartus_13.0_x86破解器.exe”复制到 “你的安装路径\quartus\bin”目录下面,并且双击,将生成的"license"保存。

4)如果你的电脑是64位,将破解器中的“Quartus_13.0_x64破解器.exe”复制到 “你的安装路径\quartus\bin64”目录下面,双击,将生成的"license"保存。

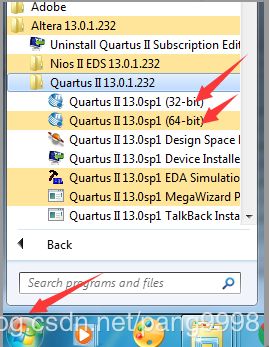

5)选择对应版本,打开QuartusII,Tools->License Setup->(NIC)ID 选择第一个作为CID复制之,关闭Quartus。

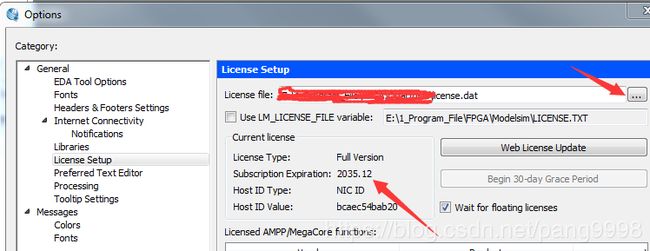

6)打开之前保存的"licence.dat",将(NIC)ID替换掉里面的xxxxxxx,打开Quartus 定位到Tools->License Setup,License file选择刚刚修改的license.dat,出现以下界面说明破解完成

2.2 ModelSim SE 10.1a安装&破解

ModelSim是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器,比Quartus自带的仿真器要强大很多,它采用直接优化的编译技术、Tcl/Tk技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段,是FPGA/ASIC设计的首选仿真软件。目前有se、de、pe等多个版本,对应Altera和Xilinx还有对应的OEM版本,所有的版本功能最强速度最快的就是se,反正也是要破解,自然就装最强的版本了,和Altera网站上的modelsim的区别在于,se的版本我们需要自己编译对应的库,所以Altera和Xilinx的都是自带对应的库无需编译的,像我这样同时装了Quartus II和ISE的,自然还是自己编译方便一点。

1)按照参考文献⑦,将modelsim se 10.1c emouse.rar下载到本地,解压之。

2)双击modelsim-win32-10.1a-se.exe选择安装路径,安装之,最后弹出一个对话框,点击“NO”即可。

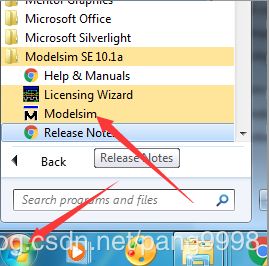

3)将MentorKG.exe和crack.bat文件复制到安装根目录win32目录下,运行crack.bat文件,生成txt文件后另存为LICENSE.TXT

4)我的电脑右键->属性->高级->环境变量,新增系统环境变量LM_LICENSE_FILE,值为LICENSE.TXT的路径,如:D:\modeltech_10.1a\LICENSE.TXT

5)运行Modelsim

2.3 编写测试程序

按照参考文献①

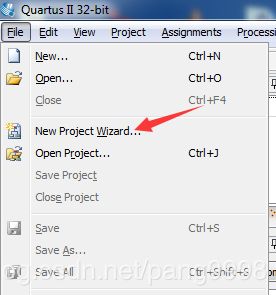

第一步:新建工程

File --> New Project Wizard...

1.选择工程目录,指定工程名及设计入口,一般情况下建议工程目录,工程名称及设计入口同名,不能有中文路径;

2.添加已有文件,如果新建的工程,则直接跳过;

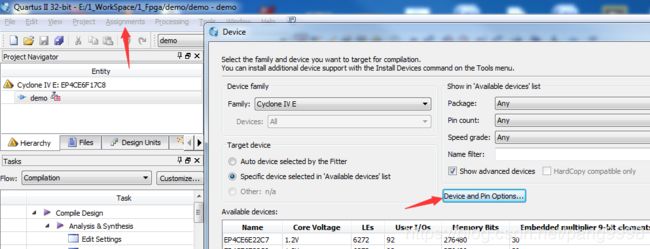

3.器件选择,需要与实际用到的器件相同,Family选择Cyclone IV E,Available device这里选择EP4CE6F17C8;

4.设置工具,一般直接next跳过;

5.信息确认,如果无误则点击Finish完成;

修改默认配置:

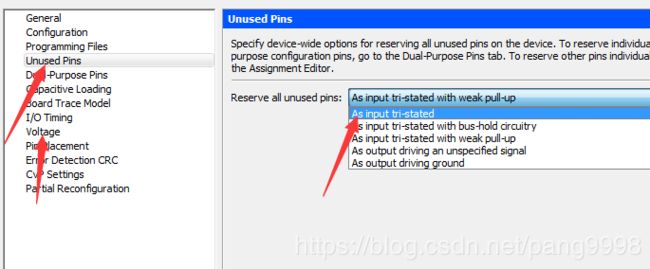

Assignments --> Device...

--> Device and Pin Option...

Unused Pins:未用到引脚选择,As input tri-stated;

Valtage 引脚默认电压值,选择 3.3-V LVTTL;

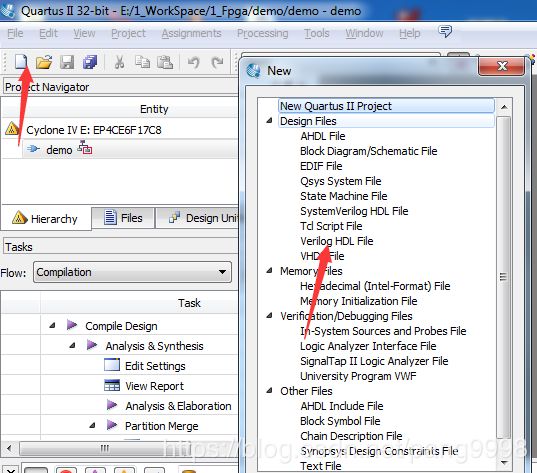

第二步:建立HDL文件

File--> New...

Design Files --> Verilog HDL File内容如下:

/*

* 功能描述:流水灯演示

*/

module demo (

input clk, // 时钟输入(外部50MHz晶振)

input rst_n, // 复位按键

output reg [3:0] led // 4位LED

);

// 寄存器定义

reg [31:0] timer; // 用于定时器计数

// 计时时钟

always @(posedge clk or negedge rst_n)

begin

if(~rst_n)

timer <= 0;

else if(timer == 32'd200_000_000)

timer <= 0;

else

timer <= timer + 1'b1; // 通过脉冲数计算时间

end

// 检测时钟的下降沿和复位的下降沿

always @(posedge clk or negedge rst_n)

begin

if (~rst_n) // 复位信号低电平有效

led <= 4'b0000; // LED灯输出全为低,四个LED灯灭

// 时钟下降沿

else

begin

// 50HMz的时钟下,50个时钟为1us

if(timer == 32'd50_000_000)

led <= 4'b0001;

else if (timer == 32'd100_000_000)

led <= 4'b0010;

else if (timer == 32'd150_000_000)

led <= 4'b0100;

else if (timer == 32'd200_000_000)

led <= 4'b1000;

end

end

endmodule

保存文件,名称与之前设置的入口文件相同;(不然会出现报错①)

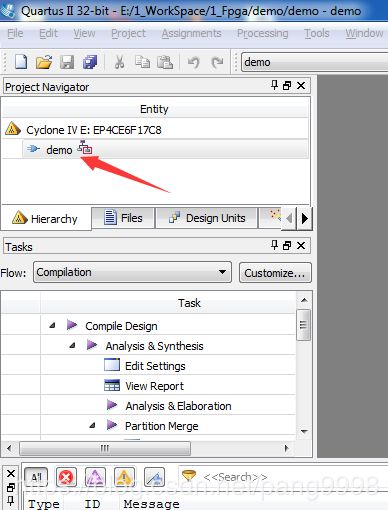

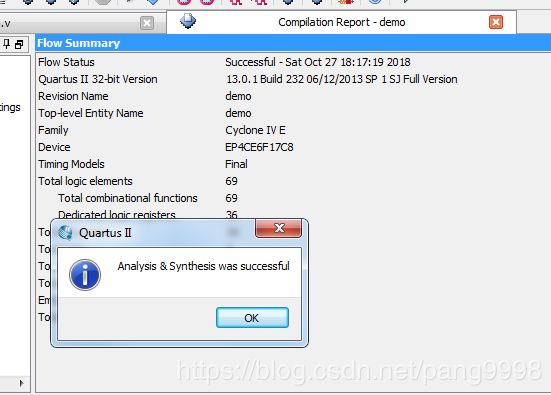

第三步:综合

点击Analysis & Synthesis进行综合;

成功

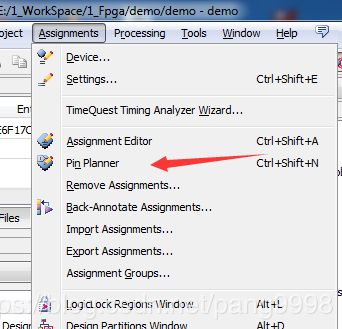

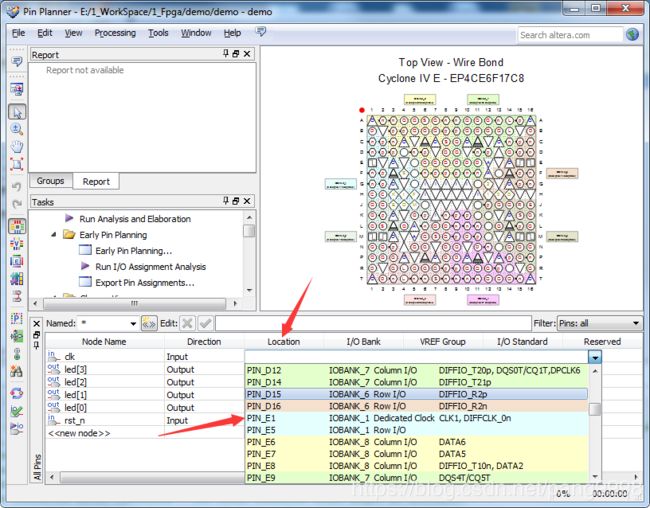

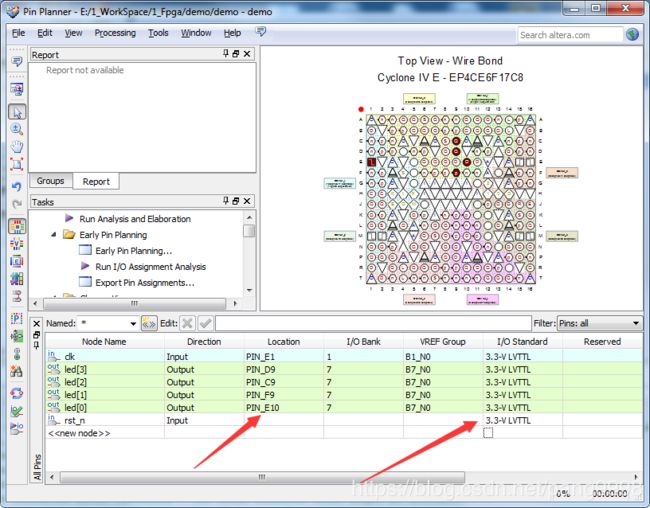

第四步:引脚分配

Assignments --> Pins Planner打开引脚分配页面进行分配;

双击引脚对应的Location,弹出引脚选择下拉列表

按照原理图上分配对应的引脚:

CLK --> E1

LED0 --> E10

LED1 --> F9

LED2 --> C9

LED3 --> D9

I/O Standard 根据实际电路选择电平标准,这里选择3.3-V LVTTL;

同一个Bank的引脚的电平标准必须相同;

注意事项:

必须综合之后,才能进行引脚分配,否则系统并不知道你用了哪些引脚;

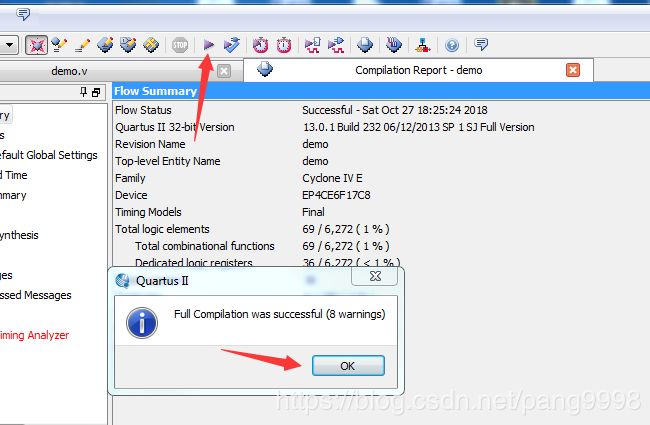

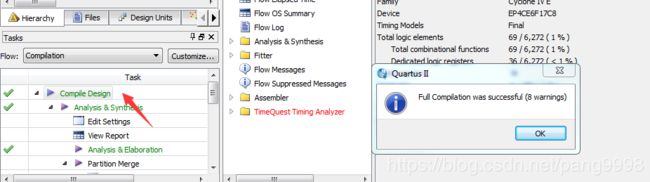

第五步:编译

双击Complile Design进行全编译;

或者点击

第六步:下载测试

通过JTAG下载至RAM

点击Program Device打开编译器;

点击Add File...添加output_files目录下生成的sof文件;

点击Start即可进行下载;

下载完成后会自动运行,掉电后会丢失;

固化至配置芯片

文件转换:

File --> Convert Programming Files...

Programming file type:

选择文件格式,指定为jic格式,JTAG Indirect Configuration File(.jic)

Configuration device:

选择配置芯片型号,与目标板上的型号一致(EPCS16)

Flash Loader:与目标板上FPGA的类别一致;

Sof Data:选择编译好的sof文件;

点击Generate生成jic目标文件;

(此时可选择Save Conversion Setup... 保本配置参数,以便下次调入)

下载固化:

点击Program Device打开编译器;

点击Add File...添加output_files目录下生成的jic文件;

点击Start即可进行下载;

下载完成后,不会自动运行,需要重上电才能正常运行;

注意事项:

一般只有在完成调试完成后,交付测试时才需要固化,而在调试过程中,则没必要进行固化下载;

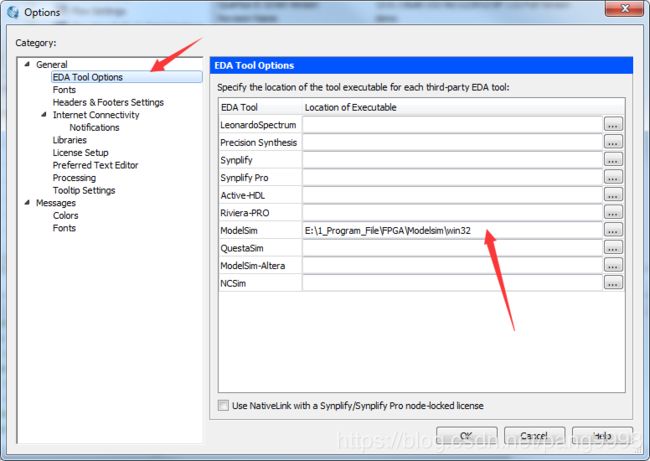

2.4 Modelsim联合仿真

1)按照参考文献②,第一次用modelsim+quartus的时候需要在quartus中设置modelsim的路径,quartus->tools->options->general->EDA tool options ,在右边选择modelsim的安装路径\win32,如下图:

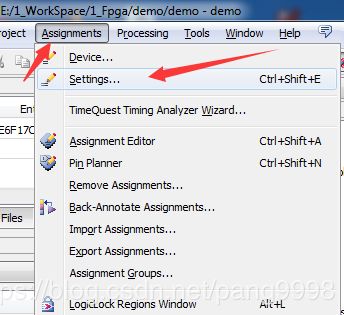

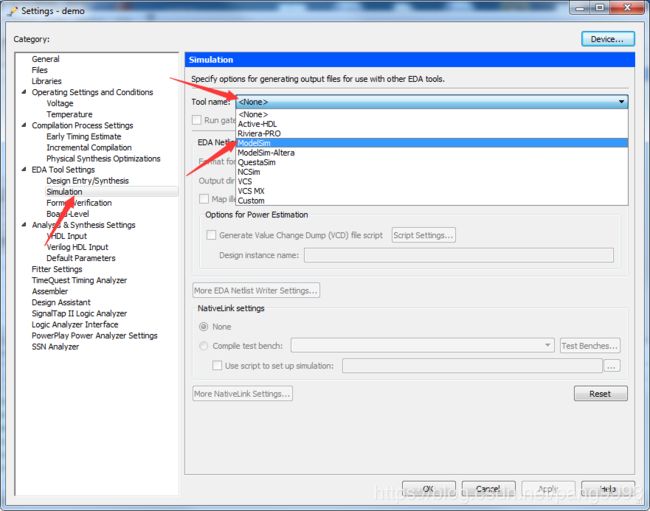

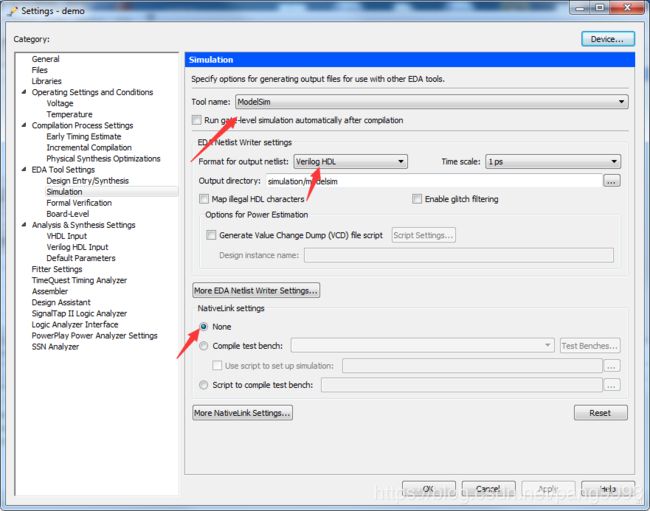

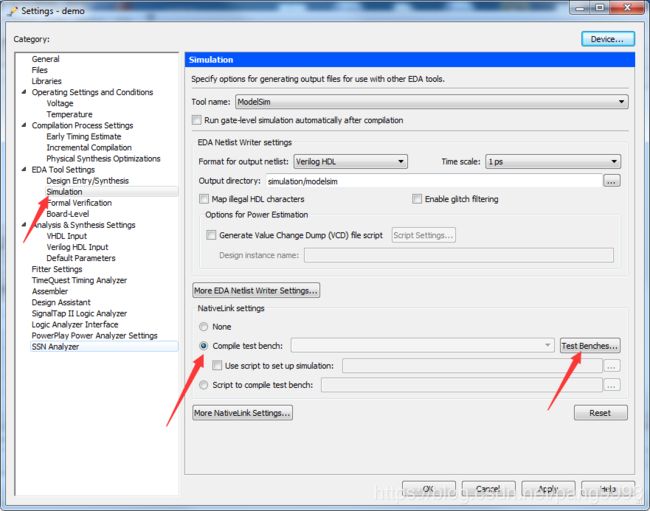

2)点击Quartus->Assignments->Settings

选择Simulation->Tool name选择ModelSim

先选择TestBenche None,点击OK

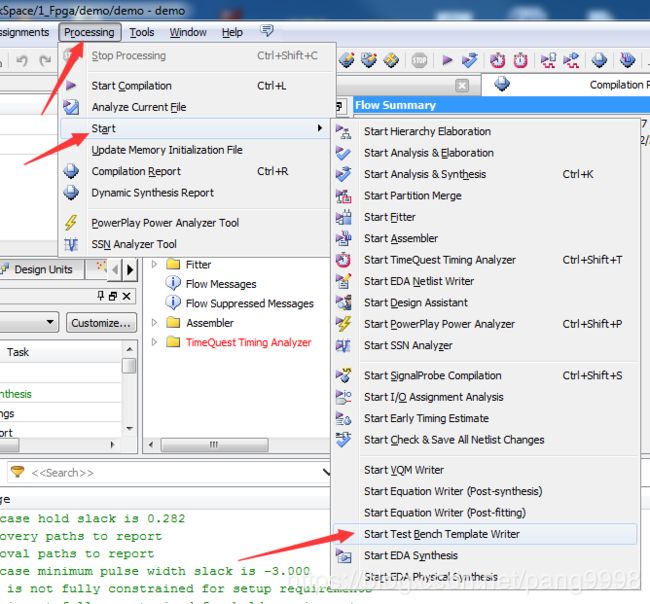

3)建立TestBench模板

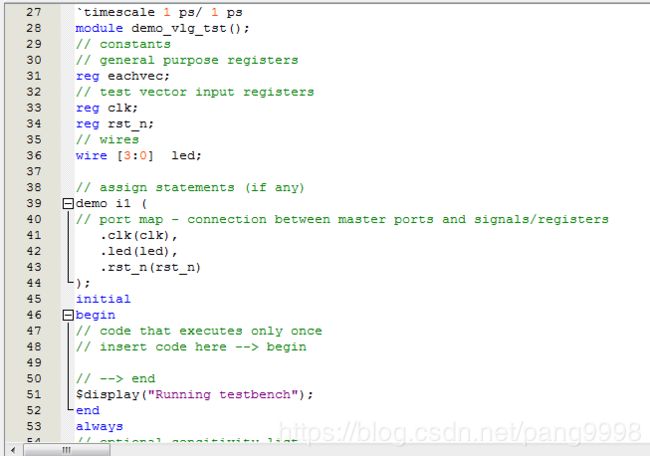

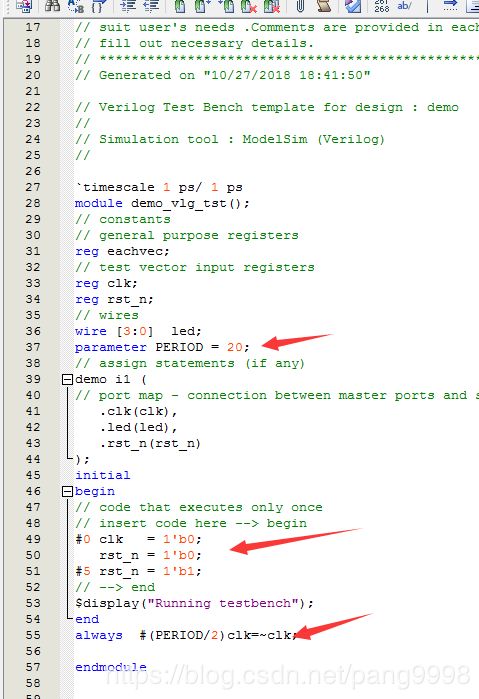

我们可以通过Quartus自动生成一个Testbench的模板,选择Processing -> Start -> Start Test Bench Template Writer,等待完成后打开刚才生成的Testbench,默认是保存在simulation\modelsim文件夹下的.vt格式文件

Quartus打开文件,到“工程目录\simulation\modelsim"下找到.vt文件,打开,

按照参考文献⑤的语法规则编写Testbench,填写完成后内容如下

// Copyright (C) 1991-2013 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details.

// *****************************************************************************

// This file contains a Verilog test bench template that is freely editable to

// suit user's needs .Comments are provided in each section to help the user

// fill out necessary details.

// *****************************************************************************

// Generated on "10/27/2018 18:41:50"

// Verilog Test Bench template for design : demo

//

// Simulation tool : ModelSim (Verilog)

//

`timescale 1 ps/ 1 ps

module demo_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg rst_n;

// wires

wire [3:0] led;

parameter PERIOD = 20;

// assign statements (if any)

demo i1 (

// port map - connection between master ports and signals/registers

.clk(clk),

.led(led),

.rst_n(rst_n)

);

initial

begin

// code that executes only once

// insert code here --> begin

#0 clk = 1'b0;

rst_n = 1'b0;

#5 rst_n = 1'b1;

// --> end

$display("Running testbench");

end

always #(PERIOD/2)clk=~clk;

endmodule

也就是对模板进行下面的修改,并保存

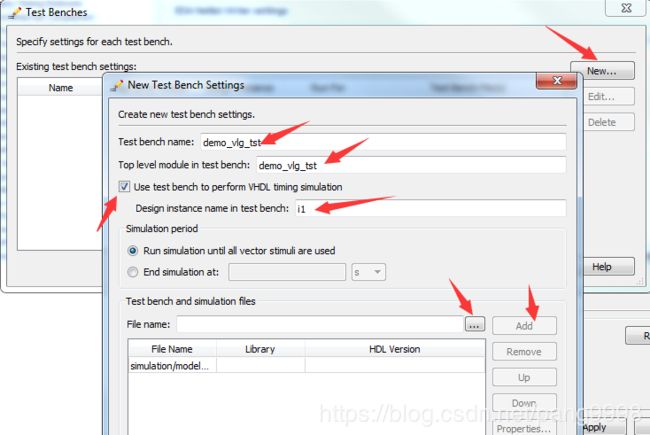

4)回到Quartus->Assignments->Settings->Simulation

点击Test Benches-》New,Test bench name粘贴刚才复制的名字,Top level module in test bench自动填充雍阳的名字,勾选Use test bench to perform VHDL timing simulation,填写i1,File name选择"工程目录\simulation\modelsim"下的.vt文件,最后点击Add,OK关闭对话框,至此,设置完成!!下面开始仿真。

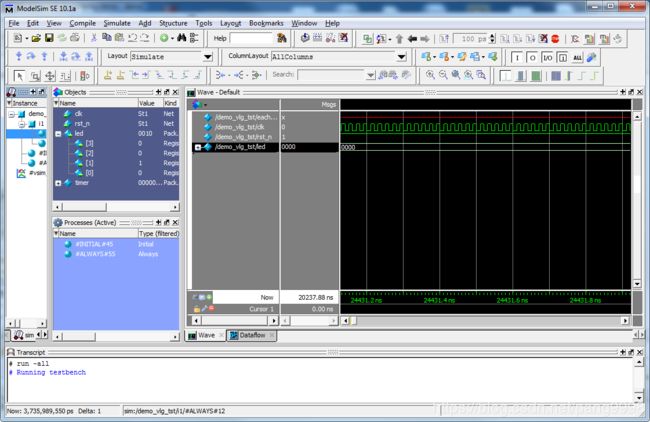

5)点击Tools -》Run Simulation tool-》RTL Simulation

漂亮的仿真界面出来啦~~~

FPGA开发环境 QuartusII+ModelSim SE配置完成!这个过程中可能会出现以下问题

①Error: Top-level design entity "simulate" is undefined

按照参考文献⑥,将模块名和.v文件名改为一致即可。