FPGA实验之串口发送

FPGA实验之串口发送

标准的串口数据格式包括:

l 起始位:是一个值位’0’的逻辑值

l 数据位:8位二进制数

l 校验位:1位,可以奇校验也可以是偶校验(也可以不加)。

l 停止位:一串数值发送结束的标志

波特率:单片机或计算机在串口通信时的速率。比如:9600bps表示每秒传输9600个二进制位。

数据传输顺序为:起始位(1位)+数据位(8位)+校验位(1位)+停止位(1位)

(1) 建立工程

(2) 编写程序

moduleUART_send(input CLK,RST,call_send,//使能发送信号 晶振50MHz

input[7:0]data,//需要发送的8为数据

output send_done,TXD);//发送完成的信号 TXD输出信号

//parameterBPS9600=13'd5208; //每位数据传输时间为t=1/9600 s,周期T=1/50000000,计数值为t/T=5208

parameter BPS115200=9'd434;//每位数据传输时间为t=1/115200 s,周期T=1/50000000,计数值为t/T=434

reg [31:0]C1,ii;

reg txd,odd_data;//odd_data为奇校验数据

reg isdone;

always @(posedgeCLK or negedge RST)

if(!RST)

begin C1<=32'd0;txd<=1'b1;ii<=0;isdone<=1'b0; end

else if(call_send)

case(ii)

0: if(C1==BPS115200)begin C1<=32'd0; ii<=ii+1; end //起始位

else beginC1<=C1+1'd1; txd<=1'b0; odd_data<=^~data; end //按位同或求奇校验,,,如果按位异或(even_data<=^data;)求偶校验

1,2,3,4,5,6,7,8:

if(C1==BPS115200)begin C1<=32'd0; ii<=ii+1; end //数据位

else beginC1<=C1+1'd1; txd<=data[ii-1]; end

9: if(C1==BPS115200)begin C1<=32'd0; ii<=ii+1; end //校验位

else beginC1<=C1+1'd1; txd<=odd_data; end

10:if(C1==BPS115200)begin C1<=32'd0; ii<=ii+1; end // 停止位

else beginC1<=C1+1'd1; txd<=1'b1; end

11:beginisdone<=1'b1; ii<=ii+1; end

12:beginisdone<=1'b0; ii<=0; end

endcase

assign TXD = txd;

assign send_done =isdone;

endmodule

以下是激励信号程序:

`timescale 1 ps/ 1ps

moduleUART_send_vlg_tst();

// constants

// general purposeregisters

reg eachvec;

// test vectorinput registers

reg CLK;

reg RST;

reg call_send;

reg [7:0] data;

reg [7:0] i;

// wires

wire TXD;

wire send_done;

// assignstatements (if any)

UART_send i1 (

// port map -connection between master ports and signals/registers

.CLK(CLK),

.RST(RST),

.TXD(TXD),

.call_send(call_send),

.data(data),

.send_done(send_done)

);

initial

begin

RST = 0; #10; RST = 1;

CLK = 0; forever #10 CLK = ~CLK;

end

always @(posedgeCLK or negedge RST)

if(!RST)

begin call_send<=1'b0;data<=0; i<=0;end

else

case(i)

0: if(send_done) begincall_send<=0; i<=i+1; end

else begincall_send<=1; data<=8'b10101010; end

1: if(send_done) begincall_send<=0; i<=i+1; end

else begincall_send<=1; data<=8'b01010101; end

2: if(send_done) begincall_send<=0; i<=i+1; end

else begincall_send<=1; data<=8'b10100101; end

3: i<=i;

endcase

endmodule

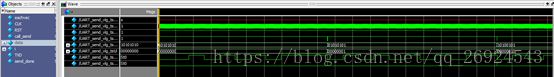

(3) ModelSim仿真

注:数据从低位开始发送