linux--多目录下的MakeFile文件(嵌套Makefile)编写

linux--多目录下的makefile文件(嵌套Makefile)编写

- 1 简介

- 2 规则

- 2.1 简介

- 2.1.1 Makefile 主要的 5个部分 (显示规则, 隐晦规则, 变量定义, 文件指示, 注释)

- 2.1.2 GNU make 的工作方式

- 2.2 Makefile 初级语法

- 2.2.1 Makefile 规则

- 2.2.1.1 规则语法

- 2.2.1.2 规则中的通配符

- 2.2.1.3 路径搜索

- 2.2.2 Makefile 中的变量

- 2.2.2.1 变量定义 ( = or := )

- 2.2.2.2 变量替换

- 2.2.2.3 变量追加值 +=

- 2.2.2.4 变量覆盖 override

- 2.2.2.5 目标变量

- 2.2.3 Makefile 命令前缀

- 2.2.4 伪目标

- 2.2.5 引用其他的 Makefile

- 2.2.6 查看C文件的依赖关系

- 2.2.7 make 退出码

- 2.2.8 指定 Makefile, 指定特定目标

- 2.2.9 make 参数介绍

- 2.2.10 Makefile 隐含规则

- 2.2.11 隐含规则中的 命令变量 和 命令参数变量

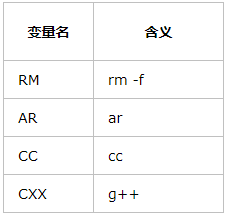

- 2.2.11.1 命令变量, 书写Makefile可以直接写 shell时用这些变量.

- 2.2.11.2 命令参数变量

- 2.2.12 自动变量

- 2.3. Makefile 高级语法

- 2.3.1 嵌套Makefile

- 2.3.2 定义命令包

- 2.3.3 条件判断

- 2.3.4 Makefile 中的函数

- 2.3.4.1 字符串函数

- 2.3.4.2 文件名函数

- 2.3.4.3 foreach

- 2.3.4.4 if

- 2.3.4.5 call - 创建新的参数化函数

- 2.3.4.6 origin - 判断变量的来源

- 2.3.4.7 shell

- 2.3.4.8 make 控制函数

- 2.3.5 Makefile中一些GNU约定俗成的伪目标

- 3 示例

- 3.1 文件根目录下的文件

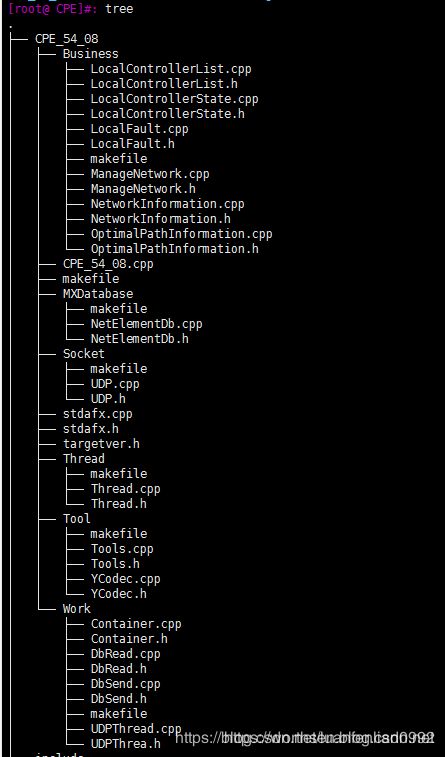

- 3.2 这个是工程中除了include,lib外的目录结构

- 3.3 根目录下的makefile文件

- 3.4 OBJ文件中的makefile

- 3.5 CPE_54_08文件目录下的makefile

- 3.6 Business文件下的makefile

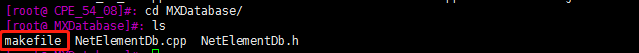

- 3.7 MXDatabase文件下的makefile

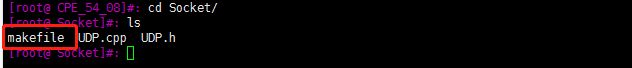

- 3.8 Socket文件下的makefile

- 3.9 Thread文件下的makefile

- 3.10 Tool文件下的makefile

- 3.11 Work文件下的makefile

- 3.12 最后成功生成可执行文件

- 参考

非原创,整理加了目录,为了后面方便查找

1 简介

- Makefile的核心

文件依赖关系是Makefile的核心!根据依赖关系,执行对应的命令,最后生成目标文件。 - 多目录下的MakeFile

出于功能模块复用,框架更清晰等考虑,MakeFile工程会将功能模块化,分到对应的目录,这就涉及多目录下MakeFile文件编写。

2 规则

2.1 简介

2.1.1 Makefile 主要的 5个部分 (显示规则, 隐晦规则, 变量定义, 文件指示, 注释)

- Makefile基本格式如下

target ... : prerequisites ...

command

...

...

target: - 目标文件, 可以是 Object File, 也可以是可执行文件

prerequisites: - 生成 target 所需要的文件或者目标

command: - make需要执行的命令 (任意的shell命令), Makefile中的命令必须以 [tab] 开头

- 显示规则 :: 说明如何生成一个或多个目标文件(包括 生成的文件, 文件的依赖文件, 生成的命令)

- 隐晦规则 :: make的自动推导功能所执行的规则

- 变量定义 :: Makefile中定义的变量

- 文件指示 :: Makefile中引用其他Makefile; 指定Makefile中有效部分; 定义一个多行命令

- 注释 :: Makefile只有行注释 “#”, 如果要使用或者输出"#"字符, 需要进行转义, “#”

2.1.2 GNU make 的工作方式

- 读入主Makefile (主Makefile中可以引用其他Makefile)

- 读入被include的其他Makefile

- 初始化文件中的变量

- 推导隐晦规则, 并分析所有规则

- 为所有的目标文件创建依赖关系链

- 根据依赖关系, 决定哪些目标要重新生成

- 执行生成命令

2.2 Makefile 初级语法

2.2.1 Makefile 规则

2.2.1.1 规则语法

规则主要有2部分: 依赖关系 和 生成目标的方法.

语法有以下2种:

target ... : prerequisites ...

command

...

target ... : prerequisites ; command

command

...

注: command太长, 可以用 \ 作为换行符

2.2.1.2 规则中的通配符

* :: 表示任意一个或多个字符

? :: 表示任意一个字符

[...] :: ex. [abcd] 表示a,b,c,d中任意一个字符, [^abcd]表示除a,b,c,d以外的字符,

[0-9]表示 0~9中任意一个数字

~ :: 表示用户的home目录

2.2.1.3 路径搜索

当一个Makefile中涉及到大量源文件时(这些源文件和Makefile极有可能不在同一个目录中),这时, 最好将源文件的路径明确在Makefile中, 便于编译时查找. Makefile中有个特殊的变量 VPATH 就是完成这个功能的.

指定了 VPATH 之后, 如果当前目录中没有找到相应文件或依赖的文件, Makefile 回到 VPATH 指定的路径中再去查找…

VPATH 使用方法:

vpath :: 当前目录中找不到文件时, 就从中搜索

vpath :: 符合格式的文件, 就从中搜索

vpath :: 清除符合格式的文件搜索路径

vpath :: 清除所有已经设置好的文件路径

vpath :: 当前目录中找不到文件时, 就从中搜索

vpath :: 符合格式的文件, 就从中搜索

vpath :: 清除符合格式的文件搜索路径

vpath :: 清除所有已经设置好的文件路径

2.2.2 Makefile 中的变量

2.2.2.1 变量定义 ( = or := )

OBJS = programA.o programB.o

OBJS-ADD = $(OBJS) programC.o

# 或者

OBJS := programA.o programB.o

OBJS-ADD := $(OBJS) programC.o

其中 = 和 := 的区别在于, := 只能使用前面定义好的变量, = 可以使用后面定义的变量

- 测试 =

# Makefile内容

OBJS2 = $(OBJS1) programC.o

OBJS1 = programA.o programB.o

all:

@echo $(OBJS2)

# bash中执行 make, 可以看出虽然 OBJS1 是在 OBJS2 之后定义的, 但在 OBJS2中可以提前使用

$ make

programA.o programB.o programC.o

- 测试 :=

# Makefile内容

OBJS2 := $(OBJS1) programC.o

OBJS1 := programA.o programB.o

all:

@echo $(OBJS2)

# bash中执行 make, 可以看出 OBJS2 中的 $(OBJS1) 为空

$ make

programC.o

2.2.2.2 变量替换

# Makefile内容

SRCS := programA.c programB.c programC.c

OBJS := $(SRCS:%.c=%.o)

all:

@echo "SRCS: " $(SRCS)

@echo "OBJS: " $(OBJS)

# bash中运行make

$ make

SRCS: programA.c programB.c programC.c

OBJS: programA.o programB.o programC.o

2.2.2.3 变量追加值 +=

# Makefile内容

SRCS := programA.c programB.c programC.c

SRCS += programD.c

all:

@echo "SRCS: " $(SRCS)

# bash中运行make

$ make

SRCS: programA.c programB.c programC.c programD.c

2.2.2.4 变量覆盖 override

作用是使 Makefile中定义的变量能够覆盖 make 命令参数中指定的变量

语法:

override =

override :=

override +=

- 下面通过一个例子体会 override 的作用

# Makefile内容 (没有用override)

SRCS := programA.c programB.c programC.c

all:

@echo "SRCS: " $(SRCS)

# bash中运行make

$ make SRCS=nothing

SRCS: nothing

#################################################

# Makefile内容 (用override)

override SRCS := programA.c programB.c programC.c

all:

@echo "SRCS: " $(SRCS)

# bash中运行make

$ make SRCS=nothing

SRCS: programA.c programB.c programC.c

2.2.2.5 目标变量

作用是使变量的作用域仅限于这个目标(target), 而不像之前例子中定义的变量, 对整个Makefile都有效.

语法:

示例

# Makefile 内容

SRCS := programA.c programB.c programC.c

target1: TARGET1-SRCS := programD.c

target1:

@echo "SRCS: " $(SRCS)

@echo "SRCS: " $(TARGET1-SRCS)

target2:

@echo "SRCS: " $(SRCS)

@echo "SRCS: " $(TARGET1-SRCS)

# bash中执行make

$ make target1

SRCS: programA.c programB.c programC.c

SRCS: programD.c

$ make target2 <-- target2中显示不了 $(TARGET1-SRCS)

SRCS: programA.c programB.c programC.c

SRCS:

2.2.3 Makefile 命令前缀

Makefile 中书写shell命令时可以加2种前缀 @ 和 -, 或者不用前缀.

3种格式的shell命令区别如下:

- 不用前缀 :: 输出执行的命令以及命令执行的结果, 出错的话停止执行

- 前缀 @ :: 只输出命令执行的结果, 出错的话停止执行

- 前缀 - :: 命令执行有错的话, 忽略错误, 继续执行

示例:

# Makefile 内容 (不用前缀)

all:

echo "没有前缀"

cat this_file_not_exist

echo "错误之后的命令" <-- 这条命令不会被执行

# bash中执行 make

$ make

echo "没有前缀" <-- 命令本身显示出来

没有前缀 <-- 命令执行结果显示出来

cat this_file_not_exist

cat: this_file_not_exist: No such file or directory

make: *** [all] Error 1

###########################################################

# Makefile 内容 (前缀 @)

all:

@echo "没有前缀"

@cat this_file_not_exist

@echo "错误之后的命令" <-- 这条命令不会被执行

# bash中执行 make

$ make

没有前缀 <-- 只有命令执行的结果, 不显示命令本身

cat: this_file_not_exist: No such file or directory

make: *** [all] Error 1

###########################################################

# Makefile 内容 (前缀 -)

all:

-echo "没有前缀"

-cat this_file_not_exist

-echo "错误之后的命令" <-- 这条命令会被执行

# bash中执行 make

$ make

echo "没有前缀" <-- 命令本身显示出来

没有前缀 <-- 命令执行结果显示出来

cat this_file_not_exist

cat: this_file_not_exist: No such file or directory

make: [all] Error 1 (ignored)

echo "错误之后的命令" <-- 出错之后的命令也会显示

错误之后的命令 <-- 出错之后的命令也会执行

2.2.4 伪目标

伪目标并不是一个"目标(target)", 不像真正的目标那样会生成一个目标文件.

典型的伪目标是 Makefile 中用来清理编译过程中中间文件的 clean 伪目标, 一般格式如下:

.PHONY: clean <-- 这句没有也行, 但是最好加上

clean:

-rm -f *.o

2.2.5 引用其他的 Makefile

语法: include (filename 可以包含通配符和路径)

- 示例

# Makefile 内容

all:

@echo "主 Makefile begin"

@make other-all

@echo "主 Makefile end"

include ./other/Makefile

# ./other/Makefile 内容

other-all:

@echo "other makefile begin"

@echo "other makefile end"

# bash中执行 make

$ ll

total 20K

-rw-r--r-- 1 wangyubin wangyubin 125 Sep 23 16:13 Makefile

-rw-r--r-- 1 wangyubin wangyubin 11K Sep 23 16:15 makefile.org <-- 这个文件不用管

drwxr-xr-x 2 wangyubin wangyubin 4.0K Sep 23 16:11 other

$ ll other/

total 4.0K

-rw-r--r-- 1 wangyubin wangyubin 71 Sep 23 16:11 Makefile

$ make

主 Makefile begin

make[1]: Entering directory `/path/to/test/makefile'

other makefile begin

other makefile end

make[1]: Leaving directory `/path/to/test/makefile'

主 Makefile end

2.2.6 查看C文件的依赖关系

写 Makefile 的时候, 需要确定每个目标的依赖关系.

GNU提供一个机制可以查看C代码文件依赖那些文件, 这样我们在写 Makefile 目标的时候就不用打开C源码来看其依赖那些文件了.

比如, 下面命令显示内核源码中 virt/kvm/kvm_main.c 中的依赖关系

$ cd virt/kvm/

$ gcc -MM kvm_main.c

kvm_main.o: kvm_main.c iodev.h coalesced_mmio.h async_pf.h <-- 这句就可以加到 Makefile 中作为编译 kvm_main.o 的依赖关系

2.2.7 make 退出码

Makefile的退出码有以下3种:

- 0 :: 表示成功执行

- 1 :: 表示make命令出现了错误

- 2 :: 使用了 “-q” 选项, 并且make使得一些目标不需要更新

2.2.8 指定 Makefile, 指定特定目标

默认执行 make 命令时, GNU make在当前目录下依次搜索下面3个文件 “GNUmakefile”, “makefile”, “Makefile”,

找到对应文件之后, 就开始执行此文件中的第一个目标(target). 如果找不到这3个文件就报错.

非默认情况下, 可以在 make 命令中指定特定的 Makefile 和特定的 目标.

- 示例

# Makefile文件名改为 MyMake, 内容

target1:

@echo "target [1] begin"

@echo "target [1] end"

target2:

@echo "target [2] begin"

@echo "target [2] end"

# bash 中执行 make

$ ls

Makefile

$ mv Makefile MyMake

$ ls

MyMake

$ make <-- 找不到默认的 Makefile

make: *** No targets specified and no makefile found. Stop.

$ make -f MyMake <-- 指定特定的Makefile

target [1] begin

target [1] end

$ make -f MyMake target2 <-- 指定特定的目标(target)

target [2] begin

target [2] end

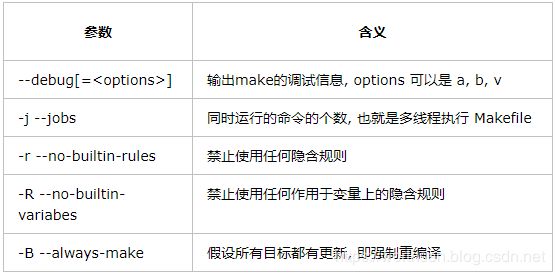

2.2.9 make 参数介绍

make 的参数有很多, 可以通过 make -h 去查看, 下面只介绍几个我认为比较有用的.

2.2.10 Makefile 隐含规则

这里只列一个和编译C相关的.

编译C时,.o 的目标会自动推导为 .c

# Makefile 中

main : main.o

gcc -o main main.o

#会自动变为:

main : main.o

gcc -o main main.o

main.o: main.c <-- main.o 这个目标是隐含生成的

gcc -c main.c

2.2.11 隐含规则中的 命令变量 和 命令参数变量

2.2.11.1 命令变量, 书写Makefile可以直接写 shell时用这些变量.

- 示例

# Makefile 内容

all:

@echo $(RM)

@echo $(AR)

@echo $(CC)

@echo $(CXX)

# bash 中执行make, 显示各个变量的值

$ make

rm -f

ar

cc

g++

2.2.11.2 命令参数变量

# test.c 内容

#include

int main(int argc, char *argv[])

{

printf ("Hello Makefile\n");

return 0;

}

# Makefile 内容

test: test.o

$(CC) -o test test.o

# bash 中用 make 来测试

$ ll

total 24K

-rw-r--r-- 1 wangyubin wangyubin 69 Sep 23 17:31 Makefile

-rw-r--r-- 1 wangyubin wangyubin 14K Sep 23 19:51 makefile.org <-- 请忽略这个文件

-rw-r--r-- 1 wangyubin wangyubin 392 Sep 23 17:31 test.c

$ make

cc -c -o test.o test.c

cc -o test test.o <-- 这个是自动推导的

$ rm -f test test.o

$ make CFLAGS=-Wall <-- 命令中加的编译器参数自动追加入下面的编译中了

cc -Wall -c -o test.o test.c

cc -o test test.o

2.2.12 自动变量

Makefile 中很多时候通过自动变量来简化书写, 各个自动变量的含义如下

2.3. Makefile 高级语法

2.3.1 嵌套Makefile

在 Makefile 初级语法中已经提到过引用其它 Makefile的方法. 这里有另一种写法, 并且可以向引用的其它 Makefile 传递参数.

示例: (不传递参数, 只是调用子文件夹 other 中的Makefile)

# Makefile 内容

all:

@echo "主 Makefile begin"

@cd ./other && make

@echo "主 Makefile end"

# ./other/Makefile 内容

other-all:

@echo "other makefile begin"

@echo "other makefile end"

# bash中执行 make

$ ll

total 28K

-rw-r--r-- 1 wangyubin wangyubin 104 Sep 23 20:43 Makefile

-rw-r--r-- 1 wangyubin wangyubin 17K Sep 23 20:44 makefile.org <-- 这个文件不用管

drwxr-xr-x 2 wangyubin wangyubin 4.0K Sep 23 20:42 other

$ ll other/

total 4.0K

-rw-r--r-- 1 wangyubin wangyubin 71 Sep 23 16:11 Makefile

$ make

主 Makefile begin

make[1]: Entering directory `/path/to/test/makefile/other'

other makefile begin

other makefile end

make[1]: Leaving directory `/path/to/test/makefile/other'

主 Makefile end

示例: (用export传递参数)

# Makefile 内容

export VALUE1 := export.c <-- 用了 export, 此变量能够传递到 ./other/Makefile 中

VALUE2 := no-export.c <-- 此变量不能传递到 ./other/Makefile 中

all:

@echo "主 Makefile begin"

@cd ./other && make

@echo "主 Makefile end"

# ./other/Makefile 内容

other-all:

@echo "other makefile begin"

@echo "VALUE1: " $(VALUE1)

@echo "VALUE2: " $(VALUE2)

@echo "other makefile end"

# bash中执行 make

$ make

主 Makefile begin

make[1]: Entering directory `/path/to/test/makefile/other'

other makefile begin

VALUE1: export.c <-- VALUE1 传递成功

VALUE2: <-- VALUE2 传递失败

other makefile end

make[1]: Leaving directory `/path/to/test/makefile/other'

主 Makefile end

补充 export 语法格式如下:

export variable = value

export variable := value

export variable += value

2.3.2 定义命令包

命令包有点像是个函数, 将连续的相同的命令合成一条, 减少 Makefile 中的代码量, 便于以后维护.

- 语法

define

command

...

endef

- 示例

# Makefile 内容

define run-hello-makefile

@echo -n "Hello"

@echo " Makefile!"

@echo "这里可以执行多条 Shell 命令!"

endef

all:

$(run-hello-makefile)

# bash 中运行make

$ make

Hello Makefile!

这里可以执行多条 Shell 命令!

2.3.3 条件判断

条件判断的关键字主要有 ifeq ifneq ifdef ifndef

- 语法

endif

# 或者

else

endif

- 示例: ifeq的例子, ifneq和ifeq的使用方法类似, 就是取反

# Makefile 内容

all:

ifeq ("aa", "bb")

@echo "equal"

else

@echo "not equal"

endif

# bash 中执行 make

$ make

not equal

- 示例: ifdef的例子, ifndef和ifdef的使用方法类似, 就是取反

# Makefile 内容

SRCS := program.c

all:

ifdef SRCS

@echo $(SRCS)

else

@echo "no SRCS"

endif

# bash 中执行 make

$ make

program.c

2.3.4 Makefile 中的函数

Makefile 中自带了一些函数, 利用这些函数可以简化 Makefile 的编写.

函数调用语法如下

$( )

# 或者

${ }

是函数名

是函数参数

2.3.4.1 字符串函数

字符串替换函数: $(subst ,, )

功能: 把字符串 中的 替换为

返回: 替换过的字符串

# Makefile 内容

all:

@echo $(subst t,e,maktfilt) <-- 将t替换为e

# bash 中执行 make

$ make

makefile

模式字符串替换函数: $(patsubst ,, )

功能: 查找 中的单词(单词以"空格", “tab”, "换行"来分割) 是否符合 , 符合的话, 用 替代.

返回: 替换过的字符串

# Makefile 内容

all:

@echo $(patsubst %.c,%.o,programA.c programB.c)

# bash 中执行 make

$ make

programA.o programB.o

去空格函数: $(strip )

功能: 去掉 字符串中开头和结尾的空字符

返回: 被去掉空格的字符串值

# Makefile 内容

VAL := " aa bb cc "

all:

@echo "去除空格前: " $(VAL)

@echo "去除空格后: " $(strip $(VAL))

# bash 中执行 make

$ make

去除空格前: aa bb cc

去除空格后: aa bb cc

查找字符串函数: $(findstring ,)

功能: 在字符串 中查找 字符串

返回: 如果找到, 返回 字符串, 否则返回空字符串

# Makefile 内容

VAL := " aa bb cc "

all:

@echo $(findstring aa,$(VAL))

@echo $(findstring ab,$(VAL))

# bash 中执行 make

$ make

aa

过滤函数: $(filter

功能: 以 模式过滤字符串 , 保留 符合模式 的单词, 可以有多个模式

返回: 符合模式 的字符串

# Makefile 内容

all:

@echo $(filter %.o %.a,program.c program.o program.a)

# bash 中执行 make

$ make

program.o program.a

反过滤函数: $(filter-out

功能: 以 模式过滤字符串 , 去除 符合模式 的单词, 可以有多个模式

返回: 不符合模式 的字符串

# Makefile 内容

all:

@echo $(filter-out %.o %.a,program.c program.o program.a)

# bash 中执行 make

$ make

program.c

排序函数: $(sort )

功能: 给字符串 中的单词排序 (升序)

返回: 排序后的字符串

# Makefile 内容

all:

@echo $(sort bac abc acb cab)

# bash 中执行 make

$ make

abc acb bac cab

取单词函数: $(word , )

功能: 取字符串 中的 第个单词 (n从1开始)

返回: 中的第个单词, 如果 比 中单词个数要大, 则返回空字符串

# Makefile 内容

all:

@echo $(word 1,aa bb cc dd)

@echo $(word 5,aa bb cc dd)

@echo $(word 4,aa bb cc dd)

# bash 中执行 make

$ make

aa

dd

取单词串函数: $(wordlist ,, )

功能: 从字符串 中取从 开始到的单词串. 和是一个数字.

返回: 从到的字符串

# Makefile 内容

all:

@echo $(wordlist 1,3,aa bb cc dd)

@echo $(word 5,6,aa bb cc dd)

@echo $(word 2,5,aa bb cc dd)

# bash 中执行 make

$ make

aa bb cc

bb

单词个数统计函数: $(words )

功能: 统计字符串 中单词的个数

返回: 单词个数

# Makefile 内容

all:

@echo $(words aa bb cc dd)

@echo $(words aabbccdd)

@echo $(words )

# bash 中执行 make

$ make

1

首单词函数: $(firstword )

功能: 取字符串 中的第一个单词

返回: 字符串 中的第一个单词

# Makefile 内容

all:

@echo $(firstword aa bb cc dd)

@echo $(firstword aabbccdd)

@echo $(firstword )

# bash 中执行 make

$ make

aa

aabbccdd

2.3.4.2 文件名函数

取目录函数: $(dir

功能: 从文件名序列 中取出目录部分

返回: 文件名序列 中的目录部分

# Makefile 内容

all:

@echo $(dir /home/a.c ./bb.c ../c.c d.c)

# bash 中执行 make

$ make

/home/ ./ ../ ./

取文件函数: $(notdir

功能: 从文件名序列 中取出非目录部分

返回: 文件名序列 中的非目录部分

# Makefile 内容

all:

@echo $(notdir /home/a.c ./bb.c ../c.c d.c)

# bash 中执行 make

$ make

a.c bb.c c.c d.c

取后缀函数: $(suffix

功能: 从文件名序列 中取出各个文件名的后缀

返回: 文件名序列 中各个文件名的后缀, 没有后缀则返回空字符串

# Makefile 内容

all:

@echo $(suffix /home/a.c ./b.o ../c.a d)

# bash 中执行 make

$ make

.c .o .a

取前缀函数: $(basename

功能: 从文件名序列 中取出各个文件名的前缀

返回: 文件名序列 中各个文件名的前缀, 没有前缀则返回空字符串

# Makefile 内容

all:

@echo $(basename /home/a.c ./b.o ../c.a /home/.d .e)

# bash 中执行 make

$ make

/home/a ./b ../c /home/

加后缀函数: $(addsuffix ,

功能: 把后缀 加到 中的每个单词后面

返回: 加过后缀的文件名序列

# Makefile 内容

all:

@echo $(addsuffix .c,/home/a b ./c.o ../d.c)

# bash 中执行 make

$ make

/home/a.c b.c ./c.o.c ../d.c.c

加前缀函数: $(addprefix ,

功能: 把前缀 加到 中的每个单词前面

返回: 加过前缀的文件名序列

# Makefile 内容

all:

@echo $(addprefix test_,/home/a.c b.c ./d.c)

# bash 中执行 make

$ make

test_/home/a.c test_b.c test_./d.c

连接函数: $(join ,)

功能: 中对应的单词加到 后面

返回: 连接后的字符串

# Makefile 内容

all:

@echo $(join a b c d,1 2 3 4)

@echo $(join a b c d,1 2 3 4 5)

@echo $(join a b c d e,1 2 3 4)

# bash 中执行 make

$ make

a1 b2 c3 d4

a1 b2 c3 d4 5

a1 b2 c3 d4 e

2.3.4.3 foreach

- 语法

$(foreach ,, ) - 示例

# Makefile 内容

targets := a b c d

objects := $(foreach i,$(targets),$(i).o)

all:

@echo $(targets)

@echo $(objects)

# bash 中执行 make

$ make

a b c d

a.o b.o c.o d.o

2.3.4.4 if

这里的if是个函数, 和前面的条件判断不一样, 前面的条件判断属于Makefile的关键字

- 语法

$(if ,)

$(if ,,) - 示例

# Makefile 内容

val := a

objects := $(if $(val),$(val).o,nothing)

no-objects := $(if $(no-val),$(val).o,nothing)

all:

@echo $(objects)

@echo $(no-objects)

# bash 中执行 make

$ make

a.o

nothing

2.3.4.5 call - 创建新的参数化函数

- 语法

$(call ,,,…) - 示例

# Makefile 内容

log = "====debug====" $(1) "====end===="

all:

@echo $(call log,"正在 Make")

# bash 中执行 make

$ make

====debug==== 正在 Make ====end====

2.3.4.6 origin - 判断变量的来源

# Makefile 内容

val-in-file := test-file

override val-override := test-override

all:

@echo $(origin not-define) # not-define 没有定义

@echo $(origin CC) # CC 是Makefile默认定义的变量

@echo $(origin PATH) # PATH 是 bash 环境变量

@echo $(origin val-in-file) # 此Makefile中定义的变量

@echo $(origin val-in-cmd) # 这个变量会加在 make 的参数中

@echo $(origin val-override) # 此Makefile中定义的override变量

@echo $(origin @) # 自动变量, 具体前面的介绍

# bash 中执行 make

$ make val-in-cmd=val-cmd

undefined

default

environment

file

command line

override

automatic

2.3.4.7 shell

- 语法

$(shell )

它的作用就是执行一个shell命令, 并将shell命令的结果作为函数的返回.

作用和

2.3.4.8 make 控制函数

产生一个致命错误: $(error

功能: 输出错误信息, 停止Makefile的运行

# Makefile 内容

all:

$(error there is an error!)

@echo "这里不会执行!"

# bash 中执行 make

$ make

Makefile:2: *** there is an error!. Stop.

输出警告: $(warning

功能: 输出警告信息, Makefile继续运行

# Makefile 内容

all:

$(warning there is an warning!)

@echo "这里会执行!"

# bash 中执行 make

$ make

Makefile:2: there is an warning!

这里会执行!

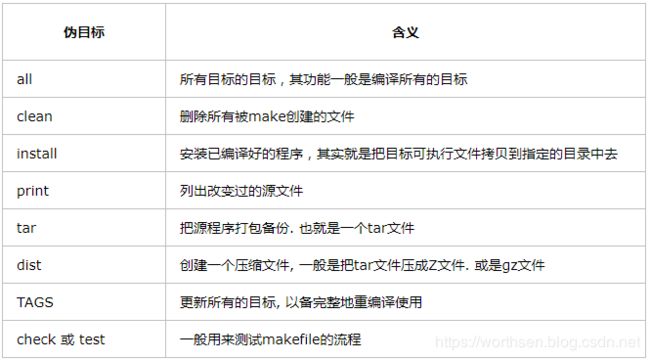

2.3.5 Makefile中一些GNU约定俗成的伪目标

如果有过在Linux上, 从源码安装软件的经历的话, 就会对 make clean, make install 比较熟悉.

像 clean, install 这些伪目标, 广为人知, 不用解释就大家知道是什么意思了.

下面列举一些常用的伪目标, 如果在自己项目的Makefile合理使用这些伪目标的话, 可以让我们自己的Makefile看起来更专业, 呵呵

3 示例

3.1 文件根目录下的文件

![]()

include文件夹里面包含的是工程所需的一些头文件,lib库包含的是工程所需的一些库文件,这两个无需makefile文件,直接在其他的makefile中有检索这两个文件夹的操作。

3.2 这个是工程中除了include,lib外的目录结构

3.3 根目录下的makefile文件

#定义编译器

CC = g++

OUT_PUT := cpe_54_08

#将所有的.o文件都编译到OBJ文件夹下

OBJ :=cpe_54_08.o business.o mxdatabase.o socket.o thread.o tool.o work.o

#根目录

TOP_DIR := $(PWD)

OBJ_DIR := $(TOP_DIR)/obj

BIN_DIR := $(TOP_DIR)/CPE_54_08

SRC_BUSINESS_DIR := $(BIN_DIR )/Business

SRC_MXDATABASE_DIR := $(BIN_DIR )/MxDatabase

SRC_SOCKET_DIR := $(BIN_DIR )/Socket

SRC_THREAD_DIR := $(BIN_DIR )/Thread

SRC_TOOL_DIR := $(BIN_DIR )/Tool

SRC_WORK_DIR := $(BIN_DIR )/Work

SUB_DIR := CPE_54_08\

CPE_54_08/Business\

CPE_54_08/MXDatabase\

CPE_54_08/Socket\

CPE_54_08/Thread\

CPE_54_08/Tool\

CPE_54_08/Work

LIB_PATH := $(TOP_DIR)/lib

LINK_LIB := -L$(LIB_PATH) -lbsapi -L$(LIB_PATH) -lMxHandlePool -L$(LIB_PATH) -lServerData -L$(LIB_PATH) -lmxcomlib -L$(LIB_PATH) -lmxdbvar -L$(LIB_PATH) -lchen -luuid

export CC OBJ TOP_DIR OBJ_DIR BIN_DIR SRC_BUSINESS_DIR SRC_MXDATABASE_DIR\

SRC_SOCKET_DIR SRC_THREAD_DIR SRC_TOOL_DIR SRC_WORK_DIR

all:$(SUB_DIR) $(OUT_PUT)

$(SUB_DIR):ECHO

make -C $@

ECHO:

@echo $(SUB_DIR)

@echo begin compile

$(OUT_PUT):$(OBJ_DIR)/cpe_54_08.o $(OBJ_DIR)/dbsend.o $(OBJ_DIR)/localcontrollerstate.o $(OBJ_DIR)/mxdatabase.o $(OBJ_DIR)/optimalpathinformation.o $(OBJ_DIR)/stdafx.o $(OBJ_DIR)/tool.o\

$(OBJ_DIR)/localfault.o $(OBJ_DIR)/localcontrollerlist.o $(OBJ_DIR)/dbread.o $(OBJ_DIR)/container.o $(OBJ_DIR)/networkinformation.o $(OBJ_DIR)/managenetwork.o $(OBJ_DIR)/ycodec.o\

$(OBJ_DIR)/thread.o $(OBJ_DIR)/socket.o

g++ -o $(OUT_PUT) $(OBJ_DIR)/cpe_54_08.o $(OBJ_DIR)/dbsend.o $(OBJ_DIR)/localcontrollerstate.o $(OBJ_DIR)/mxdatabase.o $(OBJ_DIR)/optimalpathinformation.o $(OBJ_DIR)/stdafx.o $(OBJ_DIR)/tool.o\

$(OBJ_DIR)/localfault.o $(OBJ_DIR)/localcontrollerlist.o $(OBJ_DIR)/dbread.o $(OBJ_DIR)/container.o $(OBJ_DIR)/networkinformation.o $(OBJ_DIR)/managenetwork.o $(OBJ_DIR)/ycodec.o $(OBJ_DIR)/thread.o\

$(OBJ_DIR)/socket.o $(LINK_LIB) -lpthread

clean:

rm -rf $(OBJ_DIR)/*.o $(OUT_PUT)

3.4 OBJ文件中的makefile

将工程中的所有cpp文件编译出来的 .o 文件都放在这个文件夹下

![]()

$(BIN_DIR)/$(BIN):$(OBJ)

$(CC) $^ -o $@

3.5 CPE_54_08文件目录下的makefile

INCLUDE_DIR := ../include ../

DIR := -I$(INCLUDE_DIR)

all:$(OBJ_DIR)/cpe_54_08.o $(OBJ_DIR)/stdafx.o

$(OBJ_DIR)/cpe_54_08.o:CPE_54_08.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

$(OBJ_DIR)/stdafx.o:stdafx.cpp

$(CC) -c $< $(DIR) -o $@

3.6 Business文件下的makefile

INCLUDE_DIR := ../../inlcude ../Business

DIR = -I$(INCLUDE_DIR)

all:$(OBJ_DIR)/localcontrollerlist.o $(OBJ_DIR)/localcontrollerstate.o $(OBJ_DIR)/localfault.o $(OBJ_DIR)/managenetwork.o $(OBJ_DIR)/networkinformation.o $(OBJ_DIR)/optimalpathinformation.o

$(OBJ_DIR)/localcontrollerlist.o:LocalControllerList.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

$(OBJ_DIR)/localcontrollerstate.o:LocalControllerState.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

$(OBJ_DIR)/localfault.o:LocalFault.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

$(OBJ_DIR)/managenetwork.o:ManageNetwork.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

$(OBJ_DIR)/networkinformation.o:NetworkInformation.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

$(OBJ_DIR)/optimalpathinformation.o:OptimalPathInformation.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

3.7 MXDatabase文件下的makefile

INCLUDE_DIR := ../MXDatabase ../../include

DIR := -I$(INCLUDE_DIR)

all:$(OBJ_DIR)/mxdatabase.o

$(OBJ_DIR)/mxdatabase.o:NetElementDb.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

3.8 Socket文件下的makefile

INCLUDE_DIR := ../../include ../

DIR := -I$(INCLUDE_DIR)

all:$(OBJ_DIR)/socket.o

$(OBJ_DIR)/socket.o:UDP.cpp

$(CC) -c $< $(DIR) -o $@

3.9 Thread文件下的makefile

INCLUDE_DIR := ../../include ../

DIR := -I$(INCLUDE_DIR)

all:$(OBJ_DIR)/thread.o

$(OBJ_DIR)/thread.o:Thread.cpp

$(CC) -c $< $(DIR) -o $@

3.10 Tool文件下的makefile

INCLUDE_DIR := ../../include ../

DIR := -I$(INCLUDE_DIR)

all:$(OBJ_DIR)/tool.o $(OBJ_DIR)/ycodec.o

$(OBJ_DIR)/tool.o:Tools.cpp

$(CC) -c $< $(DIR) -o $@

$(OBJ_DIR)/ycodec.o:YCodec.cpp

$(CC) -c $< $(DIR) -o $@

3.11 Work文件下的makefile

![]()

INCLUDE_DIR := ../../include ../

DIR := -I$(INCLUDE_DIR)

all:$(OBJ_DIR)/container.o $(OBJ_DIR)/dbsend.o $(OBJ_DIR)/dbread.o

$(OBJ_DIR)/container.o:Container.cpp

$(CC) -c $< $(DIR) -o $@

$(OBJ_DIR)/dbread.o:DbRead.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

$(OBJ_DIR)/dbsend.o:DbSend.cpp

$(CC) -c $< $(DIR) -o $@ -std=c++0x

3.12 最后成功生成可执行文件

参考

1、linux–Makefile概述

2、多目录下的makefile文件编写

3、Linux下Makefile的学习笔记以及多级目录下Makefile的编写

4、Makefile 使用总结

5、《Makefile》 作者 陈皓,整理 祝冬华