Zero operand per instruction: 0-address architecture

Operands must be implicit. That is, the location of the operands is already known. A 0-address architecture is also called a stack architecture because operands are kept on a run-time stack.

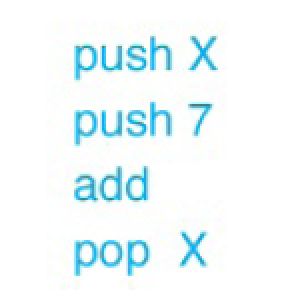

For example, an add instruction takes two values from the top of the stack, adds them together, and places the result back on the stack.

An example of instructions used on stack computer to add seven to a variable X.

One operand per instruction: a 1-address design

In essence, a 1-address design relies on an implicit operand for each instruction: a special register known as an accumulator. One operand is in the instruction and the processor uses the value of the accumulator as a second operand. Once the operation has been performed, the processor places the result back in the accumulator. We think of an instruction as operating on the value in the accumulator.

A programmer can load a constant or the value from a memory location into the accumulator or store the current value of the accumulator into a memory location.

The limitation of 1-address architecture: consider copying a value from one memory location to another. A 1-address design requires two instructions that load the value into the accumulator and then store the value in the new location. The design is especially inefficient for a system that moves graphics objects in display memory.

Constant

Although the operand field is small, having an explicit constant is important because programs use small constants frequently (e.g., to increment a loop index by 1); encoding a constant in the instruction is

faster and requires fewer registers.

We use the term immediate value to refer to an operand that is a constant. Some architectures interpret immediate values as signed, some interpret them as unsigned, and others allow a programmer to specify whether the value is signed or unsigned.

The Von Neumann bottleneck

On a computer that follows the Von Neumann Architecture, the time spent accessing memory can limit the overall performance. Architects use the term Von Neumann bottleneck to characterize the situation, and avoid the bottleneck by choosing designs in which operands are found in registers.

Implicit operand encoding

The opcode specifies the types of operands. The chief disadvantage of implicit encoding is apparent : multiple opcodes are needed for a given operation. If the processor uses many types of operands, the set of opcodes can be extremely large.

Explicit operand encoding

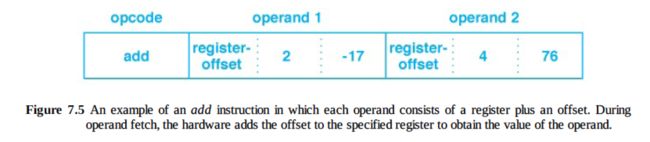

As the figure shows, the operand field is divided into two subfields: one specifies the type of the operand and the other specifies a value.

Operands That combines multiple values

One approach is known as a register-offset mechanism.

In the figure, the first operand specifies the contents of register 2 minus the constant 17, and the second operand specifies the contents of register 4 plus the constant 76.

Tradeoffs In The Choice Of Operands

Ease Of Programming. Complex forms of operands make programming easier.

Fewer Instructions. Increasing the expressive power of operands reduces the number of instructions in a program.

Smaller Instruction Size. Limiting the number of operands, the set of operands types, or the maximum size of an operand keeps each instruction small because fewer bits are needed to identify the operand type or represent an operand value.

Larger Range Of Immediate Values. Increasing the range of immediate values results in larger instructions.

Faster Operand Fetch And Decode. Limiting the number of operands and the possible types of each operand allows hardware to operate faster.

Decreased Hardware Size And Complexity. Limiting the types and complexity of operands reduces the size of the circuitry required.

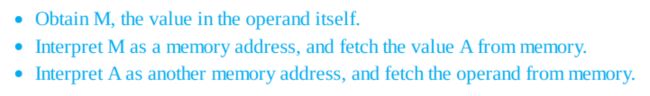

indirection

double indirection