CPU中常见寄存器及与内存的交互

本篇博客关于指令集和PSW的内容参考至:https://www.cnblogs.com/f-ck-need-u/p/11141636.html,同时做下了寄存器与内存交互的总结。

指令集

对于每个CPU,其都有一套自己可以执行的专门的指令集(这部分指令由CPU提供)。

正是因为不同CPU架构的指令集不同,使得X86处理器不能执行ARM程序,ARM程序也不能执行X86程序(Inter和AMD都使用x86指令集,手机绝大多数使用ARM指令集)。

注意:指令集具有软硬件层次之分:硬件指令集是硬件层次上由CPU自身提供的可执行的指令集合。软件指令集是指语言程序库所提供的指令,只要安装了该语言的程序库,指令就可以执行。

寄存器

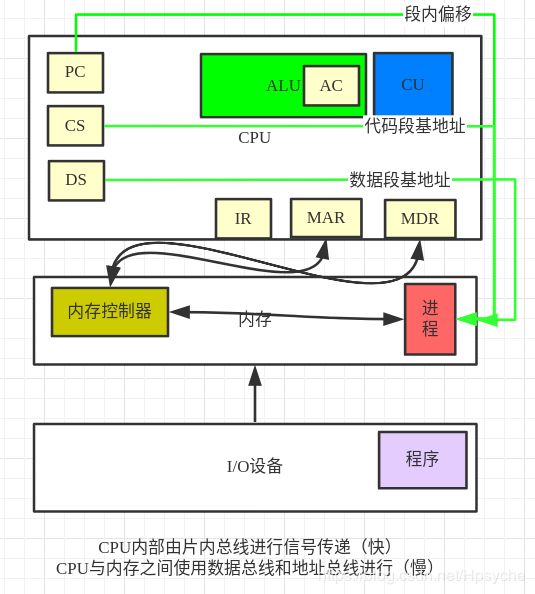

当程序要执行的部分被装载到内存中后,CPU要从内存中取出指令,然后指令解码(以便知道类型和操作数,简单的理解为:CPU要知道这是什么指令),然后执行该指令。再然后取下一个指令,重复以上操作。

由于CPU访问内存已得到指令或数据的时间要比执行指令花费的时间多得多,因此在CPU内部提供了一些来保存关键变量、临时数据等信息的通用寄存器。

所以,CPU需要提供一些特定的指令,使得可以从内存中读取数据存入寄存器以及将寄存器数据存入内存。

常见寄存器

IP寄存器:用来指向当前执行指令的下一条指令(非Inter厂家将IP寄存器称为PC寄存器:即程序计数器),指令取出后,就会更新该寄存器指向下一条指令;

CS寄存器:代码段寄存器,一般用于存放代码;

通常CS和IP配合使用,用于处理下一条执行的代码。

DS寄存器:数据段寄存器,一般用于存放数据;

- 一段内存定义为一个段,用一个段地址指示段,用偏移地址访问段内的单元;

- 用一个段存放数据,将它定义为“数据段”。用一段存放代码,将它定义为“代码段”,用一段当做栈,将它定义为“栈段”。

- 对于数据段,将它的段地址放到DS中,用mov、add、sub等访问内存单元的指令时,CPU就将我们定义的数据段中的内容当做数据来访问。对于代码段,将它的段地址放在CS中,将段中第一条指令的偏移地址放在IP中,这样CPU就将执行我们定义的的代码段中的指令。

- CPU将内存中的某段内容当做代码,是因为CS:IP指向哪里。

存储寄存器

MAR:保存将要被访问数据在内存中哪个地址,保存的是地址值

MDR:保存从内存读取进来的数据或将要被写入内存的数据,保存的是数据值

IR:保存当前正在执行的指令

- 存储器地址寄存器(MAR)和存储器数据寄存器(MDR)是主存和CPU之间的接口。MAR可以接收由程序计数器(PC)的指令地址或来自运算器的操作数的地址,以确定要访问的单元。MDR是向主存写入数据或从主存读出数据的缓冲部件。MAR和MDR从功能上看属于主存,但通常放在CPU内。

AC寄存器:累加寄存器,当运算器的算术逻辑单元(ALU)执行算术或逻辑运算时,为ALU提供一个工作区。累加寄存器暂时存放ALU运算的结果信息。

- ALU:算数逻辑单元,CPU中的关键部件,用来实现指令所指定的各种算术和逻辑运算操作。

- CU:控制器,负责将存储器中的数据送到ALU中去做运算,并将运算结果存回到存储器中

跟着上图,以取数相加指令为例:

取指:首先指令地址在PC中,通过片内总线然后送到MAR寄存器中,MAR通过与内存管理器交互,将MAR指令下那条地址的指令取出来放到MDR寄存器中。接着送到IR寄存器(IR:存储当前指令);

解码:将指令的操作码部分送给CU,由CU负责解码;

执行指令:因为是取数相加指令, 首先进行取数操作,在CU帮助下, 将取数指令的地址码送到MAR中, 然后通过与内存控制器交互,从内存中取出该地址下的数据到MDR;由于需要进行逻辑运算,通过CU控制,将两个MDR寄存器(保存了来自内存的两个数据)中的值拷贝到ALU中,然后ALU进行加法操作(中间可能使用到AC寄存器),计算完毕后将结果拷贝到MDR寄存器,最后写入回内存。

PSW

补充说明一个重要的寄存器:PSW。

在CPU中,有着PSW寄存器,表示程序状态字,这个寄存器中保存了一些控制位,比如CPU的优先级、CPU的工作模式(用户态、内核态)。

在CPU进行进程切换的时候,需要将寄存器中和当前进程有关的状态数据写入内存对应的位置(内核中该进程的栈空间)保存起来,当切换回该进程时,需要从内存中拷贝回寄存器中。即上下文切换时,需要保护现场和恢复现场。

内核态的CPU,可以执行指令集中的所有指令,并使用硬件的所有功能。

用户态的CPU,只允许执行指令集中的部分指令。一般而言,IO相关和把内存保护相关的所有执行在用户态下都是被禁止的,此外其它一些特权指令也是被禁止的,比如用户态下不能将PSW的模式设置控制位设置成内核态。

用户态CPU想要执行特权操作,需要发起系统调用来请求内核帮忙完成对应的操作。其实是在发起系统调用后,CPU会执行trap指令陷入(trap)到内核。当特权操作完成后,需要执行一个指令让CPU返回到用户态。

除了系统调用会陷入内核,更多的是硬件会引起trap行为陷入内核,使得CPU控制权可以回到操作系统,以便操作系统去决定如何处理硬件异常。