FPGA程序烧写方式——AS PS JTAG

FPGA器件有三类配置下载方式:

1:主动配置方式(AS)

2:被动配置方式(PS)

3:最常用的JTAG方式

AS模式(active serial configuration mode): FPGA每次上电时作为控制器,由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,向配置器件主动发出读取数据信号,从而把EPCS**的数据读入FPGA中,实现对FPGA的编程配置数据通过FPGA_DATA0引脚送入FPGA,配置数据被同步在FPGA_DCLK上,1个时钟传送1位数据。

PS模式(passive serial configuration mode): 由外部计算机或者控制器控制配置过程,通过加强型配置器件(EPC16, EPC8)等配置器件来完成,EPCS作为控制器件,把FPGA当作存储器,把数据写入到FPGA中,实现对FPGA的编程,该模式可以实现对FPGA在线可编程。

JTAG模式:JTAG是直接烧到FPGA里面的,由于是烧写到SRAM中,因此断电后要重烧,AS是烧到FPGA的配置芯片里保存的,每次上电就写到FPGA里。

一般情况下,Cyclone器件应该有两种下载方式,AS和JTAG,AS就是下载.pof文件到EPCS**中,而JTAG是下载.sof文件到FPGA中的SRAM中。

如何生成.pof文件并将其下载到EPCS**中呢?

首先在建立好工程,编译和分配引脚之后。

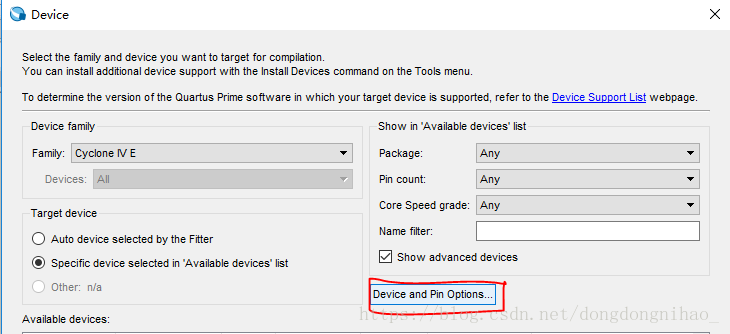

单击device,选择device and pin options

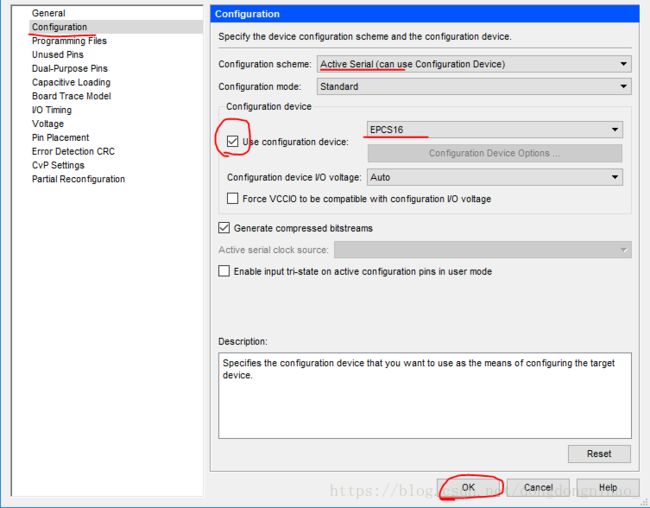

进入后选择:

然后重新编译就会生成.pof文件,就可以在programmer中下载了。

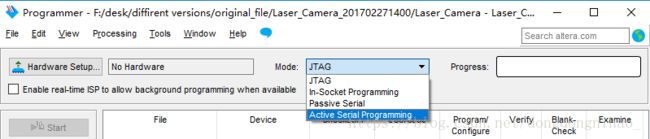

mode选择active serial programming。

在program/configure中打勾。点击start开始下载。过会儿下载成功。

然后再把板子的run/prom的开关切换回run状态,下次上电保持程序不丢失。

一般在做FPGA实验板的时候,用AS+JTAG的方式,这样可以用JTAG方式调试,在调试无误后采用AS模式把程序烧写到配置芯片里面去,这样有一个明显的优点,就是在AS模式不能下载的时候,可以利用QuartusII自带的工具生成JTAG模式下可以利用的.jic文件,来验证配置芯片是否已经损坏。

首先来看.jic文件如何生成:

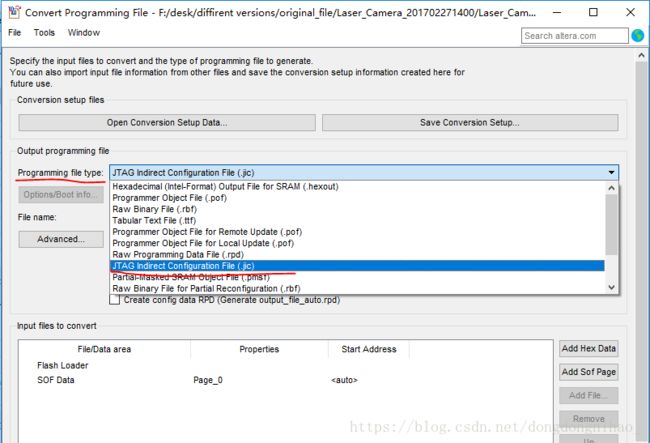

1,在QuartusII界面选择File-Convert Programmer Files

2,Programming file type 选择.jic。

3,Configure device 根据实际选择,这里选择EPCS16

4,在File name 文本框中,输入或浏览选择JIC 文件名和存放路径。

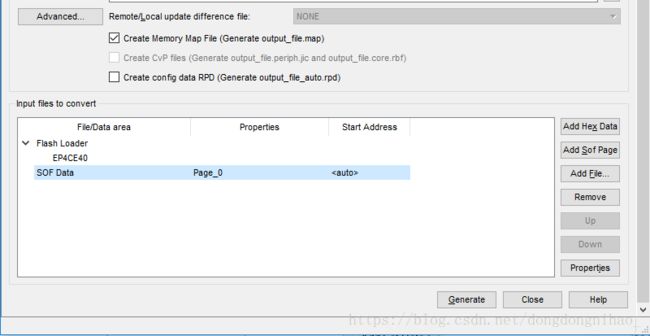

5,

在Input files to convert 栏中单击Flash Loader,

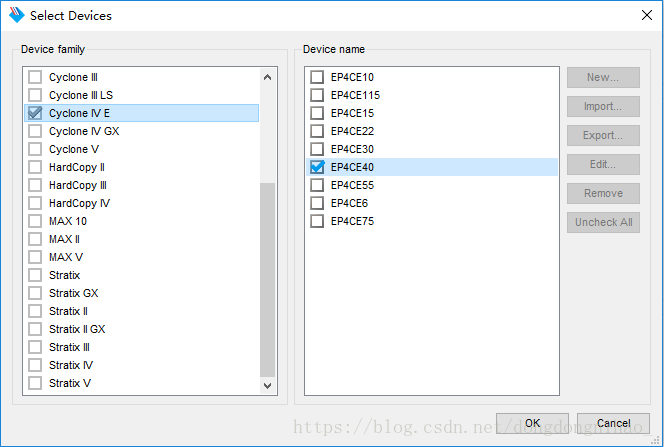

单击 add device 打开Select Device (选择器件) 对话框

根据实际情况选择相应器件,并ok

6,

在Input files to convert 栏中单击SOF Data

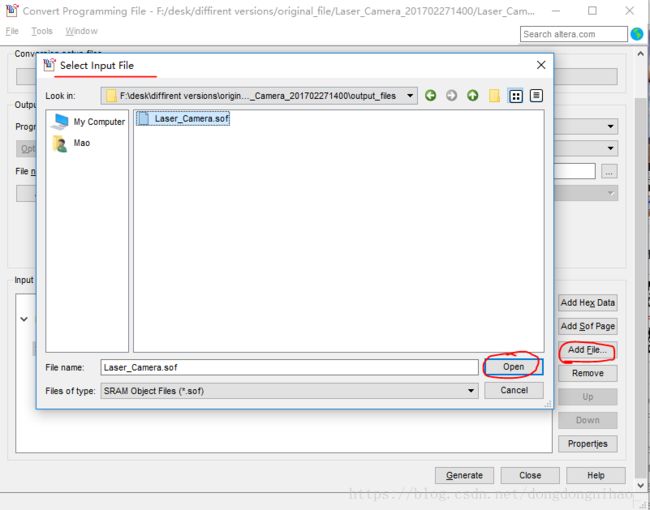

7,点击add file

8,

SOF Data 下面出现要被转换的输入SOF 文件,如图所示。单击SOF Data 下的输入SOF 文件,

单击Properties打开SOF File Properties (SOF 文件属性) 对话框。(注意SOF选中的时候,才能打开

Properties

)

9,

通过上面的步骤,就完成了SOF 文件到JIC 文件的转换。

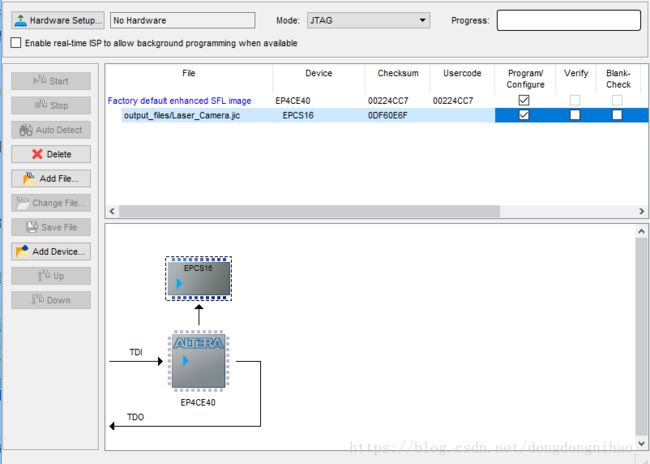

接下来使用.Jic文件和QuartusII Programmer对EPCS**进行烧写

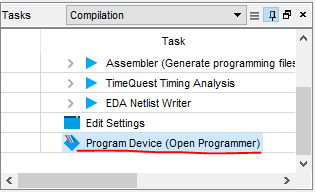

1 双击启动Programmer

2

参照下图,选中图中的Program/Configure 下的两个复选框;注意,如果有打开的SOF文件,在JTAG 烧写JIC 的时候,需要先删除掉。

3 单击户St a rt 开始编程,等待编程完成。