ARM9时钟体系结构

本文主要介绍AT91RM9200以及S3C2440处理器的时钟体系结构。

0 概要

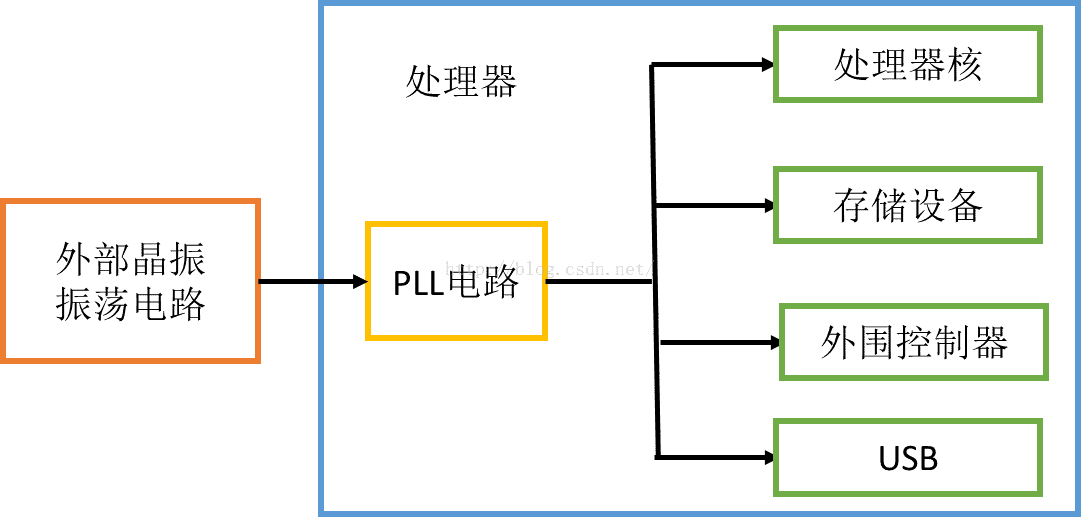

处理器的时钟源都是外部晶振振荡器产生的,有12MHz也有18MHz的(当然通常情况下外部还会挂接一个数百KHz的晶振,它是RTC所需),但无论是何种都不可能满足ARM核的数百兆赫兹的工作频率(关于各种ARM核的工作频率见附0)。因此需要通过芯片内部的锁相环电路产生更高的工作频率,产生的工作频率再经过分频或者倍频分别供给处理器核以及外设使用。整体框架如下图所示。

图处理器时钟架构

注:上图之所以将USB单独列出是因为总结的两个处理器(S3C2440以及9200)都有独立提供USB的时钟,至于具体的原因以及与外围控制器中USB控制器的区别不甚理解。

针对上图以及具体处理器再进行一次简单的分析。

1 AT91RM9200时钟体系结构

针对到具体应用对象(外围控制器等),分为处理器时钟、主时钟、以及USB时钟。处理器时钟(Processor Clock)与主时钟(Master Clock)分别是针对处理器和外围设备控制器。另外内部集成了2个PLL电路,生成PLLA以及PLLB时钟,原理框架见下图。

图 AT91RM9200时钟架构

简单分析:

首先,时钟发生器主要由两个内部振荡器以及分频器组成,它们接收外部晶振的是内部的时钟发生器模块,它产生了四个时钟作为最终使用时钟的时钟源:SlowClock、MainClock、PLLAClock和PLLBClock。注这里的MainClock并不等于MasterClock。四者产生原理图如下图所示。

SlowClock是系统内唯一保持32KHZ时钟,由慢时钟振荡器产生,用于慢时钟模式下使用。9200有四种工作模式:普通模式、空闲模式、慢时钟模式和StandBy模式(具体区别可参见附1)。

MainClock主时钟,经过内部主振荡器产生,可作为主时钟的输入时钟源选择之一。

PLLA与PLLB时钟,数据手册中表述时钟源来自MainClock,而代码中却根据外部时钟计算得到。这点应该需要硬件知识才好理解,目前先按代码中的计算方法理解。

然后,生成的四个时钟分别通过倍频和分频,分别生成处理器时钟、主时钟以及供给USB的时钟。如下图所示。相对于ARM7的处理器时钟始终与主时钟一致不同,ARM9提供了倍频的方法,从而使得CPU可以工作在更高频率的状态。[ 这也可以解释ARM9为什么可以工作在更高频率,因为多了个倍频器]

最后简单说明下USB时钟是由PLL电路生成,PLLAR寄存器或者PLLBR寄存器中有相应的位能够控制USB是48MHz还是96MHz。

另外,电源管理控制器,提供了对每个外设控制器独立控制时钟只写的寄存器--PMC_PCER/PMC_PCDR(如下图所示),使能操作PCER,禁止就写PCDR。至于每一位对应何种控制器,手册上并没有说,是从BIOS代码中查到的,具体可参阅代码。

图 AT91RM9200时钟架构

综上所述,外部晶振,经过内部的时钟产生器,生成了四个时钟,而主时钟根据寄存器选择其中一个作为时钟源,经过设定的分频倍频参数,得到最终的时钟,提供给外设控制器。而处理器时钟则是根据主时钟和设定的倍频参数得到。USB时钟则是直接从PLLA或者PLLB中得到。

2 S3C2440时钟体系结构

2440时钟分为三类:FCLK、HCLK和PCLK。其中FCLK是为ARM920T内核提供时钟、HCLK主要是为AHB高速总线上挂接硬件提供工作频率、PCLK为APB低速总线上提供时钟。如下图所示。

S3C2400内部同样拥有2个锁相环电路(PLL):MPLL和UPLL,不同之处在于功能不同。2440中较为简单。UPLL为USB控制器提供时钟。

综上,S3C2440时钟体系可以简单总结为,外部晶振产生的时钟经过MPLL生成了FCLK、HCLK和PCLK。经过UPLL生成为USB控制器提供的时钟频率。

附0 ARM系列处理器整理

其中,ARM7大多数不过100MHz,ARM9不过400MHz、11能够达到接近700MHz,A8则是600M~1GHz,A9则是1.2~1.5GHz, A53则是2.2G且是8核。

附1 AT91RM9200的工作模式

支持下列工作模式,并提供不同的功耗等级及事件响应延迟时间:

• 普通模式:ARM 处理器时钟时钟使能,外设时钟是否使能由应用需求决定。

• 空闲模式:ARM 处理器时钟禁用并等待下一次中断 ( 或主复位)。外设时钟是否使能由

应用需求决定。可能需要 PDC 传输。

• 慢时钟模式:慢时钟模式与普通模式类似,但主振荡器及PLL 关闭以节约功耗,处理

器与外设运行在慢时钟模式下。注意,慢时钟模式是复位后选择的模式。

• Standby 模式:Standby 模式是慢时钟模式与空闲模式下结合。它使能处理器以快速响应唤醒事件,并能保持较低的功耗。