Zynq 7000的hello world 实验

开发当然要从最简单的学起,从串口打印"Hello World"是开发ZYNQ的嵌入式系统的入门设计。初学者必项经过本实验锻炼才能理解和体验ZYNQ的软硬件开发过程。我们将在AX7010/AX7020开发板上创建一个简单的ZYNQ嵌入式系统。然后我们将会使用SDK创建一个简单的软件应用程序,并下载到ZYNQ的ARM处理器中,实现串口的字符打印。

1 Vivado工程创建

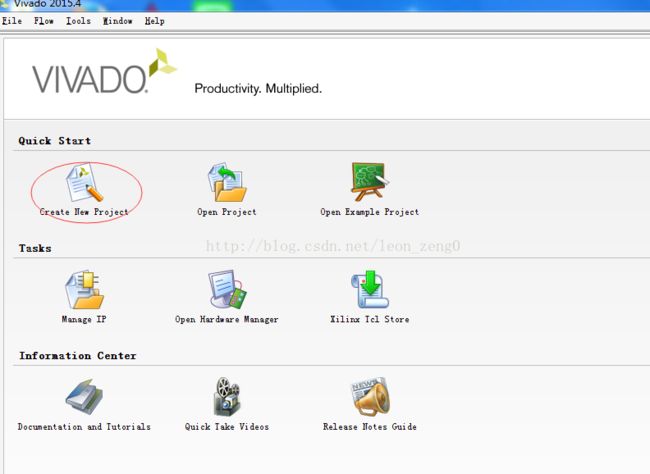

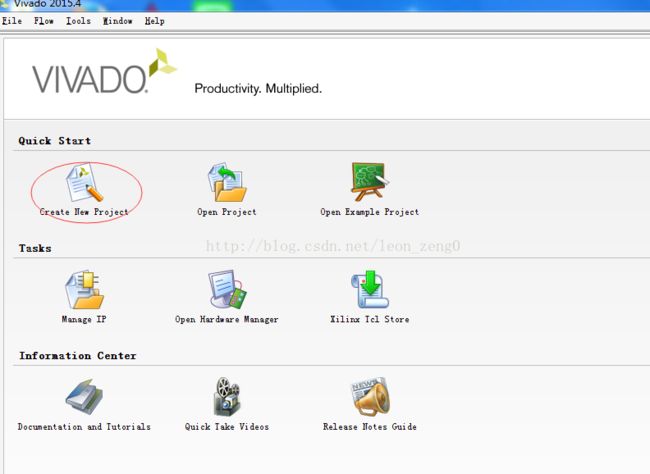

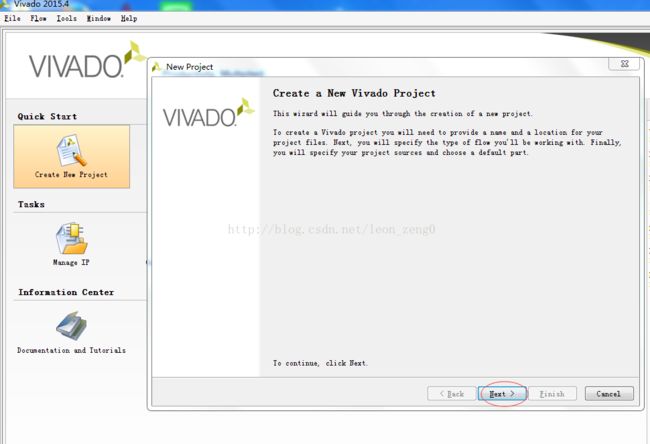

1.1 在Vivado开发环境里双击Create New Project图标

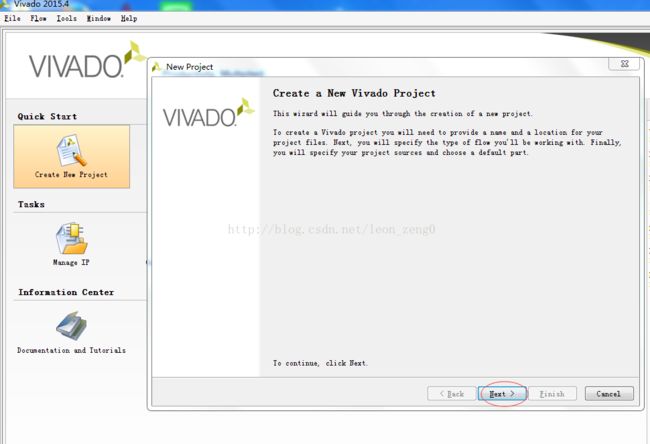

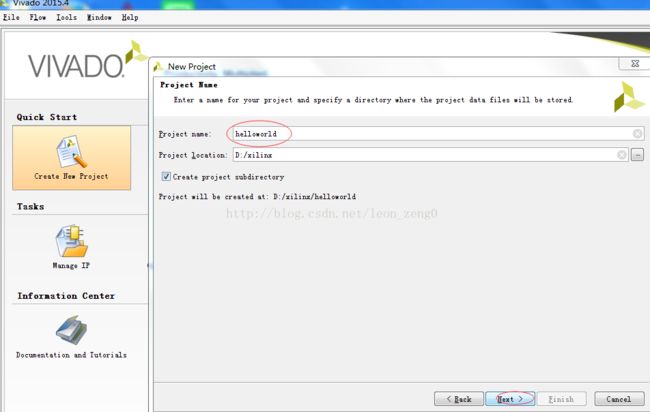

1.2 弹出一个Vivado工程向导,点击Next按钮。

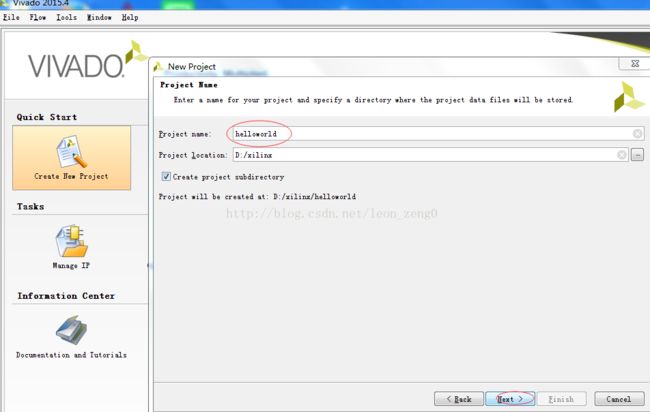

1.3 在弹出的对话框中输入工程名和工程存放目录,我们这里取一个helloworld的工程名。点击Next按钮。

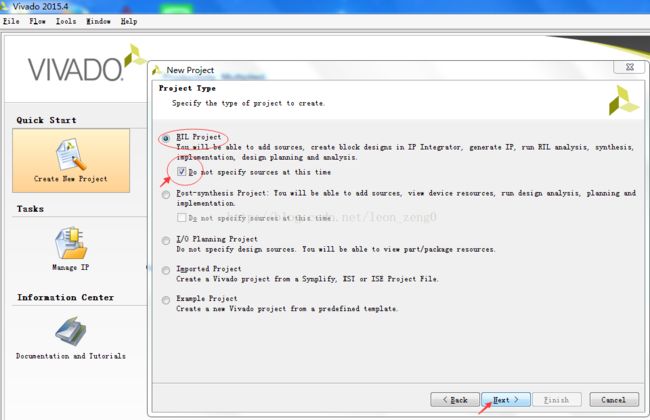

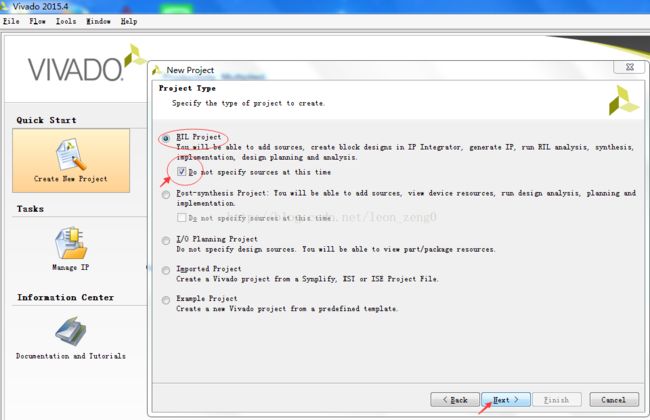

1.4 在下面的对话框中默认选择RTL Project, 勾上下面的 Do not specify source at this time 。如果不勾上,下一步会进入添加source file界面。

1.3 在弹出的对话框中输入工程名和工程存放目录,我们这里取一个helloworld的工程名。点击Next按钮。

1.4 在下面的对话框中默认选择RTL Project, 勾上下面的 Do not specify source at this time 。如果不勾上,下一步会进入添加source file界面。

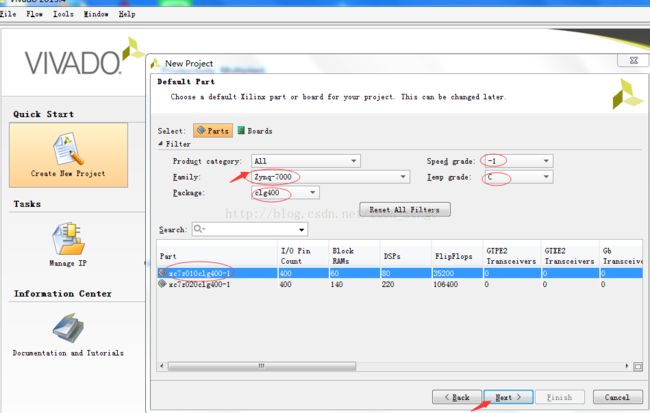

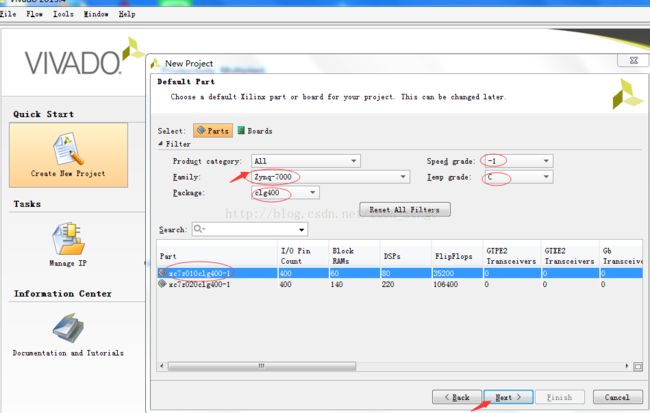

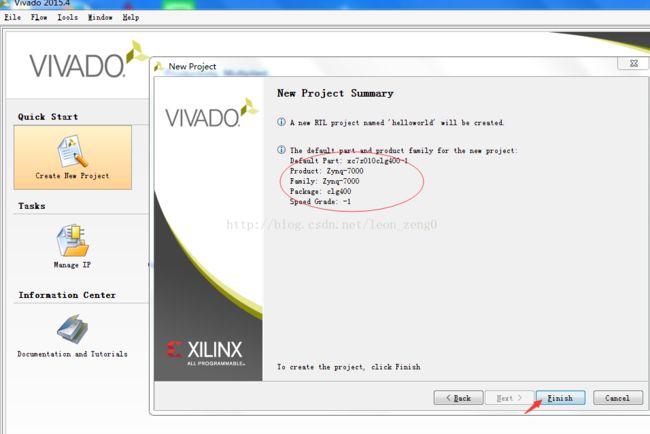

1.5 在接下来的对话框选择所用的FPGA器件,以及进行一些配置。FPGA芯片型号一定要跟开发板上的型号一致,我这里是黑金的AX7010\AC7010。首先在Family里选择Zynq-7000, Speed grade选择-1, Temp grade选择C,在Package选择clg400,然后在下面的列表中选择xc7z010clg400-1。(AX7020用户选择xc7z020clg400-2)。

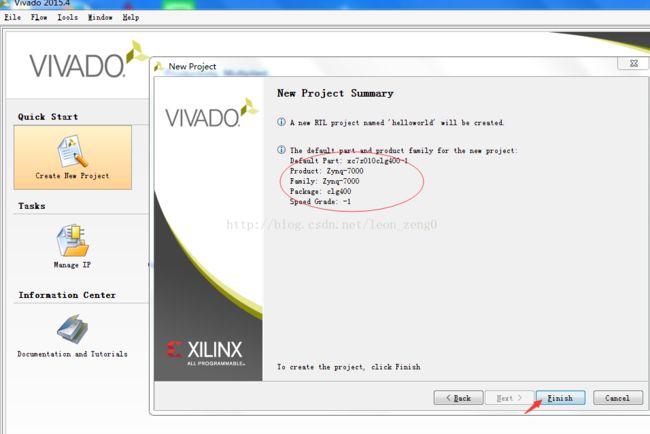

1.6 再次确认一下板子型号有没有选对,没有问题再点击“Finish”完成工程创建。

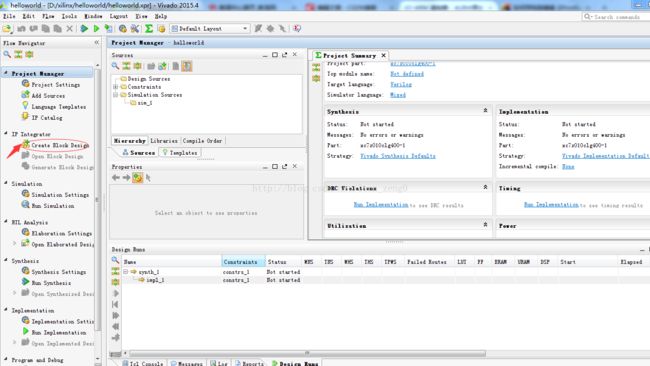

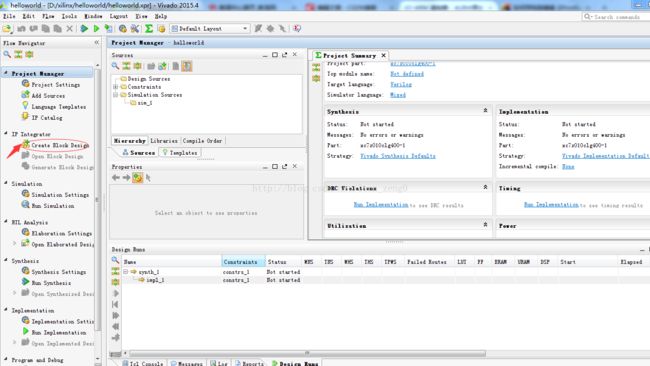

工程创建后如下图所示:

1.6 再次确认一下板子型号有没有选对,没有问题再点击“Finish”完成工程创建。

工程创建后如下图所示:

2 原理图设计

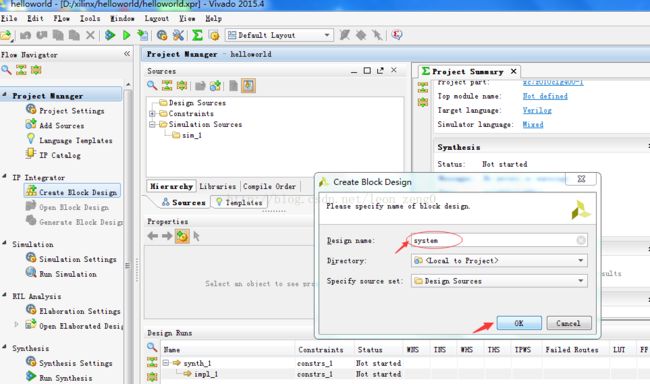

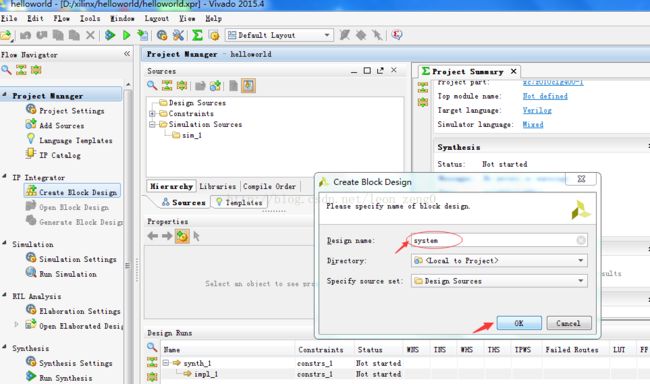

2.1 ZYNQ的嵌入式系统开发一般有原理框图的形式来设计,这样硬件的连接看起来会更加直观。点击Create Block Design按钮来添加原理图设计文件。

2.1 ZYNQ的嵌入式系统开发一般有原理框图的形式来设计,这样硬件的连接看起来会更加直观。点击Create Block Design按钮来添加原理图设计文件。

2.2 在弹出的对话框里输入原理图设计文件的名字,这里我们取名为"system"。

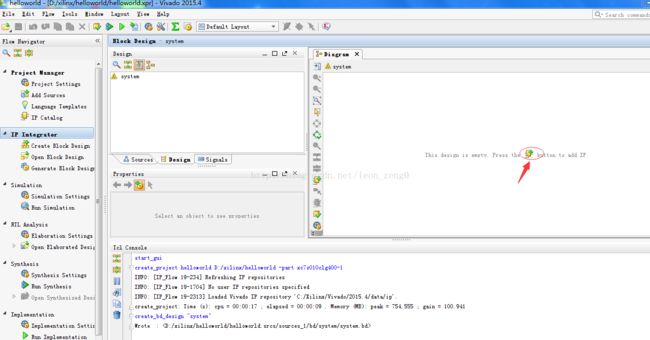

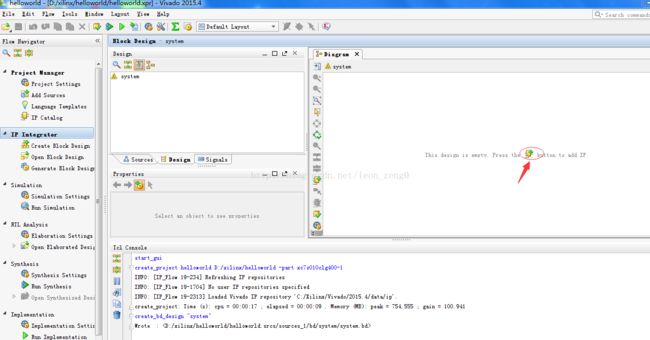

2.3 出现Diagram的空白对话框,点击图标来添加ARM处理器内核到这个空白的原理图里。

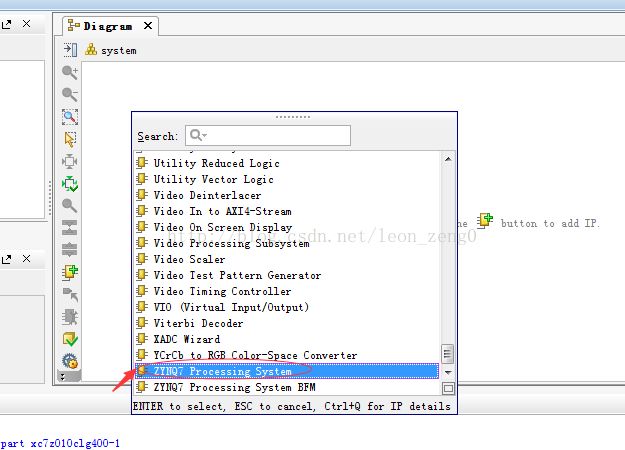

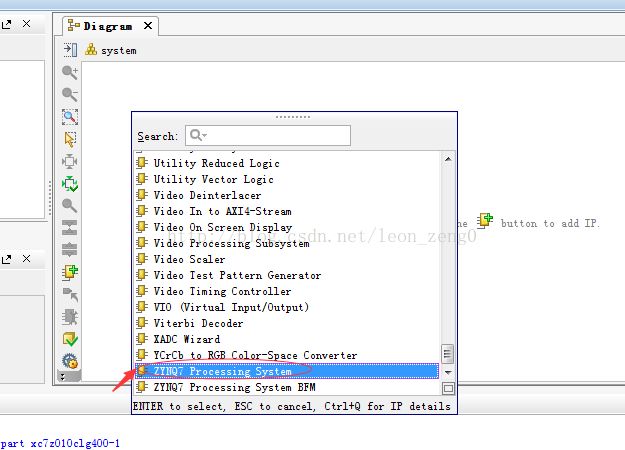

2.4 这里有很多Xilinx提供的IP,我们找到ZYNQ7 Processing System 并双击 添加,不要选择后面带BFM(总线功能模型)的,带BFM的IP 为先前的IP处理器版本。

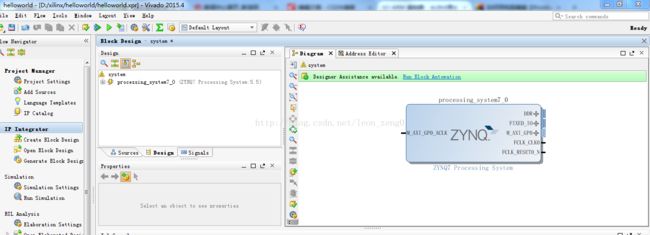

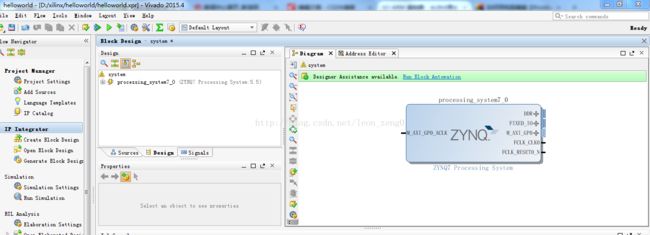

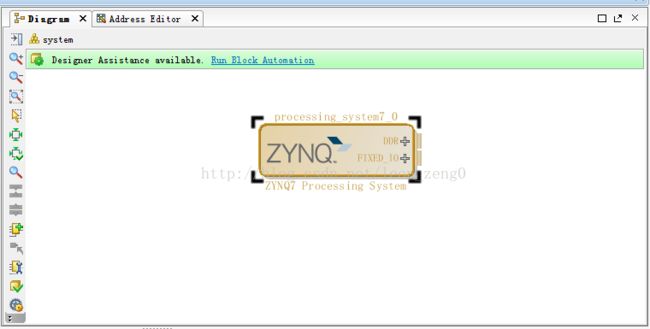

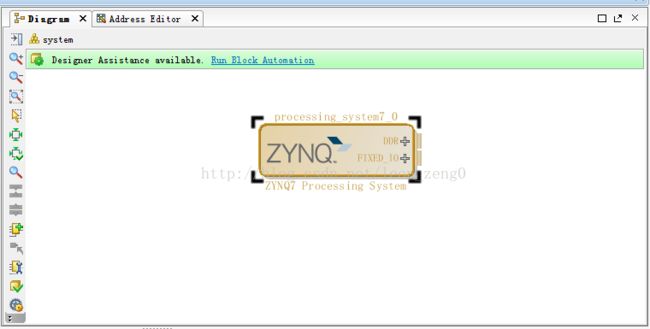

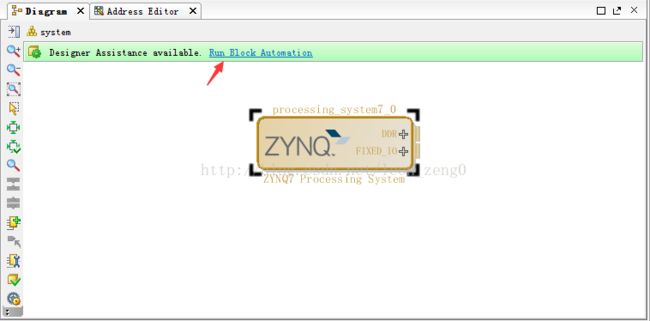

ZYNQ的处理器系统已经添加到Block Diagram窗口上了。

3 ZYNQ系统的配置

3 ZYNQ系统的配置

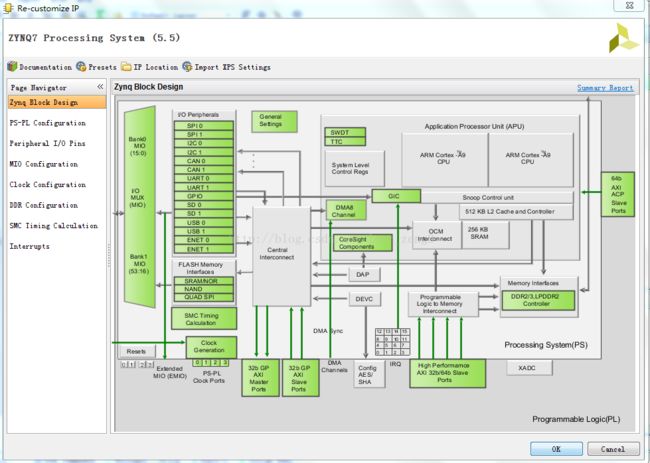

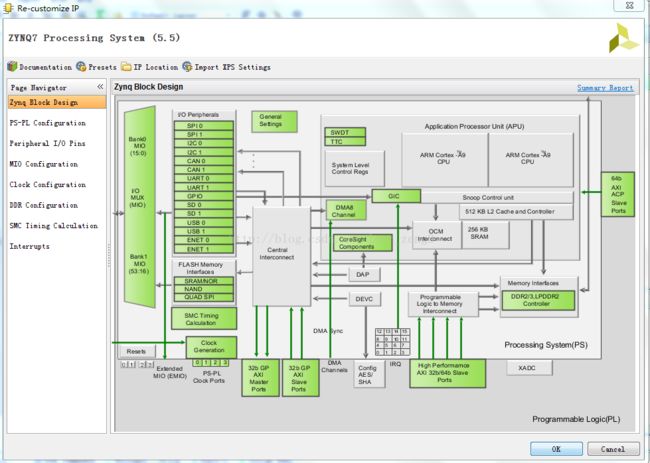

3.1 双击Diagram界面里的ZYNQ Processing System,打开ZYNQ系统的配置界面。

其中Page Navigator界面下有8个子项,分别为Zynq Block Design, PS-PL Configuration,Peripheral I/O Pins, MIO Configration, Clock Configuration, DDR Configuration, SMCTiming Calculation, Interrupts。这些页面选项是针对ZYNQ的不同硬件模块的配置,其中PS_PL页面提供了PS到PL的相关接口配置信息以及PS部分一些配置信息;Peripheral I/O Pins页面主要是对一些通用外设接口的配置;MIO Configruation页面主要是对MIO已经EMIO的分配控制;Clock Configruation页面主要是对PS端时钟资源的配置和管理;DDR Configration页面主要是对DDR控制器一些参数的配置;Interrupts页面主要是对中断进行配置管理。具体页面里的每项内容这里我们不一一讲解了,很多配置我们都会在后面的应用中用到。

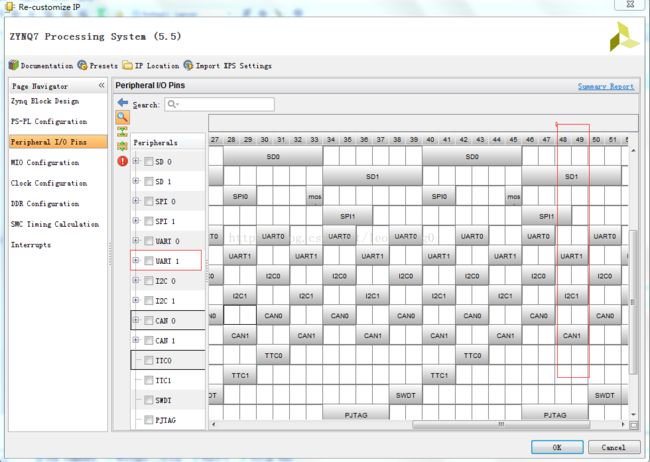

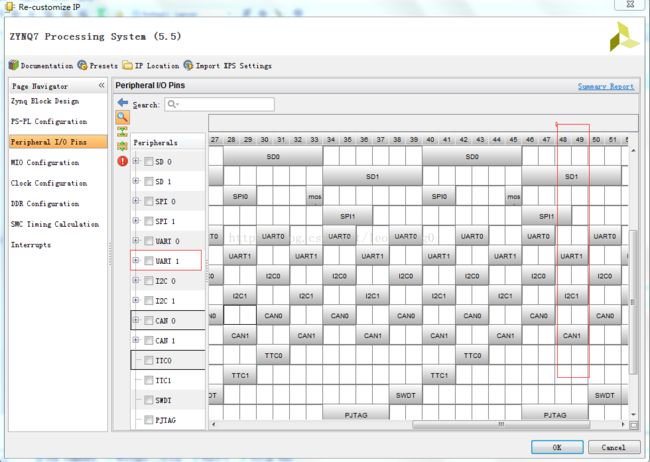

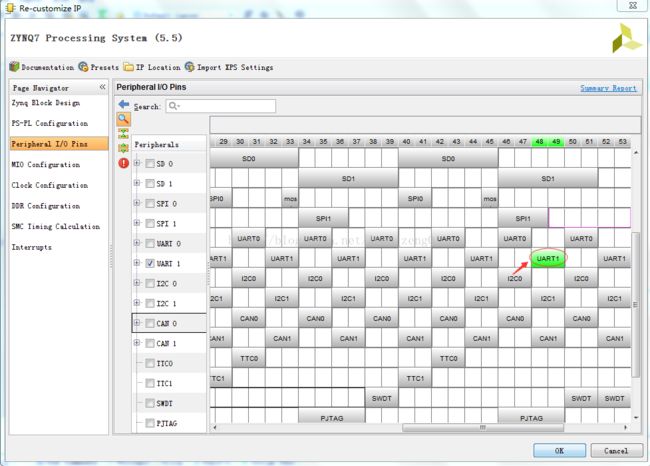

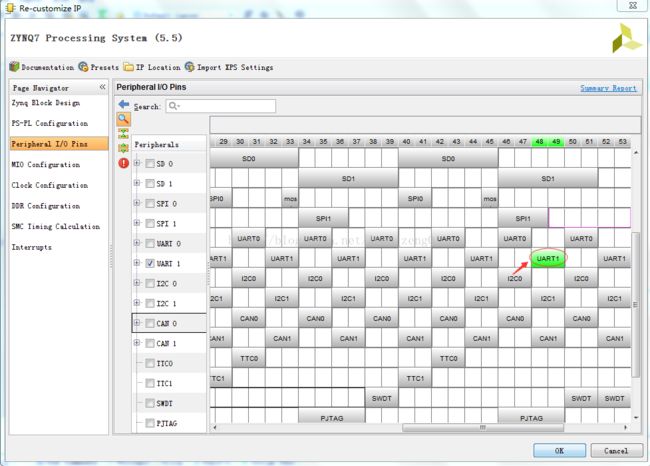

3.2 点击Peripheral I/O Pins,会出现以下的IO配置的界面。因为ZYNQ的MIO的管脚可以配置成很多功能,比如MIO48和MIO49,既可以配置成SD1的引脚,或者UART1的引脚,或者I2C1的引脚,还可以配置成CAN1的引脚。具体如何配置需要跟开发板的原理图对应。

在我们AX7010/AX7020开发板上,我们MIO48和MIO49是连接到UART芯片上,是作为串口通信使用的。

所以这里我们需要配置成UART1的功能,点击MIO48,49对应的UART1,方框的颜色会变成绿色。这样MIO48,49的管脚功能就固定了,只能作为UART的功能。其中MIO48为串口发送,MIO49为串口接收。

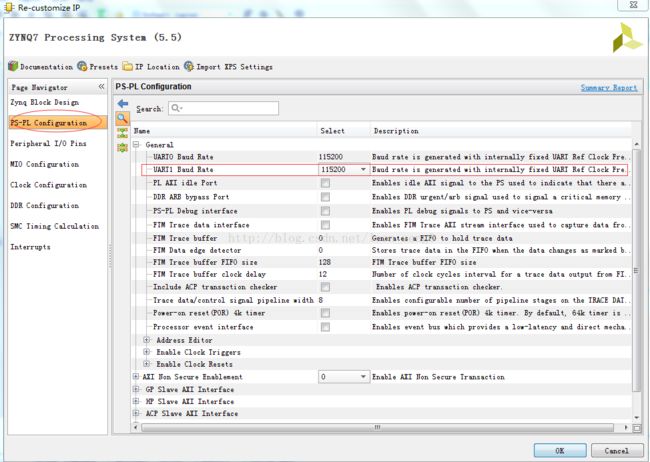

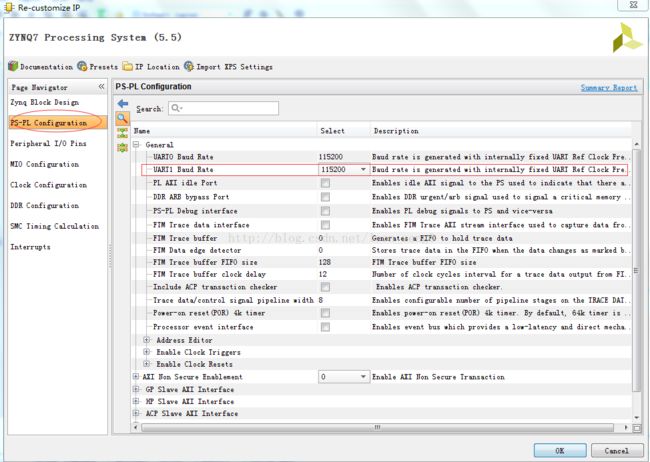

3.3 点击PS-PL Configuration,在General目录下,我们可以看到UART1的波特率是115200,这个波特率用户可以自己选择,我们这里就保留默认设置就可以了。

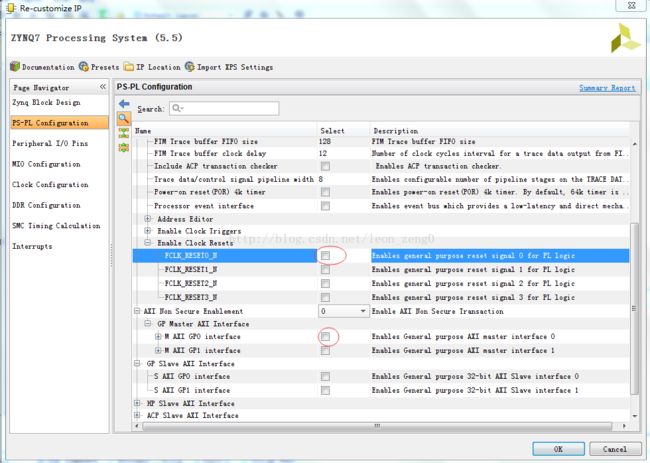

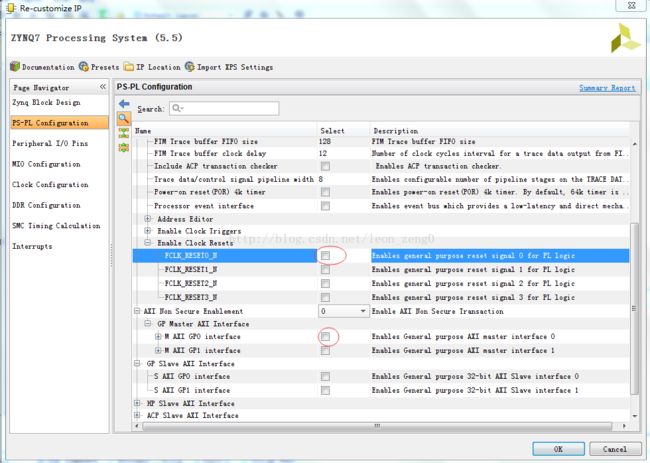

3.4因为本实验中没有用到PL部分外设,所以就没有PL外设需要挂到AXI的总线上,也就不需要AXI GP0的Master总线了,这里我们把FCLK_RESET0_N和M AXI GP0 interface的选项去掉。

3.4因为本实验中没有用到PL部分外设,所以就没有PL外设需要挂到AXI的总线上,也就不需要AXI GP0的Master总线了,这里我们把FCLK_RESET0_N和M AXI GP0 interface的选项去掉。

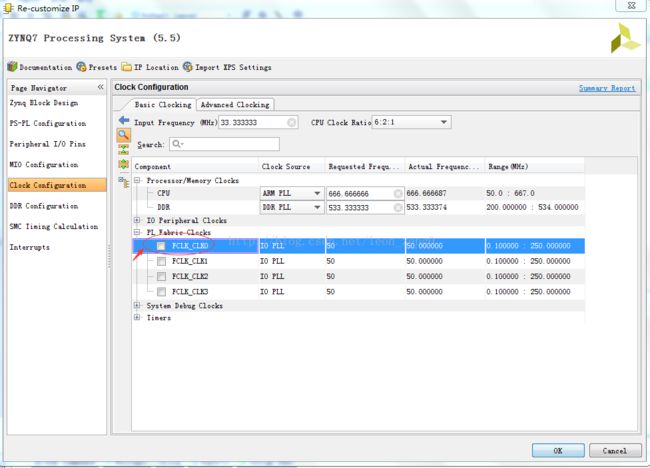

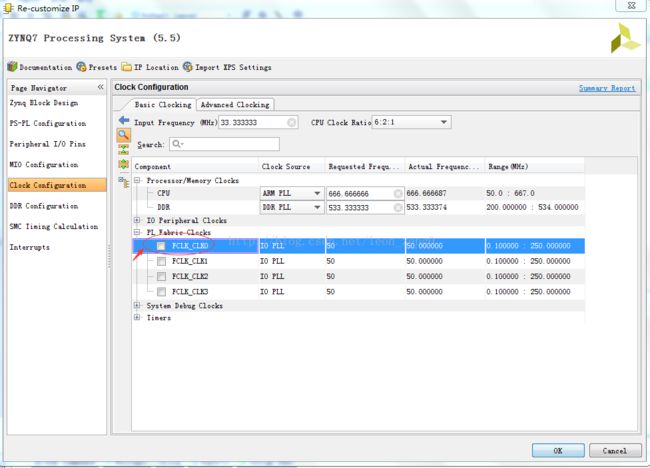

3.5 点击Clock Configuration,这个界面会显示ZYNQ系统的一些时钟,比如输入时钟是33.33333Mhz,这个时钟跟我们开发板上的PS的系统时钟是一样的。另外我们可以看到CPU的工作时钟是666.666666Mhz(AX7020开发板配置为767Mhz), DDR的工作时钟是533.333333Mhz,还有些外设的工作时钟。这些时钟频率我们不需要修改。

3.6 因为本实验中没有用到PL部分外设,所以可以把PL的FCLK_CLK0前面的选项去掉,不产生FCLK_CLK0。

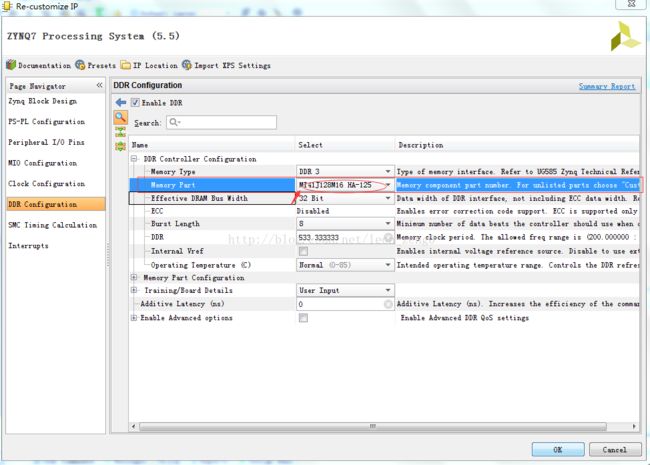

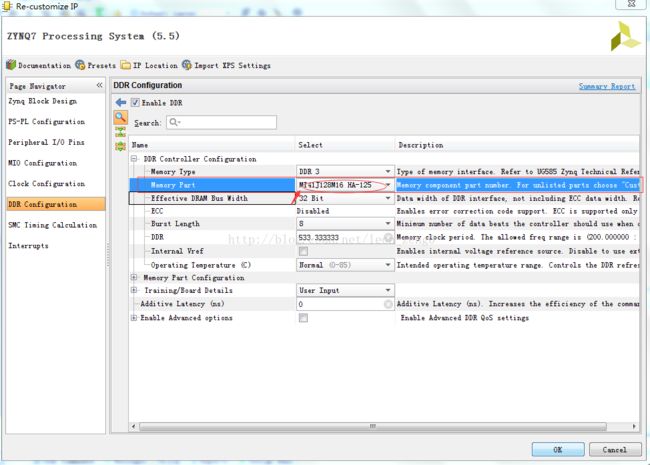

3.7 再打开DDR Configration,在这个界面上是选择DDR芯片的名称和一些参数。这里我们在Memory Part项中需要选择跟硬件DDR3型号一样的名称(AX7010的用户选择MT41J128M16 HA-125,AX7020的用户选择MT41J256M16RE-125)。

3.8 配置完成点击OK,退回到Vivado的开发环境。

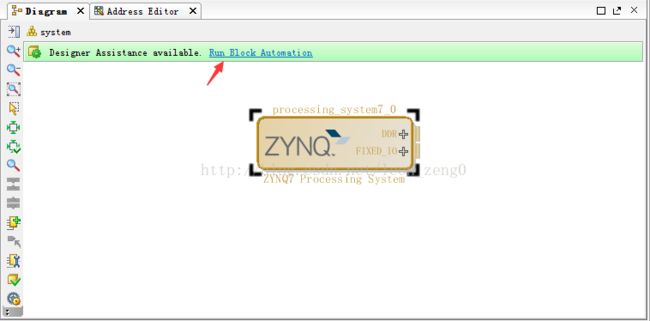

4 生成外部链接IO管脚

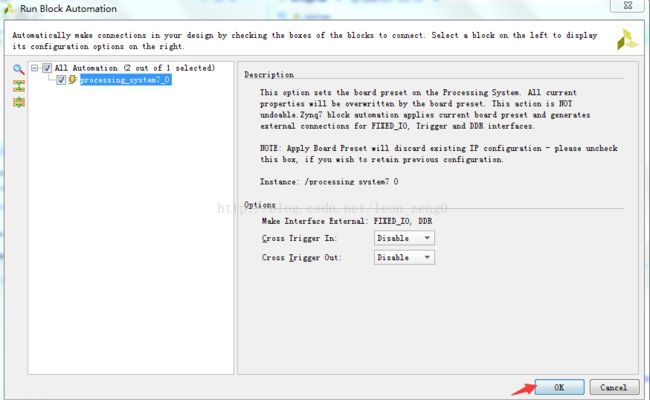

在Diagram界面里点击"Run Block Automation"完成对ZYNQ7 Processing System IP核的配置,并生成外部ZYNQ系统的外部链接IO管脚。

在Diagram界面里点击"Run Block Automation"完成对ZYNQ7 Processing System IP核的配置,并生成外部ZYNQ系统的外部链接IO管脚。

点击OK。

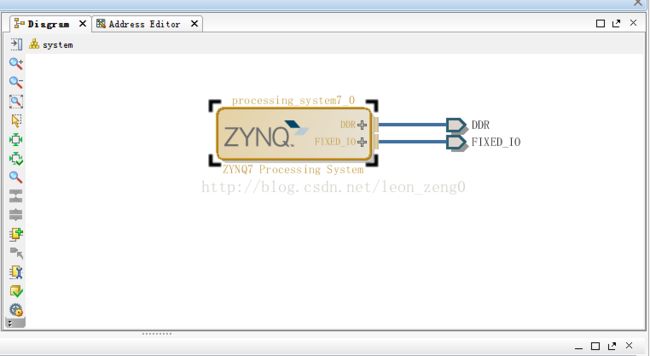

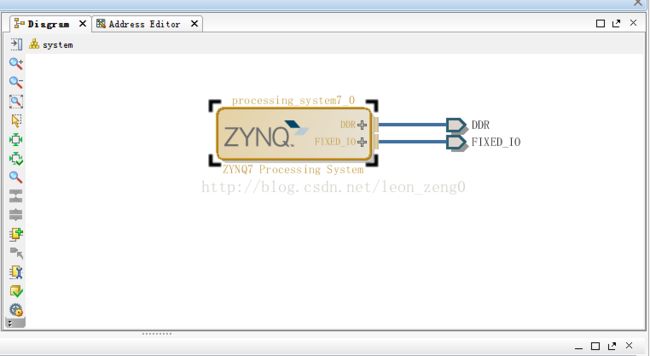

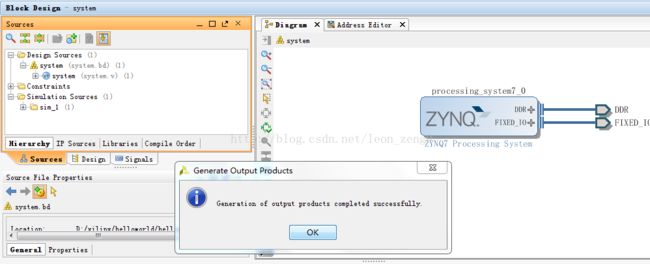

生成后的ZYNQ系统外部管脚如下,一个是DDR的接口,一个是FIXED_IO。

5 生成 HDL 文件

5 生成 HDL 文件

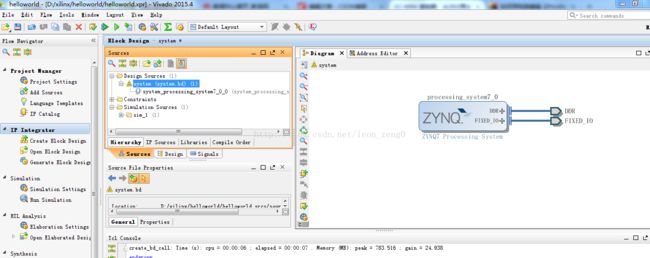

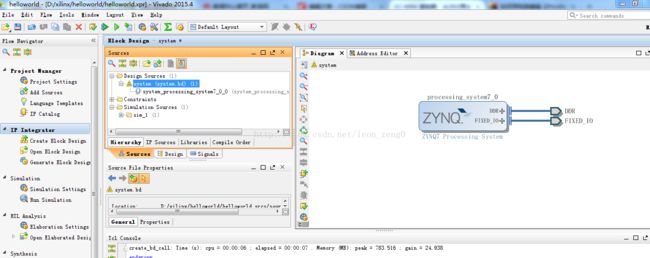

5.1 按Ctrl+S键保存一下Diagram,然后点击Sources选顷卡。

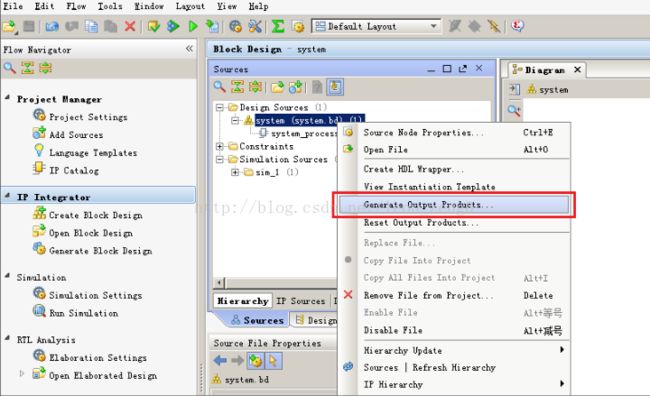

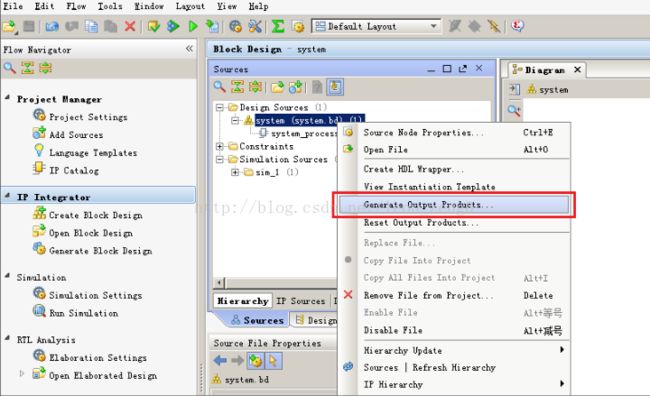

5.2 右键选择sysetm,在弹出的菜单中选择Generate Output Products...

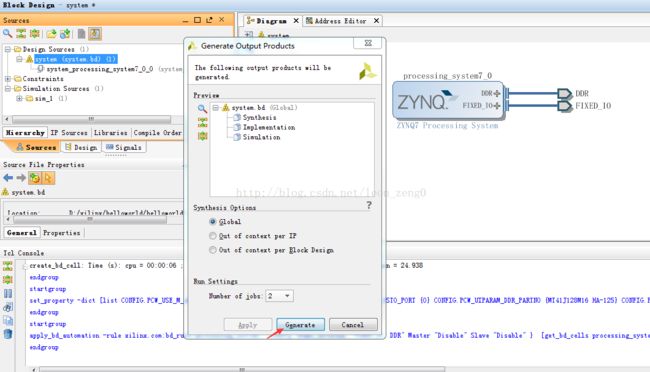

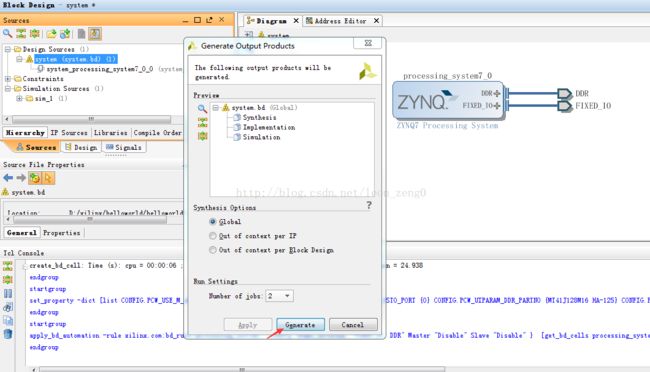

点击Generate按钮,这一操作将会生成Diagram Block Design的HDL源文件以及相应端口的约束文件。

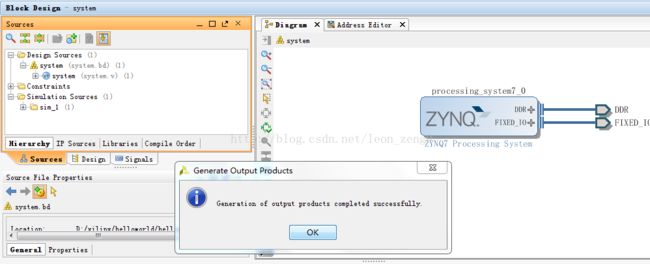

HDL文件System.v已经产生。

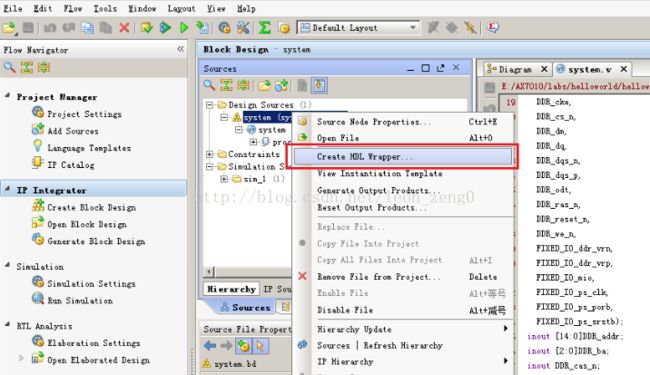

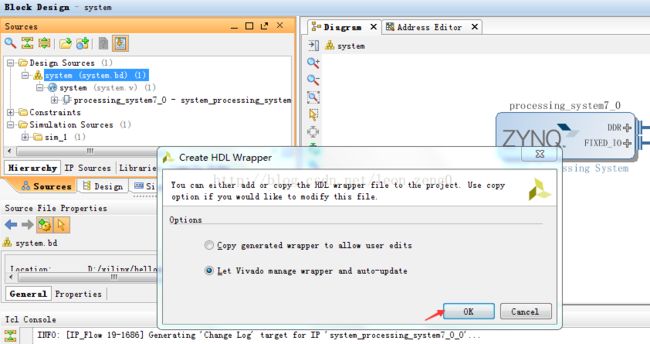

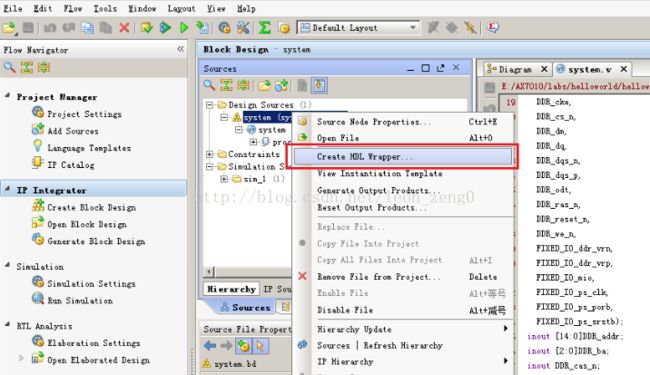

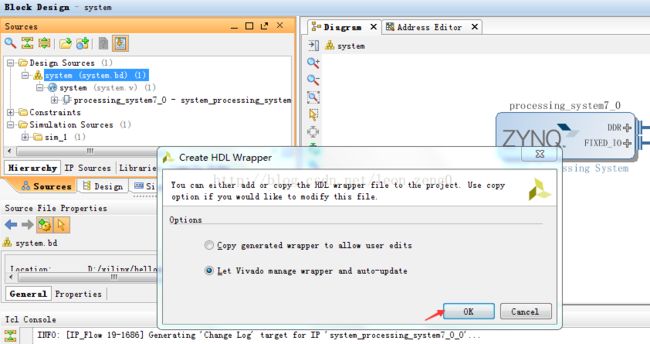

5.3 创建一个顶层的HDL文件,右键选择sysetm,在弹出的框框中选择Create HDL Wrapper..。

直接选择OK

直接选择OK

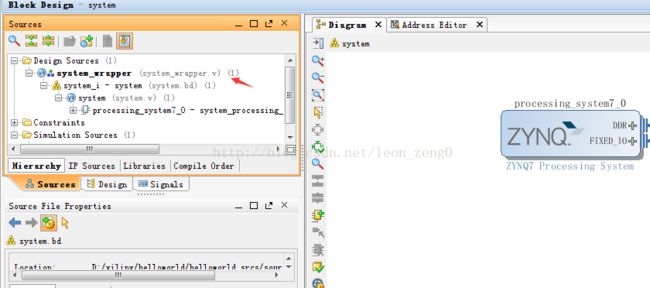

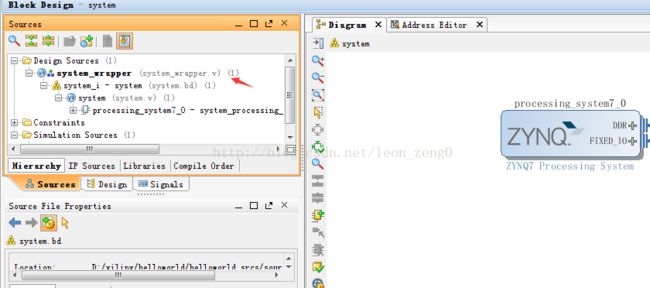

这样一个system_wrapper.v的顶层文件就生成了,这样我们就可以对该系统进行综合、布线并生成比特流了。

5.4 因为这个嵌入式系统只有PS部分的管脚,没有PL部分的管脚,而且PS部分的管脚都是固定的,所以我们不需要添加管脚约束文件。另外因为没有使用PL部分的资源,我们也不需要在Vivado下编译和生成bit文件了。

6 硬件导入SDK

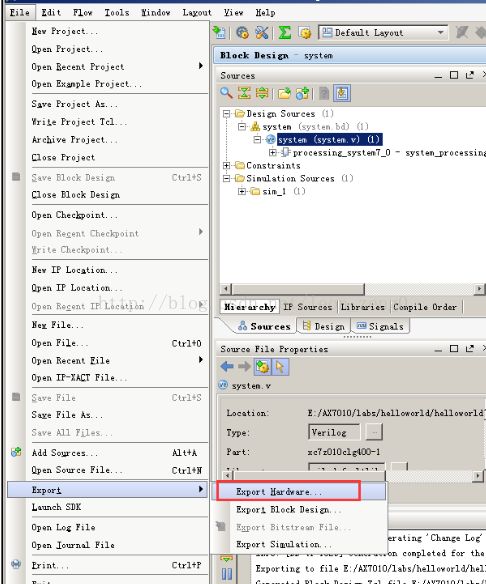

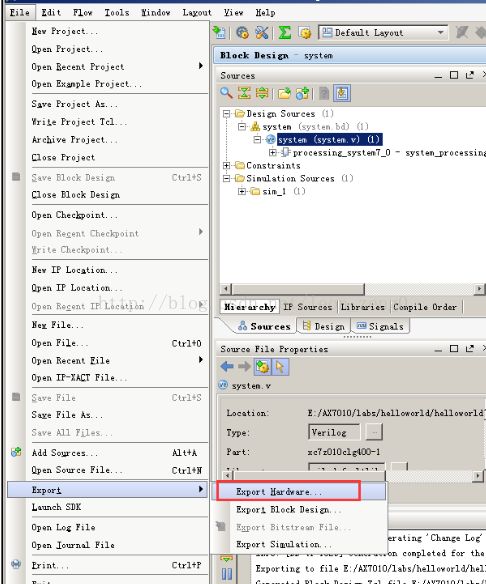

选择菜单File->Export->Export Hardware...。

因为没有生成bit文件,所以不要选Include bitstream,点击OK。

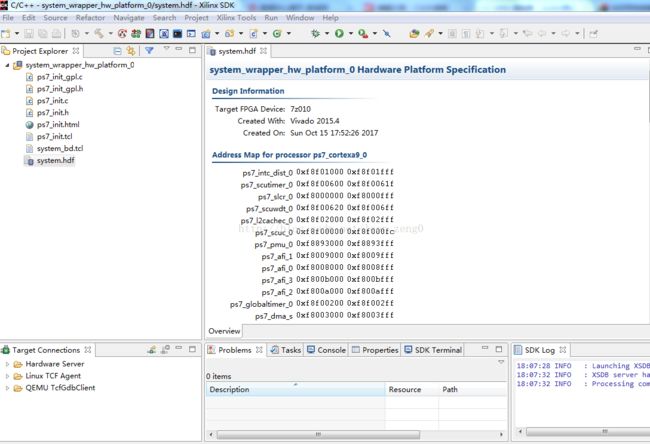

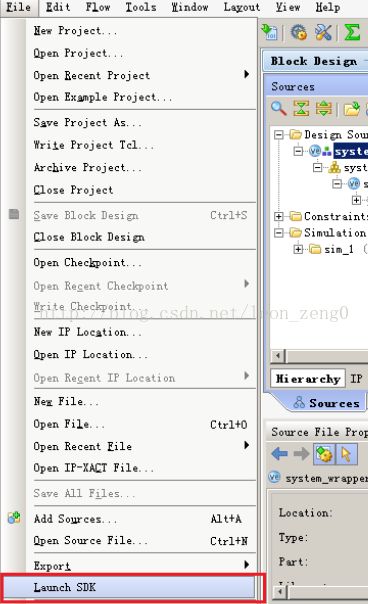

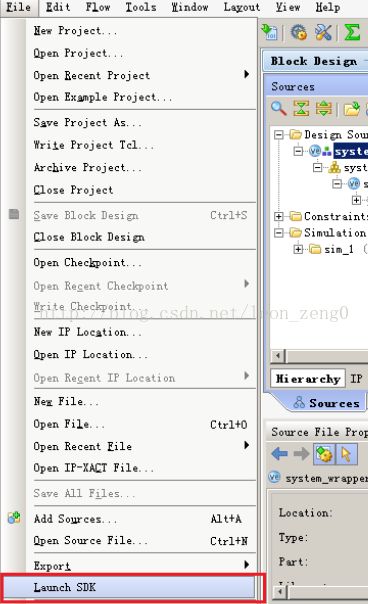

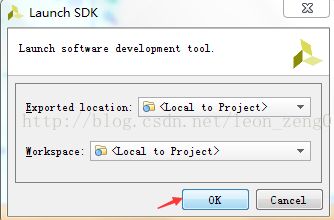

硬件导出完成后,选择菜单File->Launch SDK,启动SDK开发环境

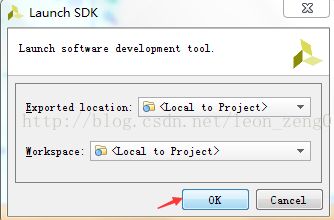

点击OK,软件会自动启动SDK开发环境

SDK软件编程

SDK软件编程

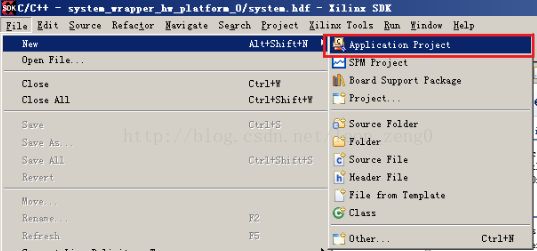

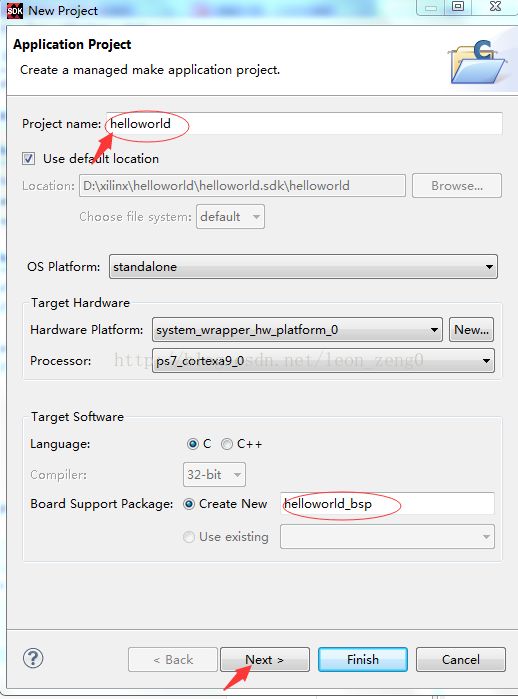

1.选择菜单File->New->Application Project,新建一个SDK的软件工程。

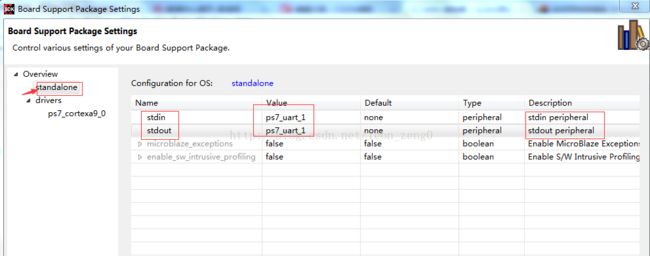

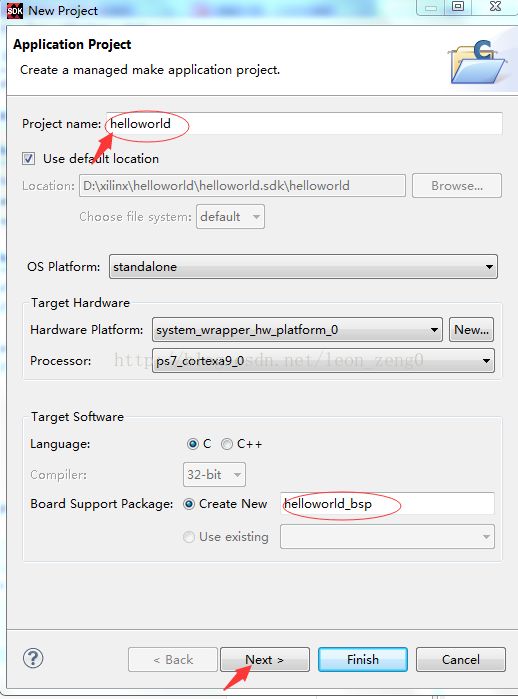

2.输入工程名字为helloworld,并生成一个新的bsp文件。

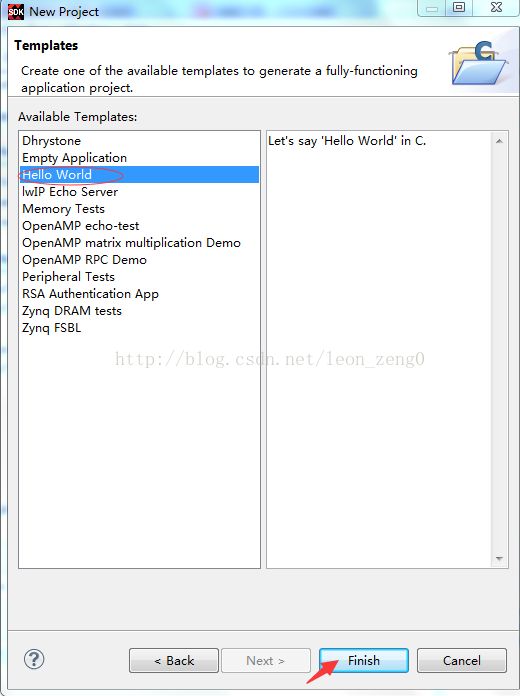

3.选择工程模版Hello World。

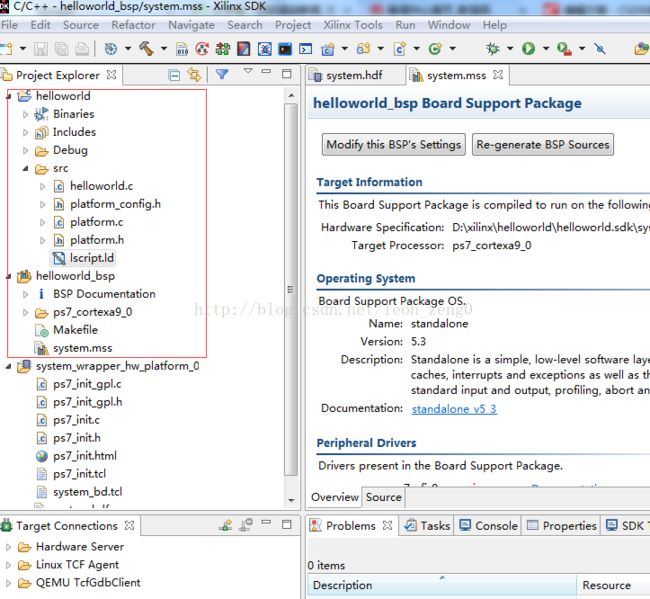

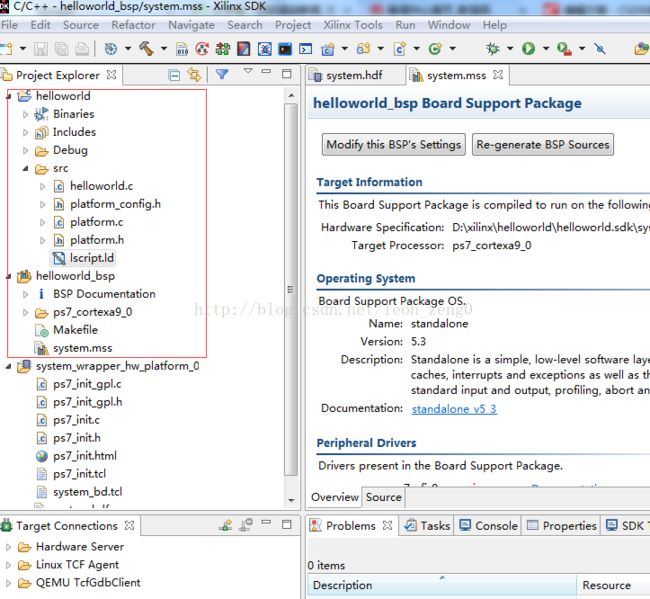

4.生成后的helloworld项目和bsp支持包如下,helloworld.c文件里就是打印一个hello World的字符。另外工程里有一个lscript.ld 定义程序或者数据是在内部的RAM或是外部的DDR里。

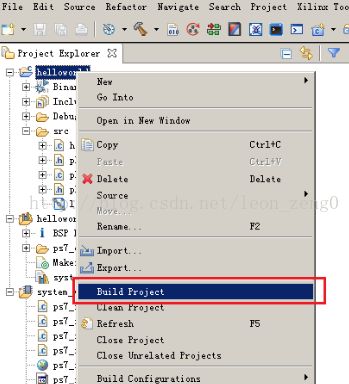

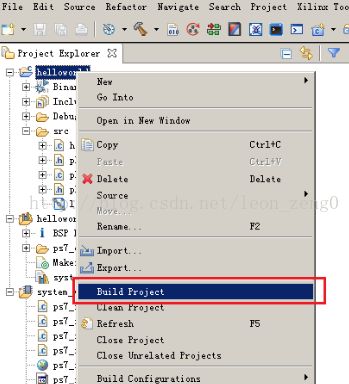

5.右键选择helloworld工程,选择Build Project,编译一下。

下载和调试

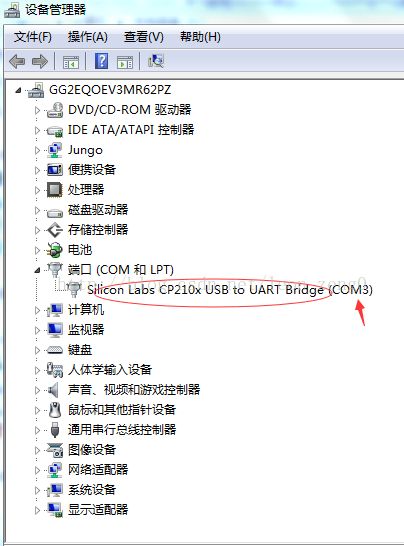

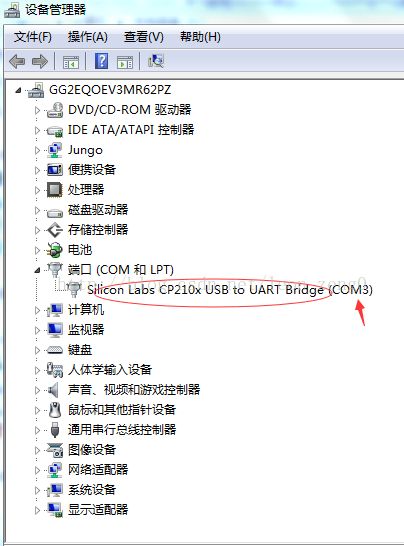

1.调试前需要连接JTAG线和Uart线到电脑的USB口并开发板上电,在电脑的设备管理器里我们能够看到开发板的串口。如下图,串口映射到COM3上。

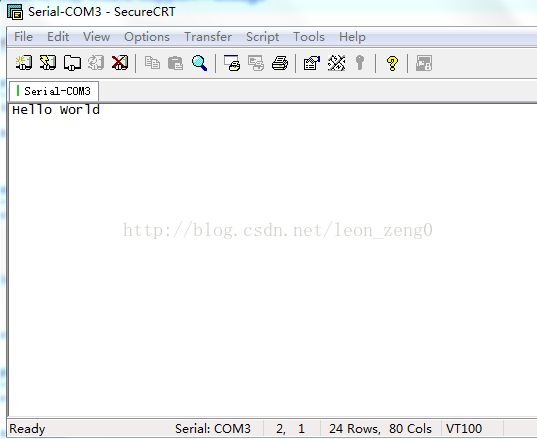

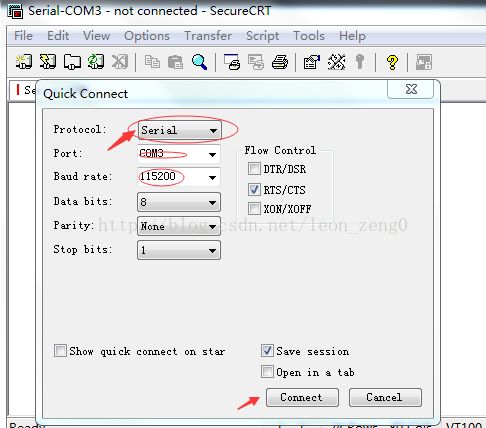

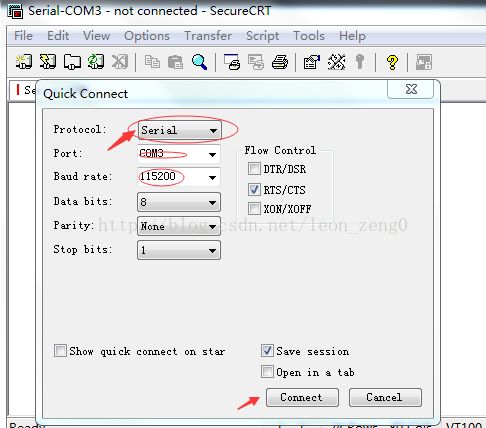

打开SecureCRT软件,配置端口为COM3,波特率为115200。

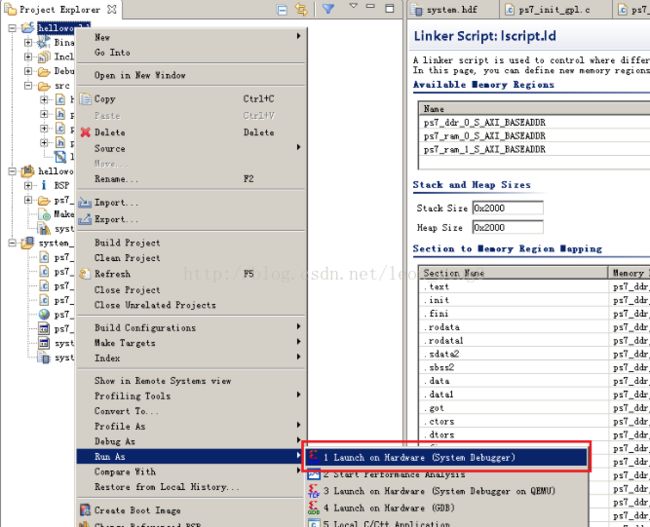

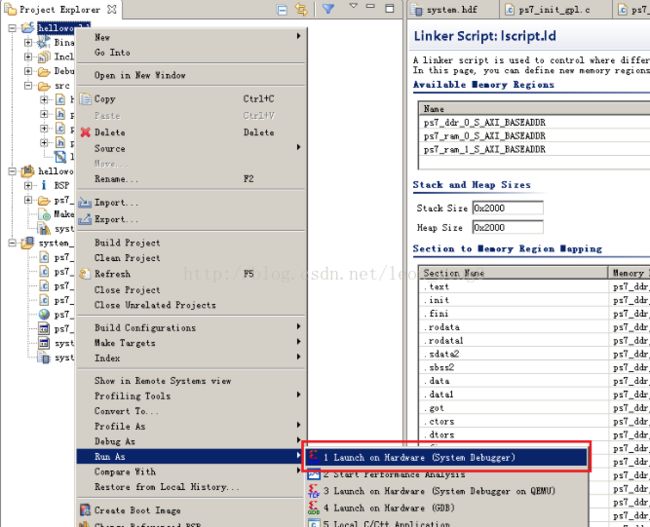

2.在SDK里右键选择helloworld工程,再选择Run as->1. Launch on Hardware (sysntem Debugger)。

这一步用户也可以选择Debug as->1. Launch on Hardware (system Debugger),然后进入调试界面,再单步执行(Step Over或F6)来调试程序。具体操作大家慢慢去琢磨。

至此,整个实验就完成了。我的实验是在黑金的学习板和核心板上完成的,最开始学习也是依照黑金的教程。

补充:

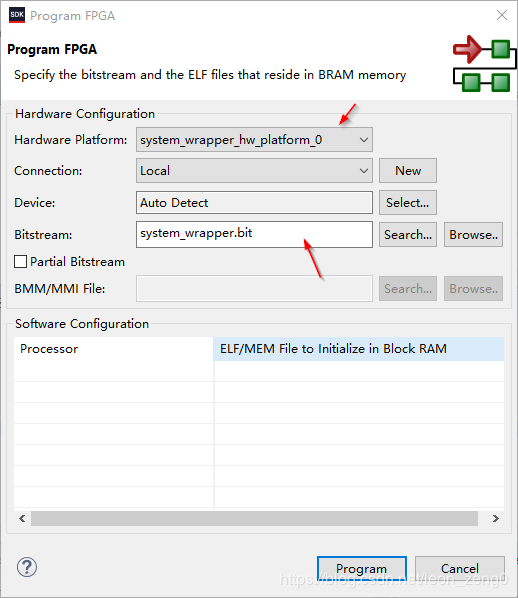

在debug 前应该下载或者说programm FPGA,并且进度条准确完成才可以debug。如下图:

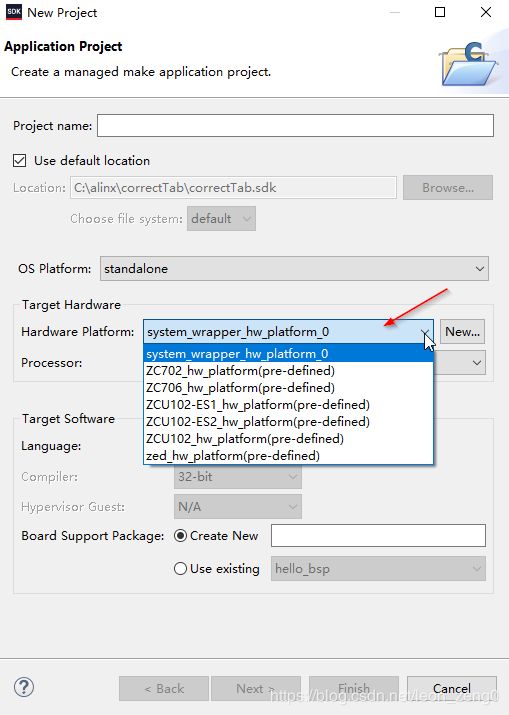

新建工程时要注意 hardware Platform 的选择。我记得2015版本的时候没问题,2018时他给你另选了,必选一下正确的设置才可以。