计算机组成与结构复习整理(五)

指令系统与中央处理机组织

- 指令系统

- 基本概念

- 指令格式

- 一般格式

- 按指令所包含的地址个数将指令划分

- 指令长度

- 寻址方式

- 指令类型

- 指令类型

- 堆栈和堆栈存取方式

- 中央处理机组织

- CPU的三种实现方式

- CPU中的主要寄存器

- 单总线数据通路

- CPU四项基本功能

- CPU时序控制方式

- CPU控制流程

- 一条完整指令的执行

- ①Add (R3),R1

- ②无条件转移指令的控制序列

- CPU性能设计

指令系统

基本概念

①程序员用各种语言编写的程序最后要翻译(解释或编译)成以指令形式表示的机器语言以后,才能在计算机上运行。计算机的指令有微指令、机器指令和宏指令之分。微指令是微程序级的命令,属于硬件;宏指令是由若干机器指令组成的,属于软件;机器指令介于二者之间,因而是硬件和软件的界面。

②一台计算机能执行的机器指令的集合统称位该机的指令系统。

指令格式

一般格式

| 操作码 | 地址码 |

|---|---|

| OP | D |

按指令所包含的地址个数将指令划分

a.三地址指令:(D1)OP(D2)→ D3

b.二地址指令:(D1)OP(D2)→D2

c.单地址指令:(D)OP (A)→ A(累加寄存器)

d.零地址指令:空操作、停机

指令长度

选取原则:

①指令长度应为存储器基本字长的整数倍。

②指令字长应尽量短。

寻址方式

①立即寻址:| OP | 操作数地址 |

②直接寻址:| OP | @间接地址 |

③间接寻址:| OP | Rx | D |

④变址寻址:| OP | Rb | D |

⑤基址寻址:

⑥相对寻址

⑦隐含寻址方式:

⑧其他寻址方式:

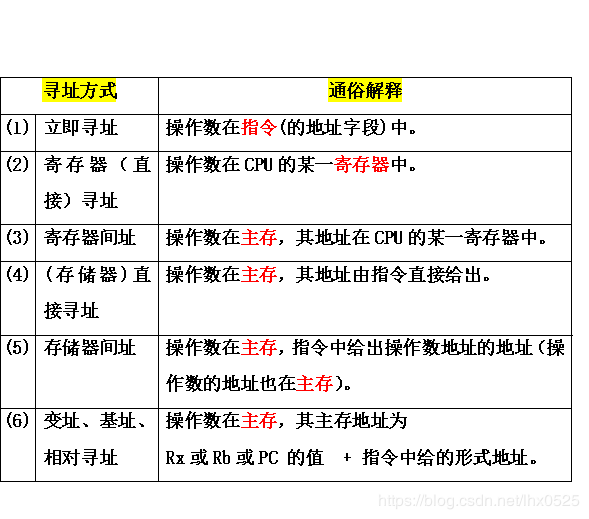

小结:

指令类型

设计一台计算机的指令系统的功能时,须考虑的几个原则:兼容性、完备性、均匀性、可扩充性。

指令类型

设计一台计算机的指令系统的功能时,须考虑的几个原则:兼容性、完备性、均匀性、可扩充性。

堆栈和堆栈存取方式

(1)寄存器堆栈:由若干移位寄存器构成,采用下压式进栈方式。

(2)存储器堆栈:内存中开辟堆栈区,存储单元固定,而栈顶位置动态变化。在CPU中专门设置了堆栈指针SP,指示栈顶位置,存取只能在栈顶进行。

入栈操作:①SP-1→SP ②存入数据→(SP)

出栈操作:①(SP)内容读出 ②SP+1→SP

入栈操作:①SP+1→SP ②存入数据→(SP)

出栈操作:①(SP)内容读出 ②SP-1→SP

中央处理机组织

CPU的三种实现方式

CPU的三种实现方式:组合逻辑、PLA、微程序控制。

CPU中的主要寄存器

指令寄存器(IR)、程序计数器(PC)、地址寄存器(AR)、缓冲寄存器(DR)、累加寄存器(AC)、状态条件寄存器(PSW)

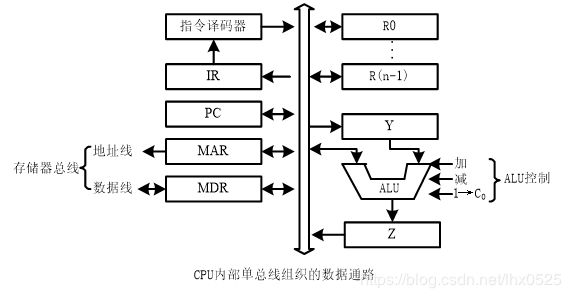

单总线数据通路

CPU四项基本功能

A.读取某一主存单元的内容,并将其装入某一个CPU寄存器;

(1) MAR←[R1] R1out, MARin

(2) Read Read

(3) WMFC WMFC

(4) R2←[MDR] MDRout,R2in

B.把一个数据字从某一CPU寄存器存入某个给定的主存单元;

(1) MAR←[R1] R1out, MARin

(2) MDR←[R2] R2out, MDRin

(3) Write Write

(4) WMFC WMFC

C.把一个数据字从某一CPU寄存器送到另一个寄存器或ALU;

R4 ←R1 R1out, R4in

D.进行一个算术运算或逻辑运算,将结果送入某一CPU寄存器。

(1)Y ←[R1]; R1out, Yin

(2)Z←[R2]+[Y]; R2out, Add, Zin

(3)R3 ←Z; Zout, R3in

CPU时序控制方式

(1)同步控制方式:同步控制方式的时序信号通常由周期、节拍和脉冲组成。指令的运行过程分为取指令、读取操作数及执行三个基本工作周期。

(2)异步控制方式

(3)联合控制方式

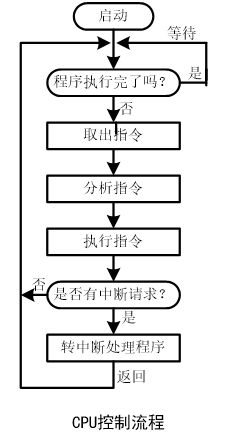

CPU控制流程

(1)取出指令

(2)分析指令

(3)执行指令

(4)对异常情况和某些请求的处理

一条完整指令的执行

①Add (R3),R1

执行这条指令需要下列动作:

(1)取指令;

(2)取第一个操作数(由R3所指出的存储单元的内容);

(3)完成加法运算;

(4)结果存入R1中。

| 步 | 操作 | 说明 |

|---|---|---|

| 1 | PCout,MARin, Read,Clear Y,1→C0,Add, Zin | 取指,(PC)+1 |

| 2 | Zout,PCin,WMFC | (PC)+1→PC |

| 3 | MDRout,IRin | 指令 → IR |

| 4 | R3out,MARin,Read | 取数据 |

| 5 | R1out,Yin,WMFC | (R1) → Y |

| 6 | MDRout,Add,Zin | 相加 |

| 7 | Zout,R1in,End | 结果 →R1 |

②无条件转移指令的控制序列

| 步 | 动作 |

|---|---|

| 1 | PCout, MARin, Read, Clear Y, 1 → C0, Add, Zin |

| 2 | Zout, PCin,WMFC |

| 3 | MDRout,IRin |

| 4 | PCout,Yin |

| 5 | (IR的偏移字段)out, Add, Zin |

| 6 | Zout, PCin, End |

CPU性能设计

决定CPU性能最重要的三个因素:指令的功能强弱、时钟周期的长短、执行每条指令所需时钟周期数。

(1)多总线组织

(2)指令流水

(3)指令发射与完成策略

(4)动态执行技术

(5)一个完整的CPU