Cadence 16.6基本操作技巧

都是工作上碰到的需要学习的知识,比较实用。

1、修改Pin脚网络

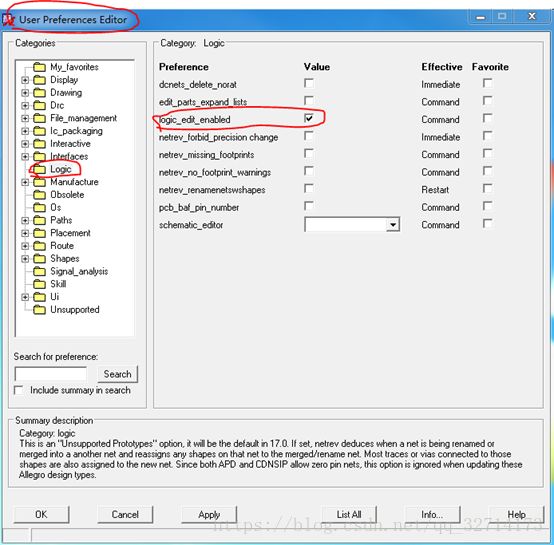

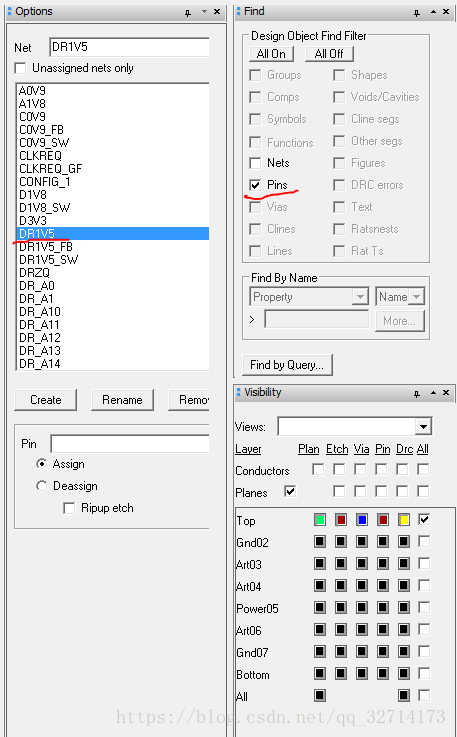

set up --user preference Editor

Logic--net logic

Option处选择网络,然后find处选择Pins,之后点击要修改网络的Pin即可将原来的网络修改为所选择的网络。

2、在使用测量工具的时候,在Find处选择对象就一定会吸附到该对象中心,否则就可以选择任意位置。

3、交换两个器件的位置

Place--Swap--Components

4、走线的模式

在走线状态下,option状态栏下的bubble选项:

off--走线的时候基本使用这种模式。

hug only 推挤走线的时候只是hug不会移动走线。

shove preferred推挤走线的时候会移动已经走好的线和过孔,不推荐这种模式。

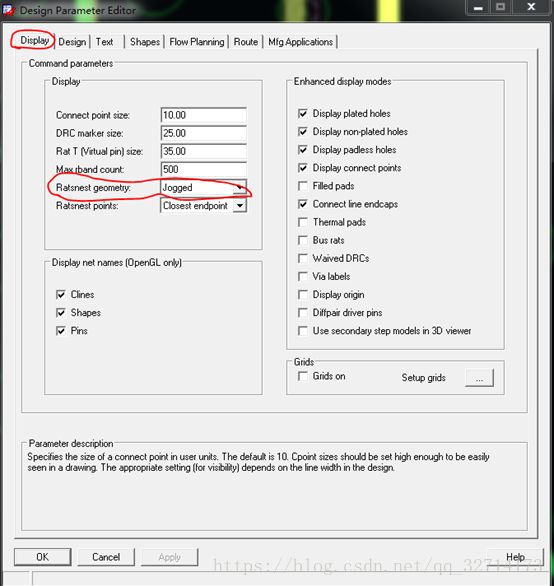

5、改变飞线布线模式

有jogged和straight模式。

Jogged:当飞仙呈水平或者垂直时自动显示有拐角的线段。

Straight:最短的直线段。

(因为之前用的AD所以一直习惯直线段的飞线模式,但是后来习惯之后还是觉得jogged的模式更合理。)

6、内电层敷铜

叠层设置好之后,该层是没有铜皮的,需要自己敷。(AD是设置完叠层就有了)

先画一块在route keepin层的铜皮,这相当于设置了可以布线的区域,之后画的铜皮都会在这个框里面,当然走线也不能超出这个框。

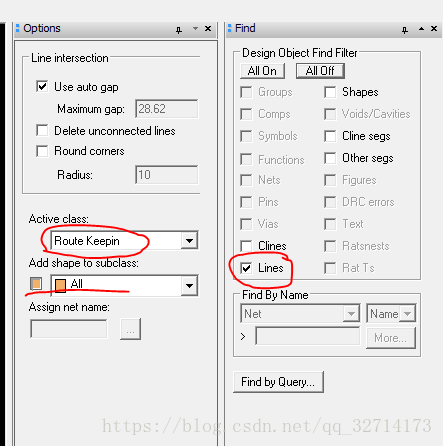

具体流程:

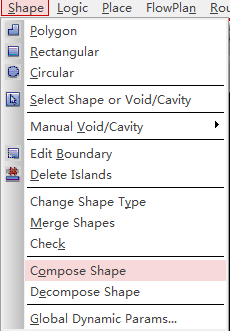

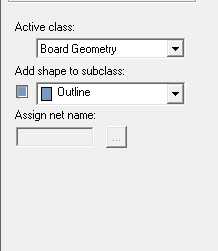

a、只打开board outline层

b、shape --compose shape,options和find处设置如下图设置完之后直接画一个大于outline层的框即可。

Find处只需要选择line,不需要选择其他。

有时候你框选了但是route keepin的shape没有出来。是因为你的outline处于fix状态,解锁之后就可以了。

c、选择外框,右键选择expand/contract,需要缩进20mil。

d、之后设置层数和网络直接铺一整块铜皮即可。铜皮基本选择dynamic模式。

7、绕T型等长

A、打开CM进行如下设置

选择F1_DQS,右键creat-pin pair,则出现右边的选项框。First pin可以理解为源端,second可以理解为负载端,在T形网络中, 一个源端最多可以对应四个负载端,等长即从源端到每个负载端的长度一样。

设置好pin pair之后按ok会出现这个警告,意思是设置完pin pair之后必须马上设置规则,否则过一段时间,设置的pin pair会消失,得重新设置。

B、将F0的DQS、DQSN、DQ0~7、RE、REN选择好pin pair之后,就可以设置match group。

需要将每个pin pair选中之后再右键creat-match group。如下图。(不要直接点网络创建match group,一定要点pin pair)

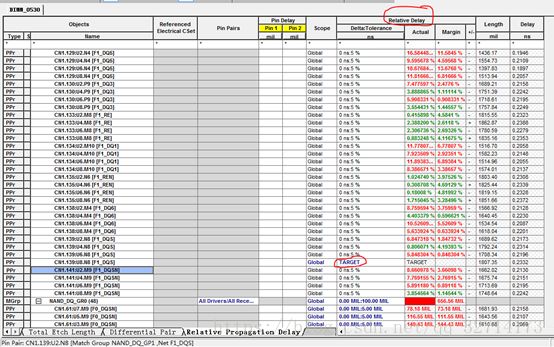

C、match group设置好之后,设置等长基准,这边以DQS为基准(选择其中一个即可),右键set as target。然后在其他单元格设置允许误差的范围。然后后面红色的数据表示超出范围,绿色的数据表示在范围内。

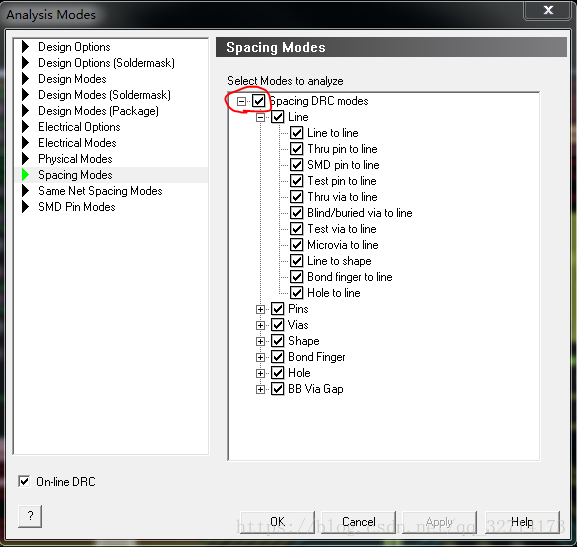

打开检查模式。Setup--constraint--modes

这个一定要打开,不然规则里面relative delay出不来,即如下图所示3列是没法显示的。

D、之后就手动绕等长。

1)![]() 这个是走蛇形线。Options如下设置。(差分最好走5W线宽)

这个是走蛇形线。Options如下设置。(差分最好走5W线宽)

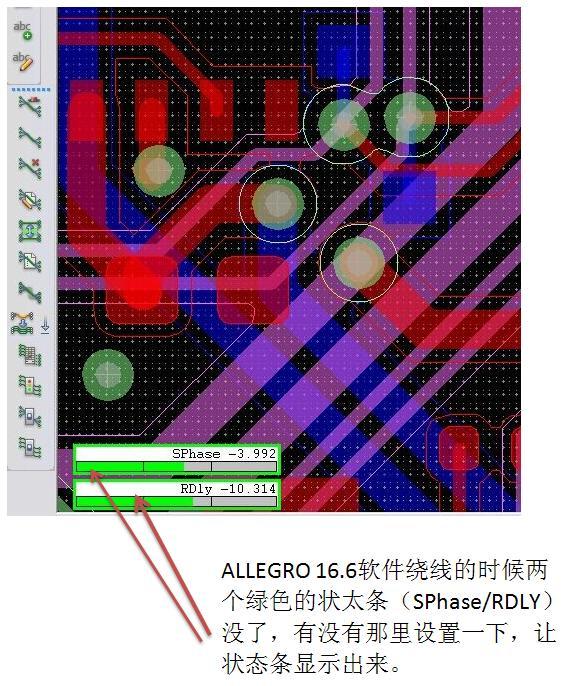

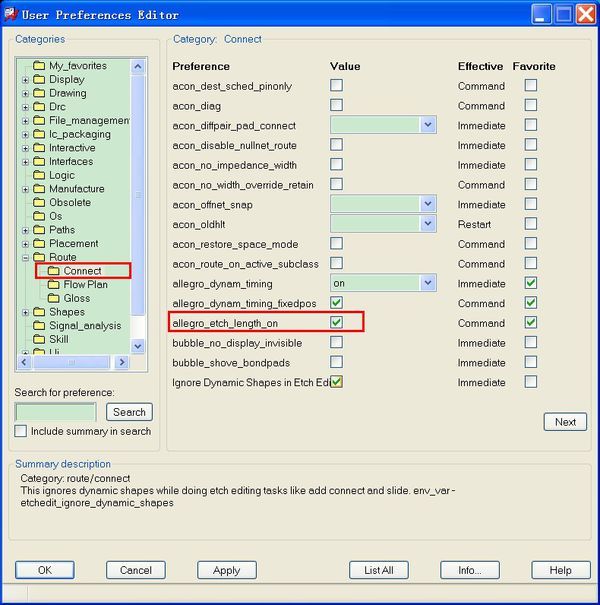

2)状态条没有显示了(摘录自网上)

F 、T型第一根引出的线可以走的比较长,但是延展到其他四个端点的线最好能走直线不要绕。虽然延伸出去的线是高阻状态, 但是它会有反射,先越长反射越大,所以尽量走短线。。

![]() net schedule,点击这个,点击想要查看的网络,可以查看从s端到d端的飞线。

net schedule,点击这个,点击想要查看的网络,可以查看从s端到d端的飞线。

顺序是先让T区两端的线保持一样长,总长误差5mil以内的,比如DQS和DQSN这两根线,两端线的误差就要在1mil以内。 总长误差在100mil以内的,两端线的误差可以适当长一点。

绕的之后掌握的技巧:

先看一下这一个match group里面的线差距怎么样,然后找一个适当的长度,将基准线调成这个长度,然后先将误差比较小的线完成,之后绕误差相对可以大一点的。(一开始先调了基准线导致后面有些线无法缩小,之后得将所有线整体饶长)

G、饶等长比较方便的命令。

Route--timing vision

这个功能直接让比基准长的一种颜色,比基准短的一种颜色,绕好的显示一种颜色,直接绕就好了,不用去看规则管理器。

Route--auto-interactive delay tune

选择命令,然后框选想要等长的线就好了。

H、最近画好的板子在仿真的时候知道,等长不是根据基准DQS绕的,是需要组内所有长度误差都在30ps以内,所以一开始可以根据上述步骤调试,之后再根据仿真结果调试。30ps约等于200mil(经验值),以这个值调整出来的不会差很多。

8、关于规则的有关设置

set up--Constraints--modes

这几个参数都需要设置,具体看公司要求。

sapcing mode都需要打开,假如有些可以忽略的再waive掉。

相同网络的靠太近也会报错,这个也需要都打开。

9、导出设置

1)导出选项

File→Export→Sub-Drawing

在Find 窗口中选择需要导出的选项,可以是option里面的任何东西,比如Line/shape/cline。

2)在命令窗口输入x 0 0 (导出文件的参考基准坐标,Compelet完直接按X就可以不用去选下面的窗口,如果X被快捷键占用则使用pick)

输完坐标后,按回车,弹出保存CLP文件的窗口,将CLP文件命名保存。

3)导入选项

将CLP文件放到需要导入的文件的当前目录下

File→import→Sub-drawing选中需要导入的CLP文件

输入基准坐标(想导入到哪个坐标,就输入什么坐标,基本为 x 0 0)

回车完成导入。

PS:要在两个PCB中相互导入Line/shape/cline需要两个文件的叠层层数和各层的名字一致,一般的操作,会将导出的文件的叠层改成和要导入的文件一致,如果要导入via,还需要在要导入的PCB的中也有这个via的路径

10、铜皮不能自动更新

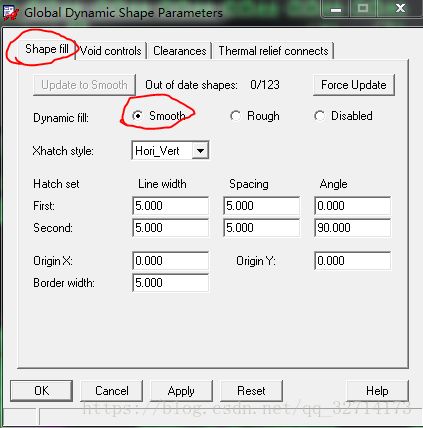

铜皮属性是dynamic copper,但是修改的过程中他不会自动更新。可以选择shape--global dynamic shape parameters(这边改动之后所有铜皮都会修改为相应的设置)

将dynamic fill设置为smooth即可。

11、修改Shape属性的outline

首先关闭其他东西,直留一个outline。

然后shape--decompose shape,在option那边选择board geometry --outline。

最后框选住整个outline就会变成board geometry属性的outline了。

12、铜皮显示修改

调高之后就可以正常显示,上图我总觉得和静态铜皮一样。

13、画弧形线

Route--unsupported prototypes--auto-interactive convert corner

然后点击需要变弧形的线就可以变成一条弧形线。

14、工程性问题

PCB完成后需要检查一下NPTH(非金属化孔)是不是有金属连接,有金属连接都需要改成PTH(金属化孔)。另外,NPTH也需要加上solder mask,假如不加板厂默认是塞孔。

在建通孔pad或者Via时也把公差加上,都按+/-4mil就可以了,安装孔和插接孔,只能大不能少,避免因为公差原因无法安装。(在出NC drill那边修改)

调整字符时需要打开对应层的Solder mask和焊盘,宁愿删除也不要压到Solder mask上,所有的封装制作时都需要对应的Assembly层丝印,以免删除Silkscreen后没有备用。

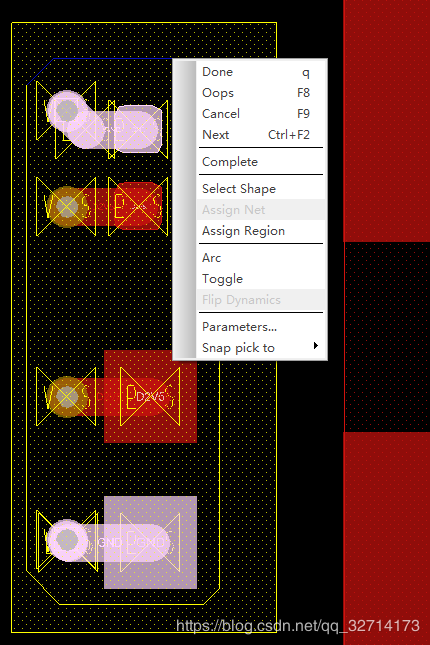

15、snap pick to

这是一个很好用的操作,先选择一个命令,比如移动或者复制,然后鼠标移动到想到操作的目标附近,右键选择snap pick to。 (segment vertext为线段顶端,比较常用)之后目标会吸附在光标上,将目标移动到相应位置,再右键选择snap pick to,至此操作完成。

在shape edit boundary时也很有用,因为假如铜皮的端点不在格点上的话是选中不了的,这个时候就可以选择snap pick to--segment vertsxt,这样就可以很容易的选中铜皮的端点。

16、更换via的网络

需要使用EDA365 skill

3、route tools--change via’s net

出现以下对话框,点击pick

然后点击相应网络,done。

再选择select,点击相应过孔,done

17、Waive DRC

Waive DRC之后还会显示是因为waive掉的DRC是在show的状态下。

选择display--waive DRCs--blank即可关闭。当然选择show可以开启,在最后检查的时候可以选择show再检查一遍waive掉的DRC是否没有影响。

18、铜皮过BGA

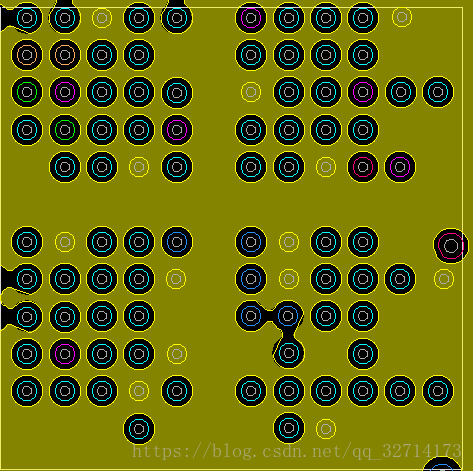

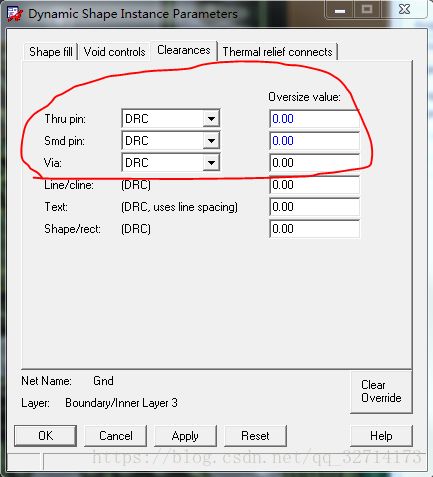

敷铜过bga的时候会遇到以下问题

这样的铜皮比较参考性就不是很好了。可以设置以下参数,shape select--选中铜皮右键--parameters即可出现以下对话框。

将红圈标注位置设置为3.5即可变成下图所示

这样铜皮就相对比较完整。

需要说明一下这边的参数是在规则管理器设置的参数上面再额外加的。

比如假如在规则里面设置shape to via的间距为4mil,然后又在parameters 这边设置via的间距为4mil,那么实际上shape to via的间距会变为8mil。

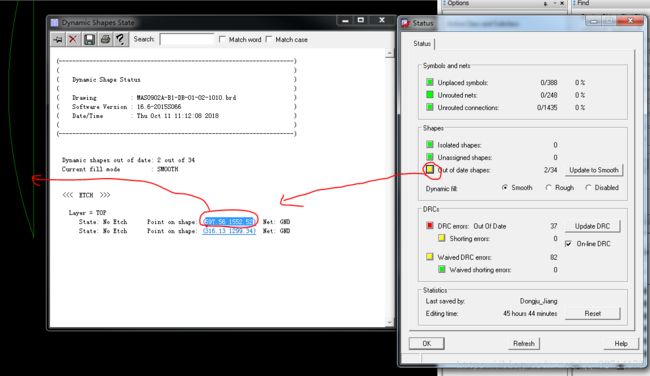

19、update to smooth

有的时候不能update to smooth,因为只有一个外框但是没有填充的shape是删除不了的。这个时候可以关闭所有图层然后打开bound。

点击out of data shape前面那个小框,会出现对应没删除铜皮的坐标,点击坐标即可跳转到相应的铜皮,删除即可。

20、复用布局和走线

选择placement edit模式

选择除group之外其他的选项,框选需要复用的布局,右键(需要选中元器件右键)place replicate create,在空白处右键done,会自动跳出需要保存的文件,命名后保存即可。

然后选择还未布局的元器件(划重点!必须是一模一样,有一点不一样都会导致复用布局出错),右键(需要选中元器件右键,其他位置右键不会出来相应选项)place replicate apply,选择刚才保存的文件即可。

复用一遍之后有改动需要再次复用时,需要先在placement edit 模式下选择group,然后右键disband group。然后再按之前的步骤即可复用。

这个技巧操作过程中可能会出挺多错,有时候也会有元器件对不上的情况,但是你多试几遍熟悉了之后就会觉得挺方便的。

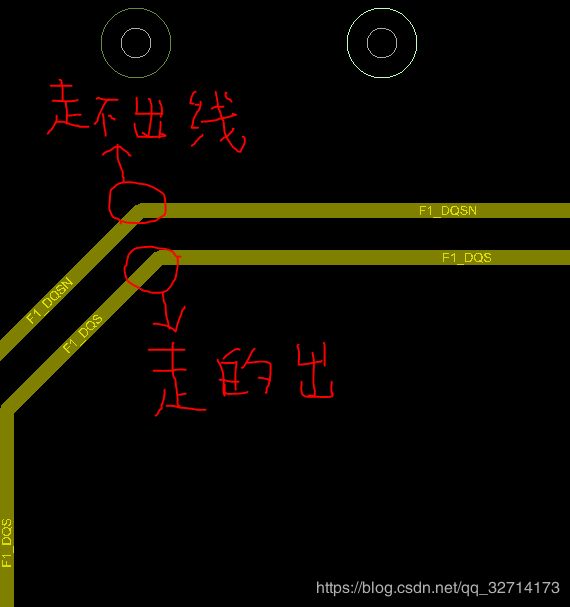

21、 调整差分线

调整差分线的时候,即用连线命令在差分线拐角位置开始走线,外围的那根线会有走不出来的情况。这是因为拐角外围的那个点内围没有与他平行的点,但是内围的线在外围有对应的平行点,所以内围那根线可以走出线。

除此之外,option那边的bubble必须设置为off。不然也是不行的。

22、移动命令的option选项

Ripup etch(rip up:撕毁、取消):移动元器件的时候会有飞线,并且移动之后,元器件上面原本的走线会消失。

Slide etch(slide:滑动):移动元器件的时候没有飞线,移动的时候,元器件上面的走线会一直相连,并且走线是以45°的形式变化。

Stretch ecth(stretch:延展):移动元器件的时候没有飞线,移动的时候,元器件上面的走线会一直相连,但是走线是以无角度约束的变化。

假如上面三个都不选的话,移动的时候会有飞线,而且线不会有变动。

rotaion那边有三个选项,分别是type,angle和point。

type里面有两个选项,absolute是绝对的意思只能旋转一次,incremental是持续的意思能够不停的旋转。

angle是角度,但是设置45°的时候,只能是右键旋转才能使用,貌似用快捷键只能旋转90°(因为快捷键设置的时候是旋转90°)。

point那边是在旋转的时候以什么为基点,想要选中的所有元器件一起旋转并且不改变布局,是用user pick。

在此说明以下技能均是EDA365网站所学习到的。

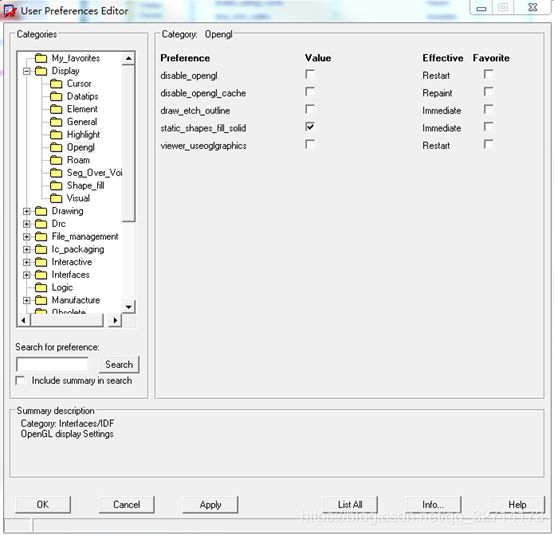

23、静态铜实心显示(但还是网格显示看着舒服,并且与动态铜有一个区分)

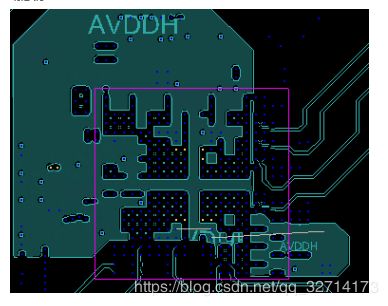

24、铜皮设置

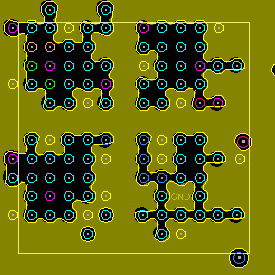

假如设置in-line的话,隔得近的孔之间的铜皮会没掉,比如下图这样:

25、静态铜的手动避让

选择一个画manual void的方式,就可以画一个框将需要避开的过控或者焊盘避让开。

因为动态铜避让之后内部会很不平整,所以用这个方法还是很不错的。

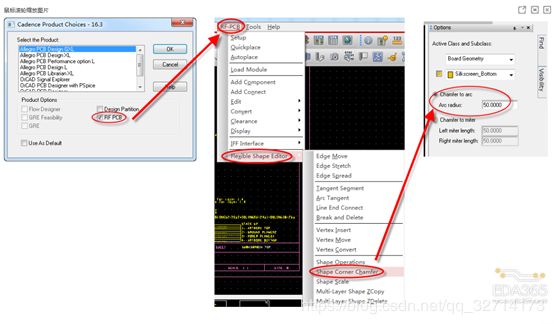

26、修改铜皮拐角为圆弧

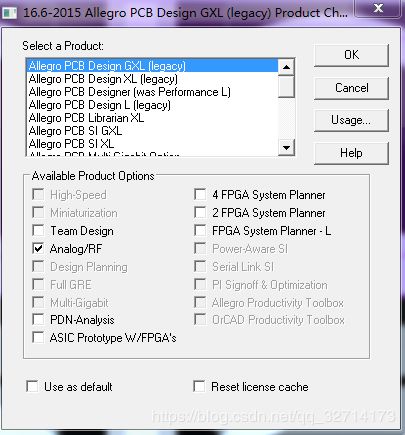

关于16.6版本是稍微有些修改

是选择nanlog/rf

半径设为5比较合适。

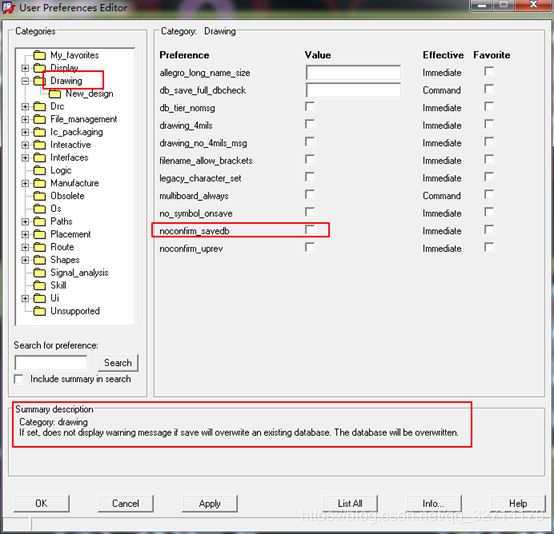

27、allegro保存时,如果名字相同,不会提示覆盖文件

28、调整线间距

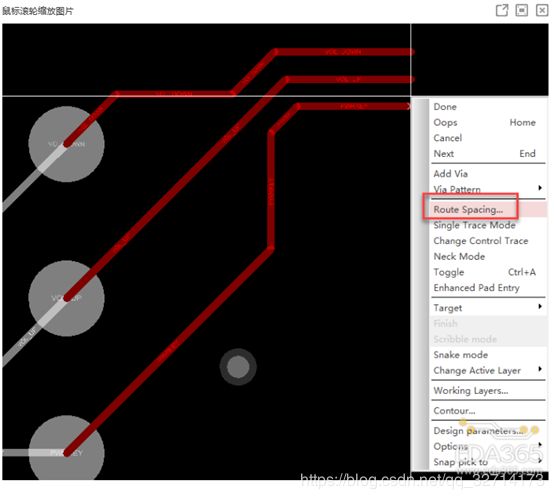

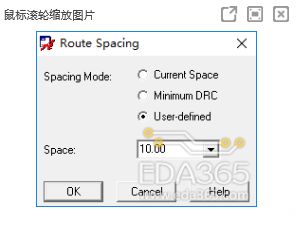

布线过程中可以控制,框选中一组线后,用右键菜单中的route spacing功能设置好间距就可以均匀布线了。

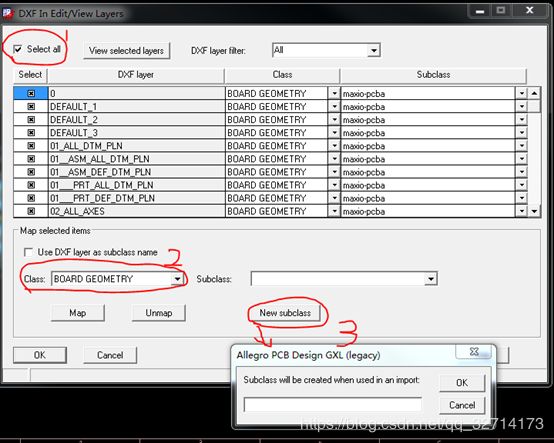

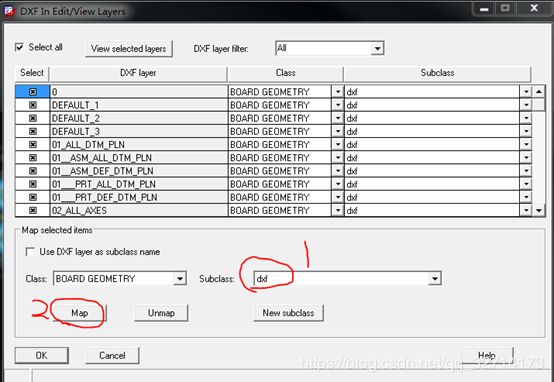

29、allegro导入dxf(这个是自己总结的)

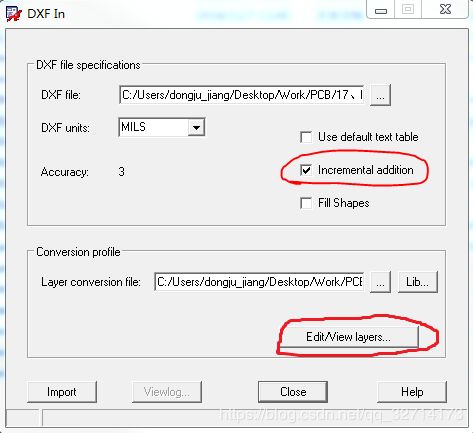

File—import—dxf

假如没有勾选incremental addition,dxf导进去之后之前的内容都会消失。然后点击edit/view layers

按照上述步骤,创建一个新的subclass,创建好之后map一下,点击ok,返回之前的对话框,就完成了dxf的导入。

之后可以在color dialog打开看一下导入的是否正确。

之后还需要将dxf中的外框部分转化为outline

之后就是将outline选中,因为线是一段一段的,所以需要单击点过去将它们连起来。如图中蓝色部分。

30、删除via内层的焊盘

需要删除内层焊盘的原因是增大敷铜面积,由于via删除内层焊盘之后,在内层就相当于hole,所以需要重新设置hole到via以及hole到line的距离,具体数值需要跟板厂确认。层数和铜厚都会影响这个数值的大小。

set up--unused pads suppression

将pin和vis的框都选中,再将dynamic unused pads suoression 和display padless hole(选中这个,在去点去掉内层焊盘的via时可以有一个虚框存在)勾上

到此为止,以后估计不会再更新了。