- 大模型的webui

Zain Lau

人工智能python昇腾Ascend天数

exportXXX_LLM_C=~/xcore-llm/build/ReleaseexportCUDA_VISIBLE_DEVICES=2,3exportCUDACXX=/usr/local/cuda-12.3/bin/nvccnohup/usr/bin/python3/home/src/api_server/api_server.py--modelLLama2:7b-chat-hf_A800--

- PCDN 与边缘计算的结合:未来内容分发的新趋势

yczykjyxgs

pcdn智能路由器

在数字化浪潮中,内容分发面临着前所未有的挑战与机遇。PCDN(P2P内容分发网络)与边缘计算的结合,正逐渐崭露头角,成为未来内容分发的新趋势。PCDN通过P2P技术,利用用户节点的闲置资源进行内容分发,有效减轻了中心服务器的压力,降低了传输成本。然而,在面对实时性要求极高的业务场景时,PCDN仍存在一定局限。边缘计算的出现,为解决这一问题提供了新思路。边缘计算将计算和存储能力下沉到网络边缘,靠近用

- IIS网站用myssl评级为B级

bigsea76

windowsssl

不光是IIS网站,包括.net使用HttpListener开发的web程序,在默认情况下都会被评为B级。提示为:降级原因:1.没有使用AEAD系列加密套件,降级为B2.没有优先使用FS系列加密套件,降级为B。我现在知道AEAD系列加密套件指的是那些支持认证加密和关联数据(AuthenticatedEncryptionwithAssociatedData)的套件,比如AES-GCM和ChaCha20

- Redis 常用数据类型

27xixi

java技术栈redis数据库缓存

Redis常用数据类型的详细介绍及其典型应用场景:String(字符串)描述:最基本的数据类型,可存储文本、数字或二进制数据(最大512MB)。常用命令:SETkeyvalue:设置值GETkey:获取值INCRkey:将值自增1(原子性操作)EXPIREkeyseconds:设置过期时间应用场景:缓存简单键值对(如用户会话、配置项)。计数器(如文章阅读量、库存扣减)。分布式锁(结合SETNX命令

- 复原IP地址 (leetcode 93

JohnFF

leetcode算法职场和发展

leetcode系列文章目录一、核心操作二、外层配合操作三、核心模式代码总结一、核心操作判断字段是否有效函数:首先start不能大于end当到最后一个收获层的时候,start已经是s.size了,但是end还是只能是s.size-1其次当字段不止一位时,start不能是0,然后再循环判断每一位是不是处于字符‘0’和‘9’之间,以及通过num*10+当前数字的操作求出值,判断是不是大于255回溯函数

- Redis 源码分析-内部数据结构 quicklist

笨手笨脚の

#Redisredis数据结构数据库quicklist链表快速链表ziplist

Redis源码分析-内部数据结构quicklistquicklist是Redis对外暴露的list数据结构的内部实现,经常被当作队列或栈使用,我们可以从常用的一些api上先思考一下它的结构最常用的就是lpush、lpop、rpush、rpop,同时它也支持lindex查询某元素在list中的索引,linsert在指定元素旁边插入新元素。从头、尾节点的push、pop来看,这就是双向链表最优秀的设计

- 【云原生】动态资源分配(DRA)深度洞察报告

碣石潇湘无限路

云原生

1.DRA的发展与设计灵感Kubernetes早期通过DevicePlugin(设备插件)机制支持GPU、NIC等特殊硬件,将节点上可用设备数量上报给kubelet和调度器。但设备插件模式存在局限:调度器只能根据节点标签等属性粗粒度筛选,无法精准指定某型号/属性的设备;此外调度器与设备插件缺乏联动,可能把Pod调度到尚未准备好相应设备的节点上。结果就是难以满足复杂场景下对特定硬件的精细化需求。为解

- iptv内容运营系统服务器架构,IPTV系统架构技术的深入解析

Damong.Liu

iptv内容运营系统服务器架构

IPTV简单来说就是交互式网络电视,它能为用户提供电信级的服务和使用简便的电视式体验。IPTV业务是伴随着宽带互联网的飞速发展而兴起的一项新兴的互联网增值业务,它利用宽带互联网的基础设施,以家用电视机和电脑作为主要终端,利用网络机顶盒(STB,Set-TopBox),通过互联网协议来传送电视信号,提供包括电视节目在内的多种数字媒体服务。IPTV系统概述到目前为止,IPTV虽然还没有一个十分明确的定

- 开源应用驱动企业新质生产力:Websoft9以EPP+AI+知识库助您领跑未来.

人工智能

开源应用驱动企业新质生产力:Websoft9以EPP+AI+知识库助您领跑未来在数字化转型加速的今天,企业新质生产力的核心已从传统资源投入转向技术驱动的效率革命。开源应用凭借其灵活性、成本优势和技术创新力,成为企业实现这一目标的关键引擎。作为开源技术与行业场景化落地的领航者,Websoft9通过企业应用平台(EPP)、AI智能引擎与知识库系统三位一体的解决方案,助力企业快速构建新一代生产力工具,实

- mysql安装启动报错_mysql安装/启动报错汇总

weixin_29179583

mysql安装启动报错

2016/9/6补充初始化报错:#/usr/local/mysql/scripts/mysql_install_db--user=mysql--basedir=/usr/local/mysql/--datadir=/data/mysqldb/InstallingMySQLsystemtables...2016-09-0617:29:160[Warning]TIMESTAMPwithimplicit

- 【机器学习】基于t-SNE数据可视化工程

无水先生

AI原理和python实现人工智能综合人工智能算法

一、说明t-SNE(t-DistributedStochasticNeighborEmbedding)是一种常用的非线性降维技术。它可以将高维数据映射到一个低维空间(通常是2D或3D)来便于可视化。Scikit-learnAPI提供TSNE类,以使用T-SNE方法可视化数据。在本教程中,我们将简要学习如何在Python中使用TSNE拟合和可视化数据。二、t-SNE是个什么?2.1什么是t-SNE?

- Flutter 自定义年月日倒计时

xudailong_blog

Flutter开发flutter倒计时年月日android

因项目中的订单页需要一个定时器,比如下单后需要进行倒计时,等倒计时完后,订单状态自动关闭。如图:这里显示等17分25秒就是我们所需要做的功能。项目里还有其他倒计时类型,比如年月日,天之类的,先上一个工具类://时间格式化,根据总秒数转换为对应的hh:mm:ss格式staticStringconstructTime(intseconds){intday=seconds~/3600~/24;intho

- 计算机系统04 - Unicode 和 UTF-8

是小崔啊

#计算机组成原理计算机组成原理

Unicode和UTF-8文章目录Unicode和UTF-8什么是字符编码什么是字符?什么是字符集认识Unicode字符集为什么要使用Unicode字符集Unicode编码标准Unicode编码格式UTF-8编码UTF的字节序问题总结什么是字符编码什么是字符?字符(Character)是对文字和符号的总称,例如汉字、拉丁字母、emoji都是字符。在计算机中,一个字符由2部分组成:1、字符的编码:字

- 前端开发:Web蜜罐详解

三掌柜666

前端网络安全

前言在当今数字化时代,网络安全威胁日益复杂,攻击手段层出不穷。对于前端开发人员来说,不仅要关注代码的性能和用户体验,还需要具备应对安全威胁的能力。在网络安全领域,Web蜜罐作为一种主动防御技术,正逐渐受到关注,它通过模拟真实的Web应用程序,吸引攻击者并记录其行为,为安全专家提供了宝贵的情报。对于前端开发人员来说,了解Web蜜罐的工作原理、特点和应用场景具有重要意义。那么本文就来探讨Web蜜罐的工

- Qt 为窗体设置透明图标

log159

qt开发语言

Widget构造,继承自QWidgetQImageimage(QSize(10,10),QImage::Format_ARGB32);image.fill(Qt::transparent);QPixmaptempPixmap=QPixmap::fromImage(image);this->setWindowIcon(QIcon(tempPixmap));

- springboot集成钉钉_钉钉通知机器人与SpringBoot的集成

weixin_39622643

springboot集成钉钉

SpringBootAdmin集成自定义监控告警(2.0.1版本)------钉钉机器人-yuancao24的博客-CSDN博客https://blog.csdn.net/yuancao24/article/details/83576194prometheus-spring-boot-starter:一个管理异常通知的神奇starter,实现了钉钉消息提醒与邮件提醒https://gitee.co

- Qt之动画编程之窗体透明度效果

我不是程序员~~~~

Qt实战qtandroid开发语言

#ifndefOPACITY_WIDGET_H#defineOPACITY_WIDGET_H#include#includeclassopacity_widget:publicQWidget{Q_OBJECTQ_PROPERTY(qrealopacityREADwindowOpacityWRITEsetWindowOpacity)public:opacity_widget(QWidget*pare

- 【AI热点】MCP协议深度洞察报告

碣石潇湘无限路

人工智能php开发语言

摘要人工智能技术飞速发展,大型语言模型(LLM)如何高效、安全地利用外部数据和工具成为关键问题。模型上下文协议(ModelContextProtocol,简称MCP)是一种由Anthropic于2024年底提出的开放标准协议。它通过统一的客户端-服务器架构,为AI应用与文件系统、数据库、第三方API等外部资源之间提供标准化、安全的双向通信接口。本文将深入解析MCP协议的基本概念和背景、架构设计(通

- 【云原生】深入浅出 K8s 设备插件技术(Device Plugin)

碣石潇湘无限路

kubernetes容器云原生

摘要:Kubernetes提供了DevicePlugin机制,用于向kubelet上报硬件信息并配置容器资源。本文以NVIDIAGPUPlugin为例,通俗易懂并深入浅出地剖析注册、ListAndWatch、Allocate及kubelet管理流程,介绍常见问题和配置要点。先用一张原理概览图把DevicePlugin和kubelet之间的交互勾勒出来,让大家感受下插件技术的整体架构(示例以NVID

- 轻松管理CSV数据,Python csv库全解析

嘎啦AGI实验室

Pythonpythonandroid数据库Pythoncsv

文章目录轻松管理CSV数据,Pythoncsv库全解析背景介绍csv库是什么?如何安装csv库?五个简单的库函数使用方法1.读取CSV文件2.写入CSV文件3.使用DictReader读取CSV4.使用DictWriter写入CSV5.指定分隔符五个场景使用代码说明场景1:读取CSV并统计数据场景2:将查询结果写入CSV场景3:读取CSV并过滤数据场景4:读取CSV并排序数据场景5:读取CSV并合

- 带你拿捏哈希表

ん贤

算法哈希算法算法散列表c++java数据结构

向Carl老师学习,用最简单的话,讲述最复杂的知识。(•̀ω•́)✧什么是哈希表?灵魂一问,这是正常人看到后,都会产生的疑问,就好比你是谁。初学者可以将其看成一个数组!大家都知道数组是怎么存数据的!通过下标(0~N,是一串连续的数字),将对应数据为其赋值。哈希表大致就是这样存储的。既然如此,那为啥它不叫数组,而叫哈希表(⊙_⊙)?因为哈希表计算计算下标的时候,是通过一个名为哈希函数的工具,将key

- python中将字符串转换成数字,并且保留两位小数

上趣工作室

pythonpython后端

在Python中,你可以使用float()函数将字符串转换为数字,并使用字符串格式化来保留小数点后两位。下面是一个示例代码:defconvert_to_float(string):try:number=float(string)formatted_number="{:.2f}".format(number)returnformatted_numberexceptValueError:return"

- 【数字IC验证】博客内容全览

MoorePlus

数字IC验证百宝箱经验分享面试数字IC芯片验证SV

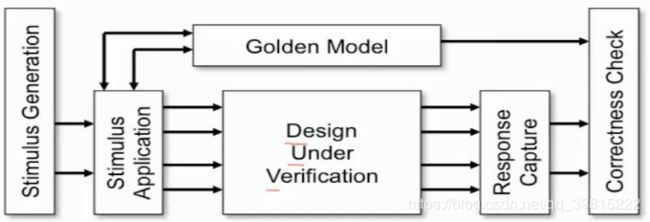

【导读】:数字IC验证百宝箱涵盖博主在实际工作中常用的技能与工具,包括但不限于SV、UVM、Formal、脚本(perl/python/shell)及EDA工具快速上手使用等。无论你是刚踏入职场的验证小白,还是希望回顾基础寻找跳槽机会的从业者,本专栏都能为你提供实用的技术支持,在达成目标的路上,助你一臂之力。“凡是能用钱买来的时间就是便宜的;凡是能用时间换来的注意力持续就是有价值的。”(附上超链接

- 论单调队列优化DP

VU-zFaith870

c++动态规划推荐算法

前情提要,参考资料:单调队列优化DP(超详细!!!)-endl\n-博客园【动态规划】选择数字(单调队列优化dp)_哔哩哔哩_bilibili背景:最近作者快被DP逼疯了,写篇博客做记录。以下是对各DP的原理阐释:单调队列通过队列元素的吸入与弹出,形成单调性的结构,使算法能够进行线性处理,大大优化了时间复杂度。接下来讲解单调队列在区间DP、背包DP、树形DP还有数位DP中的应用:1.单调队列优化区

- HIVE开窗函数

Cciccd

sqlhive

ETL,SQL面试高频考点——HIVE开窗函数(基础篇)目录标题ETL,SQL面试高频考点——HIVE开窗函数(基础篇)一,窗口函数介绍二,开窗函数三,分析函数分类1,排序分析函数:实列解析对比总结2.聚合分析函数3.用spark自定义HIVE用户自定义函数后续更新中~一,窗口函数介绍窗口函数,也叫OLAP函数(OnlineAnallyticalProcessing,联机分析处理),可以对数据库数

- Hive MR & Spark & Yarn参数优化总结

大数据侠客

hive相关问题汇总及解决hivesparkmryarn参数优化

一、hivemr参数调优:sethive.optimize.ppd=true;--开启谓词下推。--动态分区参数sethive.exec.mode.local.auto=true;sethive.exec.dynamic.partition.mode=nonstrict;--默认是strict,表示至少有一个静态分区,nonstri

- C++面向对象三大特性

CodeCuriosity

C++c++开发语言

一、封装封装是将数据和操作数据的函数捆绑在一起形成类,通过访问控制限定符(如private、protected、public)隐藏对象的内部细节,仅对外提供必要接口,以此增强代码的安全性和可维护性。#includeclassBankAccount{private:doublebalance;//私有成员变量,外部无法直接访问public://构造函数,用于初始化账户余额BankAccount(do

- hive 中优化性能的一些方法

闯闯桑

hivehadoop数据仓库

在ApacheHive中,性能优化是一个重要的课题,尤其是在处理大规模数据时。通过合理的优化方法,可以显著提升查询速度和资源利用率。以下是一些常见的Hive性能优化方法:1.数据存储优化1.1使用列式存储格式推荐格式:ORC和Parquet。优点:列式存储格式具有更高的压缩率和查询性能。支持谓词下推(PredicatePushdown)和列裁剪(ColumnPruning)。示例:CREATETA

- 远程推送didReceiveRemoteNotification代理方法调用详细说明

Ethan. L

iOS开发UIApplication远程推送代理

前言最近工作中实现远程推送点击状态栏的提醒,直接进入相应地详细界面的功能。遇到了问题,解决之后整理出来!UIApplication有两个关于接收到远程推送的代理:-application:didReceiveRemoteNotification:fetchCompletionHandler:-application:didReceiveRemoteNotification:这两个是什么关系?点击远

- SDN技术解码:架构革新与数字化转型实践指南 ——从控制平面到AI融合的网络进化论

不想加班的码小牛

架构平面人工智能网络协议

一、引言:SDN如何重塑网络价值体系?在数字化浪潮下,传统网络架构的僵化性已成为制约业务创新的瓶颈。SDN(软件定义网络)通过解耦控制与转发平面,将网络从“黑盒设备”转变为“可编程服务”,为云计算、物联网等领域提供动态、智能的网络底座。例如,某金融企业通过SDN实现跨地域数据中心流量智能调度,业务故障恢复时间缩短至分钟级。二、SDN核心架构与技术原理1.三层架构:控制-转发-应用的协同生态•控制层

- knob UI插件使用

换个号韩国红果果

JavaScriptjsonpknob

图形是用canvas绘制的

js代码

var paras = {

max:800,

min:100,

skin:'tron',//button type

thickness:.3,//button width

width:'200',//define canvas width.,canvas height

displayInput:'tr

- Android+Jquery Mobile学习系列(5)-SQLite数据库

白糖_

JQuery Mobile

目录导航

SQLite是轻量级的、嵌入式的、关系型数据库,目前已经在iPhone、Android等手机系统中使用,SQLite可移植性好,很容易使用,很小,高效而且可靠。

因为Android已经集成了SQLite,所以开发人员无需引入任何JAR包,而且Android也针对SQLite封装了专属的API,调用起来非常快捷方便。

我也是第一次接触S

- impala-2.1.2-CDH5.3.2

dayutianfei

impala

最近在整理impala编译的东西,简单记录几个要点:

根据官网的信息(https://github.com/cloudera/Impala/wiki/How-to-build-Impala):

1. 首次编译impala,推荐使用命令:

${IMPALA_HOME}/buildall.sh -skiptests -build_shared_libs -format

2.仅编译BE

${I

- 求二进制数中1的个数

周凡杨

java算法二进制

解法一:

对于一个正整数如果是偶数,该数的二进制数的最后一位是 0 ,反之若是奇数,则该数的二进制数的最后一位是 1 。因此,可以考虑利用位移、判断奇偶来实现。

public int bitCount(int x){

int count = 0;

while(x!=0){

if(x%2!=0){ /

- spring中hibernate及事务配置

g21121

Hibernate

hibernate的sessionFactory配置:

<!-- hibernate sessionFactory配置 -->

<bean id="sessionFactory"

class="org.springframework.orm.hibernate3.LocalSessionFactoryBean">

<

- log4j.properties 使用

510888780

log4j

log4j.properties 使用

一.参数意义说明

输出级别的种类

ERROR、WARN、INFO、DEBUG

ERROR 为严重错误 主要是程序的错误

WARN 为一般警告,比如session丢失

INFO 为一般要显示的信息,比如登录登出

DEBUG 为程序的调试信息

配置日志信息输出目的地

log4j.appender.appenderName = fully.qua

- Spring mvc-jfreeChart柱图(2)

布衣凌宇

jfreechart

上一篇中生成的图是静态的,这篇将按条件进行搜索,并统计成图表,左面为统计图,右面显示搜索出的结果。

第一步:导包

第二步;配置web.xml(上一篇有代码)

建BarRenderer类用于柱子颜色

import java.awt.Color;

import java.awt.Paint;

import org.jfree.chart.renderer.category.BarR

- 我的spring学习笔记14-容器扩展点之PropertyPlaceholderConfigurer

aijuans

Spring3

PropertyPlaceholderConfigurer是个bean工厂后置处理器的实现,也就是BeanFactoryPostProcessor接口的一个实现。关于BeanFactoryPostProcessor和BeanPostProcessor类似。我会在其他地方介绍。

PropertyPlaceholderConfigurer可以将上下文(配置文件)中的属性值放在另一个单独的标准java

- maven 之 cobertura 简单使用

antlove

maventestunitcoberturareport

1. 创建一个maven项目

2. 创建com.CoberturaStart.java

package com;

public class CoberturaStart {

public void helloEveryone(){

System.out.println("=================================================

- 程序的执行顺序

百合不是茶

JAVA执行顺序

刚在看java核心技术时发现对java的执行顺序不是很明白了,百度一下也没有找到适合自己的资料,所以就简单的回顾一下吧

代码如下;

经典的程序执行面试题

//关于程序执行的顺序

//例如:

//定义一个基类

public class A(){

public A(

- 设置session失效的几种方法

bijian1013

web.xmlsession失效监听器

在系统登录后,都会设置一个当前session失效的时间,以确保在用户长时间不与服务器交互,自动退出登录,销毁session。具体设置很简单,方法有三种:(1)在主页面或者公共页面中加入:session.setMaxInactiveInterval(900);参数900单位是秒,即在没有活动15分钟后,session将失效。这里要注意这个session设置的时间是根据服务器来计算的,而不是客户端。所

- java jvm常用命令工具

bijian1013

javajvm

一.概述

程序运行中经常会遇到各种问题,定位问题时通常需要综合各种信息,如系统日志、堆dump文件、线程dump文件、GC日志等。通过虚拟机监控和诊断工具可以帮忙我们快速获取、分析需要的数据,进而提高问题解决速度。 本文将介绍虚拟机常用监控和问题诊断命令工具的使用方法,主要包含以下工具:

&nbs

- 【Spring框架一】Spring常用注解之Autowired和Resource注解

bit1129

Spring常用注解

Spring自从2.0引入注解的方式取代XML配置的方式来做IOC之后,对Spring一些常用注解的含义行为一直处于比较模糊的状态,写几篇总结下Spring常用的注解。本篇包含的注解有如下几个:

Autowired

Resource

Component

Service

Controller

Transactional

根据它们的功能、目的,可以分为三组,Autow

- mysql 操作遇到safe update mode问题

bitray

update

我并不知道出现这个问题的实际原理,只是通过其他朋友的博客,文章得知的一个解决方案,目前先记录一个解决方法,未来要是真了解以后,还会继续补全.

在mysql5中有一个safe update mode,这个模式让sql操作更加安全,据说要求有where条件,防止全表更新操作.如果必须要进行全表操作,我们可以执行

SET

- nginx_perl试用

ronin47

nginx_perl试用

因为空闲时间比较多,所以在CPAN上乱翻,看到了nginx_perl这个项目(原名Nginx::Engine),现在托管在github.com上。地址见:https://github.com/zzzcpan/nginx-perl

这个模块的目的,是在nginx内置官方perl模块的基础上,实现一系列异步非阻塞的api。用connector/writer/reader完成类似proxy的功能(这里

- java-63-在字符串中删除特定的字符

bylijinnan

java

public class DeleteSpecificChars {

/**

* Q 63 在字符串中删除特定的字符

* 输入两个字符串,从第一字符串中删除第二个字符串中所有的字符。

* 例如,输入”They are students.”和”aeiou”,则删除之后的第一个字符串变成”Thy r stdnts.”

*/

public static voi

- EffectiveJava--创建和销毁对象

ccii

创建和销毁对象

本章内容:

1. 考虑用静态工厂方法代替构造器

2. 遇到多个构造器参数时要考虑用构建器(Builder模式)

3. 用私有构造器或者枚举类型强化Singleton属性

4. 通过私有构造器强化不可实例化的能力

5. 避免创建不必要的对象

6. 消除过期的对象引用

7. 避免使用终结方法

1. 考虑用静态工厂方法代替构造器

类可以通过

- [宇宙时代]四边形理论与光速飞行

comsci

从四边形理论来推论 为什么光子飞船必须获得星光信号才能够进行光速飞行?

一组星体组成星座 向空间辐射一组由复杂星光信号组成的辐射频带,按照四边形-频率假说 一组频率就代表一个时空的入口

那么这种由星光信号组成的辐射频带就代表由这些星体所控制的时空通道,该时空通道在三维空间的投影是一

- ubuntu server下python脚本迁移数据

cywhoyi

pythonKettlepymysqlcx_Oracleubuntu server

因为是在Ubuntu下,所以安装python、pip、pymysql等都极其方便,sudo apt-get install pymysql,

但是在安装cx_Oracle(连接oracle的模块)出现许多问题,查阅相关资料,发现这边文章能够帮我解决,希望大家少走点弯路。http://www.tbdazhe.com/archives/602

1.安装python

2.安装pip、pymysql

- Ajax正确但是请求不到值解决方案

dashuaifu

Ajaxasync

Ajax正确但是请求不到值解决方案

解决方案:1 . async: false , 2. 设置延时执行js里的ajax或者延时后台java方法!!!!!!!

例如:

$.ajax({ &

- windows安装配置php+memcached

dcj3sjt126com

PHPInstallmemcache

Windows下Memcached的安装配置方法

1、将第一个包解压放某个盘下面,比如在c:\memcached。

2、在终端(也即cmd命令界面)下输入 'c:\memcached\memcached.exe -d install' 安装。

3、再输入: 'c:\memcached\memcached.exe -d start' 启动。(需要注意的: 以后memcached将作为windo

- iOS开发学习路径的一些建议

dcj3sjt126com

ios

iOS论坛里有朋友要求回答帖子,帖子的标题是: 想学IOS开发高阶一点的东西,从何开始,然后我吧啦吧啦回答写了很多。既然敲了那么多字,我就把我写的回复也贴到博客里来分享,希望能对大家有帮助。欢迎大家也到帖子里讨论和分享,地址:http://bbs.csdn.net/topics/390920759

下面是我回复的内容:

结合自己情况聊下iOS学习建议,

- Javascript闭包概念

fanfanlovey

JavaScript闭包

1.参考资料

http://www.jb51.net/article/24101.htm

http://blog.csdn.net/yn49782026/article/details/8549462

2.内容概述

要理解闭包,首先需要理解变量作用域问题

内部函数可以饮用外面全局变量

var n=999;

functio

- yum安装mysql5.6

haisheng

mysql

1、安装http://dev.mysql.com/get/mysql-community-release-el7-5.noarch.rpm

2、yum install mysql

3、yum install mysql-server

4、vi /etc/my.cnf 添加character_set_server=utf8

- po/bo/vo/dao/pojo的详介

IT_zhlp80

javaBOVODAOPOJOpo

JAVA几种对象的解释

PO:persistant object持久对象,可以看成是与数据库中的表相映射的java对象。最简单的PO就是对应数据库中某个表中的一条记录,多个记录可以用PO的集合。PO中应该不包含任何对数据库的操作.

VO:value object值对象。通常用于业务层之间的数据传递,和PO一样也是仅仅包含数据而已。但应是抽象出的业务对象,可

- java设计模式

kerryg

java设计模式

设计模式的分类:

一、 设计模式总体分为三大类:

1、创建型模式(5种):工厂方法模式,抽象工厂模式,单例模式,建造者模式,原型模式。

2、结构型模式(7种):适配器模式,装饰器模式,代理模式,外观模式,桥接模式,组合模式,享元模式。

3、行为型模式(11种):策略模式,模版方法模式,观察者模式,迭代子模式,责任链模式,命令模式,备忘录模式,状态模式,访问者

- [1]CXF3.1整合Spring开发webservice——helloworld篇

木头.java

springwebserviceCXF

Spring 版本3.2.10

CXF 版本3.1.1

项目采用MAVEN组织依赖jar

我这里是有parent的pom,为了简洁明了,我直接把所有的依赖都列一起了,所以都没version,反正上面已经写了版本

<project xmlns="http://maven.apache.org/POM/4.0.0" xmlns:xsi="ht

- Google 工程师亲授:菜鸟开发者一定要投资的十大目标

qindongliang1922

工作感悟人生

身为软件开发者,有什么是一定得投资的? Google 软件工程师 Emanuel Saringan 整理了十项他认为必要的投资,第一项就是身体健康,英文与数学也都是必备能力吗?来看看他怎么说。(以下文字以作者第一人称撰写)) 你的健康 无疑地,软件开发者是世界上最久坐不动的职业之一。 每天连坐八到十六小时,休息时间只有一点点,绝对会让你的鲔鱼肚肆无忌惮的生长。肥胖容易扩大罹患其他疾病的风险,

- linux打开最大文件数量1,048,576

tianzhihehe

clinux

File descriptors are represented by the C int type. Not using a special type is often considered odd, but is, historically, the Unix way. Each Linux process has a maximum number of files th

- java语言中PO、VO、DAO、BO、POJO几种对象的解释

衞酆夼

javaVOBOPOJOpo

PO:persistant object持久对象

最形象的理解就是一个PO就是数据库中的一条记录。好处是可以把一条记录作为一个对象处理,可以方便的转为其它对象。可以看成是与数据库中的表相映射的java对象。最简单的PO就是对应数据库中某个表中的一条记录,多个记录可以用PO的集合。PO中应该不包含任何对数据库的操作。

BO:business object业务对象

封装业务逻辑的java对象