缓存和主存系统(Cache and Memory)

缓存和主存系统(Cache and Memory)

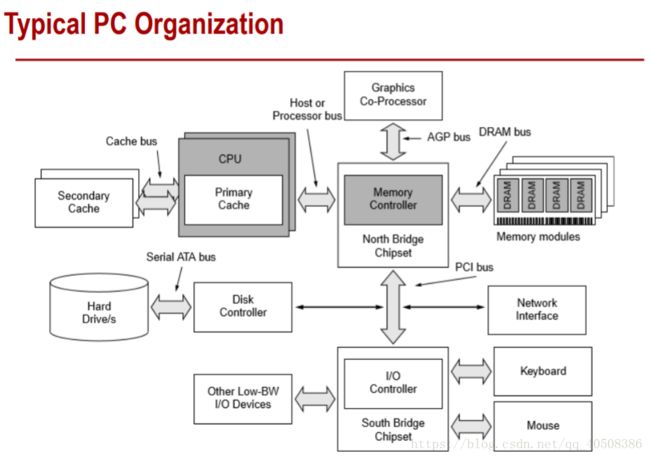

1、总览经典PC架构

用于后续联系各个部件之间的关系,不然经常讲完某个部件却不知道在整个系统中的位置。

观察上图产生的几个疑问:

(1)cache在cpu和主板上?以什么介质形式存在?(主板不大肯定无法提供大空间)

(2)DRAM(Memory)在哪里,又以什么介质形式存在?

先扔在这。

2、内存层次

ps:Tape虽然已经慢慢退伍,但还是一项比较常用的存储方式。(最大的缺点就是运输过程中易损坏)

关注点:实现技术,管理方式,存取类型。

一个疑惑:随机存储中的随机是什么意思?

本篇接下来主要讲述两个部分(Cache and DRAM)

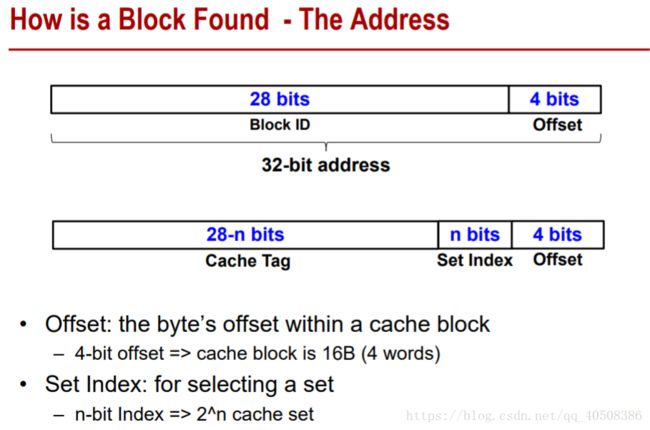

3、Cache Basics

Basic Concepts:

注意:主板上面的chip不只一片,chip主要分为南,北桥,以及cpu芯片。

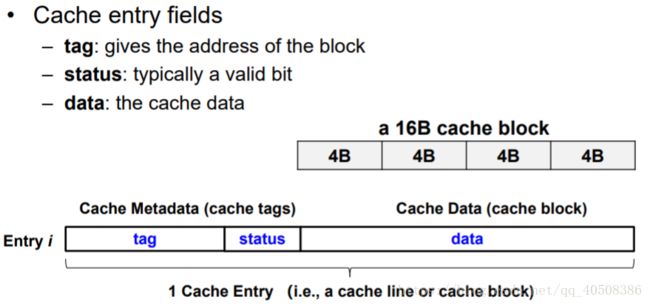

Cache lines or Cache blocks

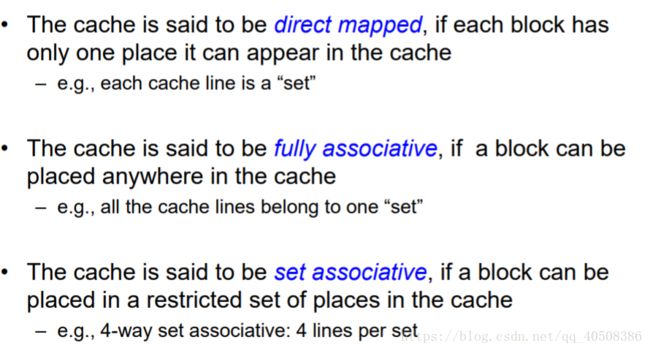

cache类型:

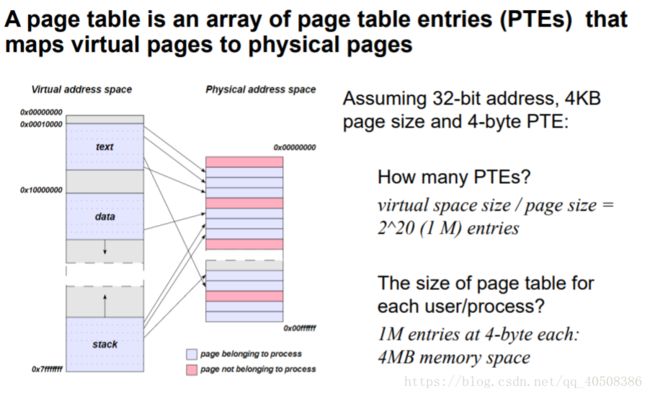

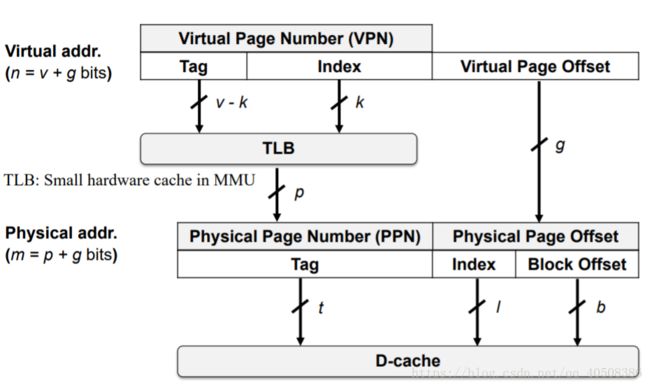

VM(虚拟内存)Virtual Memory

地址转换:

具体计算不是体系结构主要关注的(以后复习)

Optimizations

局部性原则:

时间局部性,空间局部性,算法局部性

注意:其中算法局部性比较特殊,它是对一些访问数据有一定规律的程序(这些数据又是呈现分布式的,否则就是时间局部性了)。至于时空局部性就很好理解了。

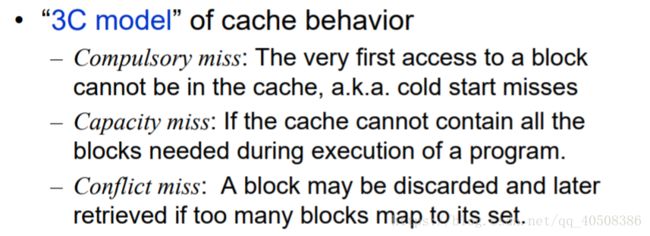

Reducing Miss Rate

必要性miss,即cold start miss(一开始访问的时候)

容量性miss:cache size不够。

冲突性miss:多个block映射到同一组导致set里面line不够(和容量性miss有一定的区别)

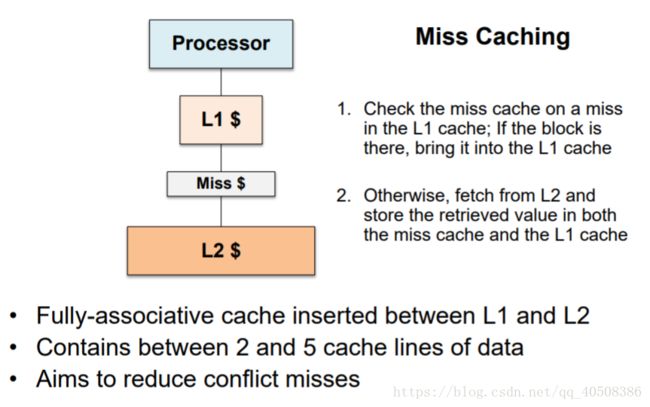

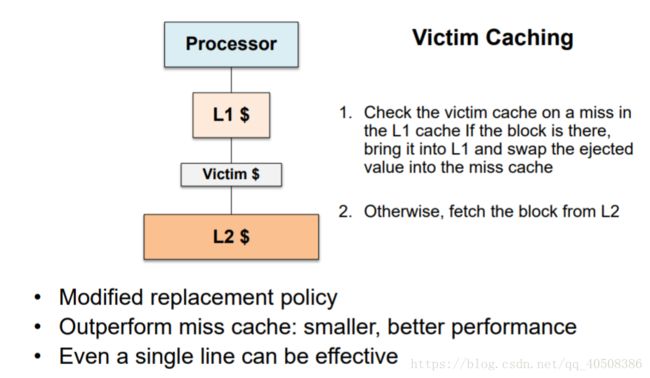

两种降低miss rate的策略:Miss caching && Victim Caching

缺点:还是会由于将miss cache替换导致conflict miss(这样miss cache的作用就没有了)

提高性能的另一种方式:Prefetching

Cache Write Policies:

-----------------------------------------------------------------------------

DRAM System(Main memory)

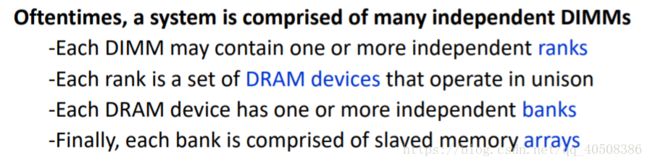

整体结构层次:

DIMM:(dual in-line memory module)由一个或多个Rank组成。

DRAM device由多个(比如8个)内部BANKS组成。

DIMM--RANK----DRAM device--BANKS--DRAM arrays

即;

po一个侧面图:

MC分为单和多MC:

关于Bank中memory array的数量:(column width)

DRAM cell:1T1C