内核目录下的设备树手册路径Kernel/Documentation/devicetree/bindings

今天的需求是用QT读写can接口,之前天嵌的老系统驱动很全,不用改,但是用yocto的话官方的设备树没有做相关适配,比竞属于自己定制的板子,官方肯定不管了,不过官方都给了相应的参考文件。

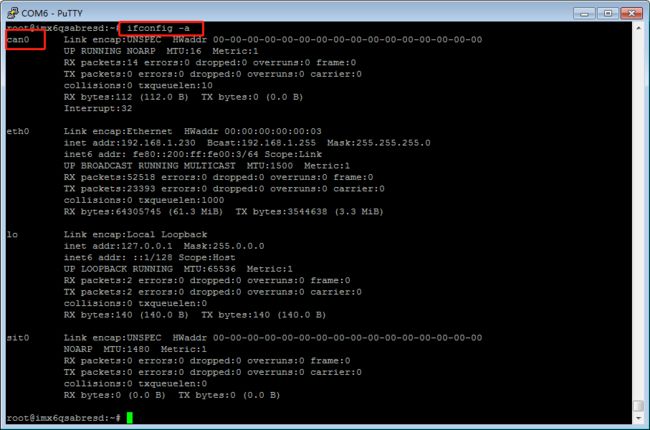

首先确定一下你的can是否正常工作了

判断can是否工作

//因为can在新版内核里属于网络设备,所以用这个命令查看can设备是否正常

root@imx6qsabresd:~# ifconfig -a

eth0 Link encap:Ethernet HWaddr 00:00:00:00:00:03

inet addr:192.168.1.230 Bcast:192.168.1.255 Mask:255.255.255.0

inet6 addr: fe80::200:ff:fe00:3/64 Scope:Link

UP BROADCAST RUNNING MULTICAST MTU:1500 Metric:1

RX packets:52518 errors:0 dropped:0 overruns:0 frame:0

TX packets:23393 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:64305745 (61.3 MiB) TX bytes:3544638 (3.3 MiB)

lo Link encap:Local Loopback

inet addr:127.0.0.1 Mask:255.0.0.0

inet6 addr: ::1/128 Scope:Host

UP LOOPBACK RUNNING MTU:65536 Metric:1

RX packets:2 errors:0 dropped:0 overruns:0 frame:0

TX packets:2 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:0

RX bytes:140 (140.0 B) TX bytes:140 (140.0 B)

sit0 Link encap:UNSPEC HWaddr 00-00-00-00-00-00-00-00-00-00-00-00-00-00-00-00

NOARP MTU:1480 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:0

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)

从上面的代码可以判断,can设备没有正确识别,下图是正常识别的效果

开始移植

参考这篇文章I.MX6Q(TQIMX6Q/TQE9)学习笔记——新版BSP之CAN移植

因为girlkoo大神的CSDN里面有很多移植心得,首先就想到了参考一下大神是怎么改的。这篇文章可以很好的提供修改思路。

修改思路

- 创建一个节点

- 描述这个节点的相关信息

设备树语法

参考这篇文章--点击进入

Dts中相关符号的含义

- “/” 根节点

- “@” 如果设备有地址,则由此符号指定

- “&” 引用节点(比如这个设备树include了其他的设备树文件,其他设备树文件里有个ABC节点,&ABC就可以引用这个节点并添加新的属性了)

- “:” 冒号前的label是为了方便引用给节点起的别名,此label一般使用为&label,冒号后面的就是这个节点真正的名字了

- “,” 属性名称中可以包含逗号。如compatible属性的名字 组成方式为"[manufacturer], [model]",加入厂商名是为了避免重名。自定义属性名中通常也要有厂商名,并以逗号分隔。

- “#” #并不表示注释。如 #address-cells ,#size-cells 用来决定reg属性的格式。

- 空属性并不一定表示没有赋值。如 interrupt-controller 一个空属性用来声明这个node接收中断信号

数据类型- “” 引号中的为字符串,字符串数组:”strint1”,”string2”,”string3”

- < > 尖括号中的为32位整形数字,整形数组<12 3 4>

- “[ ]” 方括号中的为32位十六进制数,十六机制数据[0x11 0x12 0x13] 其中0x可省略

节点名命名规则

每个节点必须有一个“<名称>[@<设备地址>]”形式的名字

<名称> 就是一个不超过31位的简单 ascii 字符串

<设备地址>就是用来访问该设备的主地址(基地址),并且该地址也在节点的 reg 属性中列出

cpus {

cpu@0 {

compatible = "arm,cortex-a9";

};

cpu@1 {

compatible = "arm,cortex-a9";

};

};

同级节点命名必须是唯一的,但只要地址不同,多个节点也可以使用一样的通用名称(例如 serial@101f1000 和 serial@101f2000)

serial@101F0000 {

compatible = "arm,pl011";

};

serial@101F2000 {

compatible = "arm,pl011";

};

**节点的命名应当反映设备的类型而不是特定的型号**

创建一个can节点

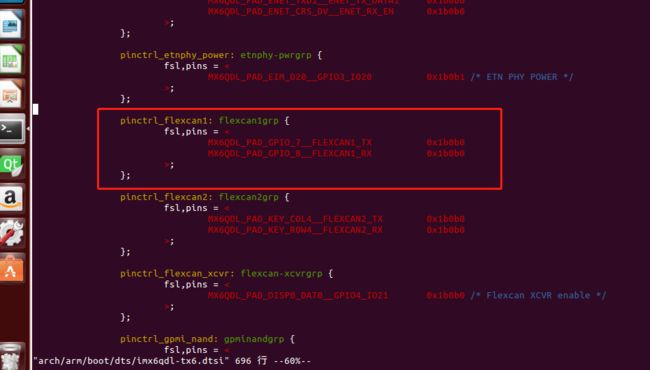

上图中是内核源码目录下arch/arm/boot/dts/imx6qdl-tx6.dtsi文件,同属于一个系列的不同版本,参考价值很高

&can1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_flexcan1>;//引用其他地方的label

/*xceiver-supply = <®_can_xcvr>;*/

status = "okay";//注意这里的okay是开启can的关键

};

/*第四行的代码会报错,变量找不到,经测试不加也可。*/

注意:我参考girlkoo的文章时也是用flexcan这个节点名,但是编译报错,找不到flexcan,百度发现了上图中的文章,内核版本不一样,节点名可能有变化哟,但是我还是不知道这个名字到底是哪个文件里定义的,有知道的同学希望留言告诉下我~

描述这个can节点的关键参数

pinctrl_flexcan1: flexcan1grp {

fsl,pins = <

MX6QDL_PAD_GPIO_7__FLEXCAN1_TX 0x1b0b0//双底杠前后表示相互的复用关系

MX6QDL_PAD_GPIO_8__FLEXCAN1_RX 0x1b0b0

>;

};

//具体是哪个IO请自行查看原理图

相关解释

对于设备树熟悉的人来说上面的很容易理解,那么对于新人来说就需要解释下了。

&can1 {

....

}

这句话的意思是存在一个节点叫做can1,括号里面都是can1节点的通用信息

pinctrl_flexcan1: flexcan1grp {

....

}

上面这句话的意思是有个名为pinctrl_flexcan1的引脚配置项,括号里面包含的是引脚复用参数,参考下图去配置。

小技巧,使用这条命令可以递归查找并显示引号包含的内容所在文件的第几行,这样可以快速搜索关键线索内容所在文件的位置,比如别的板子设备树文件是怎么配置的。

grep -rn “MX6QDL_PAD_GPIO_7__FLEXCAN1_TX” *

综合一下就是

&can1 {

....

pinctrl-0 = <&pinctrl_flexcan1>;

....

};

//上面的&pinctrl_flexcan1引用了下面的具体配置内容

pinctrl_flexcan1: flexcan1grp {

....

}

下面是设备树源码,适配了天嵌的 SD卡/USB2514/OTG SY6280/触摸ft5x06/声卡sgtl5000/串口ttymxc1/串口ttymxc3/GPIO GPIO4_5

/*dtsi文件*/

/*

* Copyright 2012-2016 Freescale Semiconductor, Inc.

* Copyright 2011 Linaro Ltd.

*

* The code contained herein is licensed under the GNU General Public

* License. You may obtain a copy of the GNU General Public License

* Version 2 or later at the following locations:

*

* http://www.opensource.org/licenses/gpl-license.html

* http://www.gnu.org/copyleft/gpl.html

*/

#include

#include

/ {

aliases {

mxcfb0 = &mxcfb1;

/*

mxcfb1 = &mxcfb2;

mxcfb2 = &mxcfb3;

mxcfb3 = &mxcfb4;

*/

};

battery: max8903@0 {

compatible = "fsl,max8903-charger";

pinctrl-names = "default";

dok_input = <&gpio2 24 1>;

uok_input = <&gpio1 27 1>;

chg_input = <&gpio3 23 1>;

flt_input = <&gpio5 2 1>;

fsl,dcm_always_high;

fsl,dc_valid;

fsl,usb_valid;

status = "okay";

};

hannstar_cabc {

compatible = "hannstar,cabc";

lvds0 {

gpios = <&gpio6 15 GPIO_ACTIVE_HIGH>;

};

lvds1 {

gpios = <&gpio6 16 GPIO_ACTIVE_HIGH>;

};

};

chosen {

stdout-path = &uart1;

};

leds {

compatible = "gpio-leds";

charger-led {

gpios = <&gpio1 2 0>;

linux,default-trigger = "max8903-charger-charging";

retain-state-suspended;

};

};

memory: memory {

reg = <0x10000000 0x40000000>;

};

regulators {

compatible = "simple-bus";

#address-cells = <1>;

#size-cells = <0>;

reg_usb_otg_vbus: regulator@0 {

compatible = "regulator-fixed";

reg = <0>;

regulator-name = "usb_otg_vbus";

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

/*gpio = <&gpio3 22 0>;*/

gpio = <&gpio7 1 0>;/*yinshuaihua*/

enable-active-high;

/*vin-supply = <&swbst_reg>;*/

};

reg_usb_h1_vbus: regulator@1 {

compatible = "regulator-fixed";

reg = <1>;

regulator-name = "usb_h1_vbus";

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

/*gpio = <&gpio1 29 0>;*/

gpio = <&gpio1 20 0>;/*yinshuaihua*/

enable-active-high;

/*vin-supply = <&swbst_reg>;*/

regulator-always-on;/*yinshuaihua*/

};

reg_audio: regulator@2 {

compatible = "regulator-fixed";

reg = <2>;

regulator-name = "wm8962-supply";

gpio = <&gpio4 10 0>;

enable-active-high;

};

reg_pcie: regulator@3 {

compatible = "regulator-fixed";

reg = <3>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_pcie_reg>;

regulator-name = "MPCIE_3V3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

gpio = <&gpio3 19 0>;

regulator-always-on;

enable-active-high;

};

reg_sensor: regulator@4 {

regulator-name = "sensor-supply";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

gpio = <&gpio2 31 0>;

startup-delay-us = <500>;

enable-active-high;

};

reg_hdmi: regulator@5 {

compatible = "regulator-fixed";

reg = <5>;

regulator-name = "hdmi-5v-supply";

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5000000>;

enable-active-high;

hdmi-5v-supply = <&swbst_reg>;

};

reg_mipi_dsi_pwr_on: mipi_dsi_pwr_on {

compatible = "regulator-fixed";

regulator-name = "mipi_dsi_pwr_on";

gpio = <&gpio6 14 0>;

enable-active-high;

};

reg_3p3v: 3p3v {

compatible = "regulator-fixed";

regulator-name = "3P3V";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

regulator-always-on;

};

reg_1p2v: 1p2v{

compatible = "regulator-fixed";

regulator-name = "1P2V";

regulator-min-microvolt = <1200000>;

regulator-max-microvolt = <1200000>;

regulator-always-on;

};

reg_2p5v: 2p5v{

compatible = "regulator-fixed";

regulator-name = "2P5V";

regulator-min-microvolt = <2500000>;

regulator-max-microvolt = <2500000>;

regulator-always-on;

};

};

gpio-keys {

compatible = "gpio-keys";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_gpio_keys>;

power {

label = "Power Button";

gpios = <&gpio3 29 GPIO_ACTIVE_LOW>;

gpio-key,wakeup;

linux,code = ;

};

volume-up {

label = "Volume Up";

gpios = <&gpio1 4 GPIO_ACTIVE_LOW>;

gpio-key,wakeup;

linux,code = ;

};

volume-down {

label = "Volume Down";

gpios = <&gpio1 5 GPIO_ACTIVE_LOW>;

gpio-key,wakeup;

linux,code = ;

};

};

sound {

/* compatible = "fsl,imx6q-sabresd-wm8962",

"fsl,imx-audio-wm8962";

model = "wm8962-audio";

cpu-dai = <&ssi2>;

audio-codec = <&codec>;

asrc-controller = <&asrc>;

audio-routing =

"Headphone Jack", "HPOUTL",

"Headphone Jack", "HPOUTR",

"Ext Spk", "SPKOUTL",

"Ext Spk", "SPKOUTR",

"AMIC", "MICBIAS",

"IN3R", "AMIC",

"DMIC", "MICBIAS",

"DMICDAT", "DMIC",

"CPU-Playback", "ASRC-Playback",

"Playback", "CPU-Playback",

"ASRC-Capture", "CPU-Capture",

"CPU-Capture", "Capture";

mux-int-port = <2>;

mux-ext-port = <3>;

codec-master;

hp-det-gpios = <&gpio7 8 1>;

mic-det-gpios = <&gpio1 9 1>;

*/

compatible = "fsl,imx-audio-sgtl5000";

model = "imx6q-sgtl5000";

ssi-controller = <&ssi1>;

audio-codec = <&codec>;

audio-routing =

"MIC_IN", "Mic Jack",

"Mic Jack", "Mic Bias",

"Headphone Jack", "HP_OUT";

mux-int-port = <1>;

mux-ext-port = <3>;

};

sound-hdmi {

compatible = "fsl,imx6q-audio-hdmi",

"fsl,imx-audio-hdmi";

model = "imx-audio-hdmi";

hdmi-controller = <&hdmi_audio>;

};

mxcfb1: fb@0 {

compatible = "fsl,mxc_sdc_fb";

disp_dev = "lcd";

interface_pix_fmt = "RGB24";

/* mode_str ="CLAA-WVGA"; */

mode_str ="1024x600M@60";

default_bpp = <24>;

int_clk = <0>;

late_init = <0>;

status = "ok";

};

mxcfb2: fb@1 {

compatible = "fsl,mxc_sdc_fb";

disp_dev = "hdmi";

interface_pix_fmt = "RGB24";

mode_str ="1920x1080M@60";

default_bpp = <24>;

int_clk = <0>;

late_init = <0>;

status = "disabled";

};

mxcfb3: fb@2 {

compatible = "fsl,mxc_sdc_fb";

disp_dev = "lcd";

interface_pix_fmt = "RGB565";

mode_str ="CLAA-WVGA";

default_bpp = <16>;

int_clk = <0>;

late_init = <0>;

status = "disabled";

};

mxcfb4: fb@3 {

compatible = "fsl,mxc_sdc_fb";

disp_dev = "ldb";

interface_pix_fmt = "RGB666";

default_bpp = <16>;

int_clk = <0>;

late_init = <0>;

status = "disabled";

};

lcd@0 {

compatible = "fsl,lcd";

ipu_id = <0>;

disp_id = <0>;

default_ifmt = "RGB565";

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ipu1>;

status = "okay";

};

backlight {

compatible = "pwm-backlight";

pwms = <&pwm1 0 5000000>;

brightness-levels = <0 4 8 16 32 64 128 255>;

default-brightness-level = <7>;

status = "okay";

};

v4l2_cap_0 {

compatible = "fsl,imx6q-v4l2-capture";

ipu_id = <0>;

csi_id = <0>;

mclk_source = <0>;

status = "okay";

};

v4l2_cap_1 {

compatible = "fsl,imx6q-v4l2-capture";

ipu_id = <0>;

csi_id = <1>;

mclk_source = <0>;

status = "okay";

};

v4l2_out {

compatible = "fsl,mxc_v4l2_output";

status = "okay";

};

mipi_dsi_reset: mipi-dsi-reset {

compatible = "gpio-reset";

reset-gpios = <&gpio6 11 GPIO_ACTIVE_LOW>;

reset-delay-us = <50>;

#reset-cells = <0>;

};

};

&can1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_flexcan1>;

status = "okay";

};

&audmux {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_audmux>;

status = "okay";

};

&ssi1 {

fsl,mode = "i2s-slave";

status = "okay";

};

&ssi2 {

fsl,mode = "i2s-slave";

status = "okay";

};

&cpu0 {

arm-supply = <&sw1a_reg>;

soc-supply = <&sw1c_reg>;

};

&clks {

fsl,ldb-di0-parent = <&clks IMX6QDL_CLK_PLL2_PFD0_352M>;

fsl,ldb-di1-parent = <&clks IMX6QDL_CLK_PLL2_PFD0_352M>;

};

&ecspi1 {

fsl,spi-num-chipselects = <1>;

cs-gpios = <&gpio4 9 0>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ecspi1>;

status = "okay";

flash: m25p80@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "st,m25p32";

spi-max-frequency = <20000000>;

reg = <0>;

};

};

&fec {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_enet>;

phy-mode = "rgmii";

phy-reset-gpios = <&gpio1 25 0>;

fsl,magic-packet;

status = "okay";

};

&gpc {

fsl,ldo-bypass = <1>;

};

&dcic1 {

dcic_id = <0>;

dcic_mux = "dcic-hdmi";

status = "okay";

};

&dcic2 {

dcic_id = <1>;

dcic_mux = "dcic-lvds1";

status = "okay";

};

&hdmi_audio {

status = "okay";

};

&hdmi_cec {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hdmi_cec>;

status = "okay";

};

&hdmi_core {

ipu_id = <0>;

disp_id = <0>;

status = "okay";

};

&hdmi_video {

fsl,phy_reg_vlev = <0x0294>;

fsl,phy_reg_cksymtx = <0x800d>;

HDMI-supply = <®_hdmi>;

status = "okay";

};

&i2c1 {

clock-frequency = <100000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c1>;

status = "okay";

def_speed = <50>;

edt-ft5x06@38{

compatible = "edt,edt-ft5306";

reg = <0x38>;

pinctrl-names = "default";

/*

pinctrl-0 = <&pinctrl_edt_ft5x06>;

*/

interrupt-parent = <&gpio1>;

interrupts = <9 2>;

rst-gpios = <&gpio1 5 1>; /* active high: SD1_DAT1 */

touchscreen-size-x = <1024>;

touchscreen-size-y = <600>;

/*

touchscreen-swap = <1>;

touchscreen-revert-x = <1>;

touchscreen-revert-y = <1>;

*/

};

/*

gt811@5d {

compatible = "gt811,gt811_ts";

pinctrl-names = "default";

reg = <0x5d>;

interrupt-parent = <&gpio1>;

interrupts = <9 2>;

gpios = <&gpio1 5 0>;

touchscreen-size-x = <1024>;

touchscreen-size-y = <600>;

touchscreen-swap = <1>;

touchscreen-revert-x = <1>;

touchscreen-revert-y = <1>;

};

*/

/* codec: wm8962@1a {

compatible = "wlf,wm8962";

reg = <0x1a>;

clocks = <&clks IMX6QDL_CLK_CKO>;

DCVDD-supply = <®_audio>;

DBVDD-supply = <®_audio>;

AVDD-supply = <®_audio>;

CPVDD-supply = <®_audio>;

MICVDD-supply = <®_audio>;

PLLVDD-supply = <®_audio>;

SPKVDD1-supply = <®_audio>;

SPKVDD2-supply = <®_audio>;

gpio-cfg = <

0x0000 /* 0:Default */

/* 0x0000 /* 1:Default */

/* 0x0013 /* 2:FN_DMICCLK*/

/* 0x0000 /* 3:Default */

/* 0x8014 /* 4:FN_DMICCDAT*/

/* 0x0000 /* 5:Default */

/* >;

amic-mono;

};

*/

mma8451@1c {

compatible = "fsl,mma8451";

reg = <0x1c>;

position = <0>;

vdd-supply = <®_sensor>;

vddio-supply = <®_sensor>;

interrupt-parent = <&gpio1>;

interrupts = <18 8>;

interrupt-route = <1>;

};

ov564x: ov564x@3c {

compatible = "ovti,ov564x";

reg = <0x3c>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_ipu1_2>;

clocks = <&clks IMX6QDL_CLK_CKO>;

clock-names = "csi_mclk";

DOVDD-supply = <&vgen4_reg>; /* 1.8v */

AVDD-supply = <&vgen3_reg>; /* 2.8v, on rev C board is VGEN3,

on rev B board is VGEN5 */

DVDD-supply = <&vgen2_reg>; /* 1.5v*/

pwn-gpios = <&gpio1 16 1>; /* active low: SD1_DAT0 */

rst-gpios = <&gpio1 17 0>; /* active high: SD1_DAT1 */

csi_id = <0>;

mclk = <24000000>;

mclk_source = <0>;

};

};

&i2c2 {

clock-frequency = <100000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c2>;

status = "okay";

egalax_ts@04 {

compatible = "eeti,egalax_ts";

reg = <0x04>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c2_egalax_int>;

interrupt-parent = <&gpio6>;

interrupts = <8 2>;

wakeup-gpios = <&gpio6 8 GPIO_ACTIVE_HIGH>;

};

max11801@48 {

compatible = "maxim,max11801";

reg = <0x48>;

interrupt-parent = <&gpio3>;

interrupts = <26 2>;

work-mode = <1>;/*DCM mode*/

};

codec: sgtl5000@0a {

compatible = "fsl,sgtl5000";

reg = <0x0a>;

clocks = <&clks 201>;

VDDA-supply = <®_2p5v>;

VDDIO-supply = <®_3p3v>;

/*VDDD-supply = <®_1p2v>;*/

};

pmic: pfuze100@08 {

compatible = "fsl,pfuze100";

reg = <0x08>;

regulators {

sw1a_reg: sw1ab {

regulator-min-microvolt = <300000>;

regulator-max-microvolt = <1875000>;

regulator-boot-on;

regulator-always-on;

regulator-ramp-delay = <6250>;

};

sw1c_reg: sw1c {

regulator-min-microvolt = <300000>;

regulator-max-microvolt = <1875000>;

regulator-boot-on;

regulator-always-on;

regulator-ramp-delay = <6250>;

};

sw2_reg: sw2 {

regulator-min-microvolt = <800000>;

regulator-max-microvolt = <3300000>;

regulator-boot-on;

regulator-always-on;

regulator-ramp-delay = <6250>;

};

sw3a_reg: sw3a {

regulator-min-microvolt = <400000>;

regulator-max-microvolt = <1975000>;

regulator-boot-on;

regulator-always-on;

};

sw3b_reg: sw3b {

regulator-min-microvolt = <400000>;

regulator-max-microvolt = <1975000>;

regulator-boot-on;

regulator-always-on;

};

sw4_reg: sw4 {

regulator-min-microvolt = <800000>;

regulator-max-microvolt = <3300000>;

};

swbst_reg: swbst {

regulator-min-microvolt = <5000000>;

regulator-max-microvolt = <5150000>;

};

snvs_reg: vsnvs {

regulator-min-microvolt = <1000000>;

regulator-max-microvolt = <3000000>;

regulator-boot-on;

regulator-always-on;

};

vref_reg: vrefddr {

regulator-boot-on;

regulator-always-on;

};

vgen1_reg: vgen1 {

regulator-min-microvolt = <800000>;

regulator-max-microvolt = <1550000>;

};

vgen2_reg: vgen2 {

regulator-min-microvolt = <800000>;

regulator-max-microvolt = <1550000>;

};

vgen3_reg: vgen3 {

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <3300000>;

};

vgen4_reg: vgen4 {

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <3300000>;

regulator-always-on;

};

vgen5_reg: vgen5 {

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <3300000>;

regulator-always-on;

};

vgen6_reg: vgen6 {

regulator-min-microvolt = <1800000>;

regulator-max-microvolt = <3300000>;

regulator-always-on;

};

};

};

hdmi: edid@50 {

compatible = "fsl,imx6-hdmi-i2c";

reg = <0x50>;

};

ov564x_mipi: ov564x_mipi@3c { /* i2c2 driver */

compatible = "ovti,ov564x_mipi";

reg = <0x3c>;

clocks = <&clks 201>;

clock-names = "csi_mclk";

DOVDD-supply = <&vgen4_reg>; /* 1.8v */

AVDD-supply = <&vgen3_reg>; /* 2.8v, rev C board is VGEN3

rev B board is VGEN5 */

DVDD-supply = <&vgen2_reg>; /* 1.5v*/

pwn-gpios = <&gpio1 19 1>; /* active low: SD1_CLK */

rst-gpios = <&gpio1 20 0>; /* active high: SD1_DAT2 */

csi_id = <1>;

mclk = <24000000>;

mclk_source = <0>;

};

};

&i2c3 {

clock-frequency = <100000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c3>;

status = "okay";

egalax_ts@04 {

compatible = "eeti,egalax_ts";

reg = <0x04>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c3_egalax_int>;

interrupt-parent = <&gpio6>;

interrupts = <7 2>;

wakeup-gpios = <&gpio6 7 GPIO_ACTIVE_HIGH>;

};

isl29023@44 {

compatible = "fsl,isl29023";

reg = <0x44>;

rext = <499>;

vdd-supply = <®_sensor>;

interrupt-parent = <&gpio3>;

interrupts = <9 2>;

};

mag3110@0e {

compatible = "fsl,mag3110";

reg = <0x0e>;

position = <2>;

vdd-supply = <®_sensor>;

vddio-supply = <®_sensor>;

interrupt-parent = <&gpio3>;

interrupts = <16 1>;

};

};

&iomuxc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hog>;

imx6qdl-sabresd {

pinctrl_hog: hoggrp {

fsl,pins = <

MX6QDL_PAD_NANDF_D0__GPIO2_IO00 0x80000000

MX6QDL_PAD_NANDF_D1__GPIO2_IO01 0x80000000

MX6QDL_PAD_NANDF_D2__GPIO2_IO02 0x80000000

MX6QDL_PAD_NANDF_D3__GPIO2_IO03 0x80000000

MX6QDL_PAD_GPIO_0__CCM_CLKO1 0x130b0

/*MX6QDL_PAD_GPIO_0__CCM_CLKO1 0x80000000*/

MX6QDL_PAD_GPIO_19__GPIO4_IO05 0x80000000

MX6QDL_PAD_ENET_TXD1__GPIO1_IO29 0x80000000

MX6QDL_PAD_EIM_D22__GPIO3_IO22 0x80000000

MX6QDL_PAD_ENET_CRS_DV__GPIO1_IO25 0x80000000

/*MX6QDL_PAD_EIM_D26__GPIO3_IO26 0x80000000*/

MX6QDL_PAD_EIM_CS1__GPIO2_IO24 0x80000000

MX6QDL_PAD_ENET_RXD0__GPIO1_IO27 0x80000000

MX6QDL_PAD_EIM_A25__GPIO5_IO02 0x80000000

MX6QDL_PAD_EIM_D23__GPIO3_IO23 0x80000000

MX6QDL_PAD_EIM_EB3__GPIO2_IO31 0x80000000

MX6QDL_PAD_SD1_CMD__GPIO1_IO18 0x80000000

MX6QDL_PAD_EIM_D16__GPIO3_IO16 0x80000000

MX6QDL_PAD_SD3_RST__GPIO7_IO08 0x80000000

MX6QDL_PAD_GPIO_9__GPIO1_IO09 0x80000000

MX6QDL_PAD_EIM_DA9__GPIO3_IO09 0x80000000

MX6QDL_PAD_NANDF_CS0__GPIO6_IO11 0x80000000

MX6QDL_PAD_NANDF_CS1__GPIO6_IO14 0x80000000

MX6QDL_PAD_NANDF_CS2__GPIO6_IO15 0x80000000

MX6QDL_PAD_NANDF_CS3__GPIO6_IO16 0x80000000

>;

};

pinctrl_audmux: audmuxgrp {

fsl,pins = <

MX6QDL_PAD_CSI0_DAT7__AUD3_RXD 0x130b0

MX6QDL_PAD_CSI0_DAT4__AUD3_TXC 0x130b0

MX6QDL_PAD_CSI0_DAT5__AUD3_TXD 0x110b0

MX6QDL_PAD_CSI0_DAT6__AUD3_TXFS 0x130b0

>;

};

pinctrl_ecspi1: ecspi1grp {

fsl,pins = <

MX6QDL_PAD_KEY_COL1__ECSPI1_MISO 0x100b1

MX6QDL_PAD_KEY_ROW0__ECSPI1_MOSI 0x100b1

MX6QDL_PAD_KEY_COL0__ECSPI1_SCLK 0x100b1

MX6QDL_PAD_KEY_ROW1__GPIO4_IO09 0x1b0b0

>;

};

pinctrl_i2c2_egalax_int: egalax_i2c2_intgrp {

fsl,pins = <

MX6QDL_PAD_NANDF_ALE__GPIO6_IO08 0x80000000

>;

};

pinctrl_i2c3_egalax_int: egalax_i2c3_intgrp {

fsl,pins = <

MX6QDL_PAD_NANDF_CLE__GPIO6_IO07 0x80000000

>;

};

pinctrl_enet: enetgrp {

fsl,pins = <

MX6QDL_PAD_ENET_MDIO__ENET_MDIO 0x1b0b0

MX6QDL_PAD_ENET_MDC__ENET_MDC 0x1b0b0

MX6QDL_PAD_RGMII_TXC__RGMII_TXC 0x1b0b0

MX6QDL_PAD_RGMII_TD0__RGMII_TD0 0x1b0b0

MX6QDL_PAD_RGMII_TD1__RGMII_TD1 0x1b0b0

MX6QDL_PAD_RGMII_TD2__RGMII_TD2 0x1b0b0

MX6QDL_PAD_RGMII_TD3__RGMII_TD3 0x1b0b0

MX6QDL_PAD_RGMII_TX_CTL__RGMII_TX_CTL 0x1b0b0

MX6QDL_PAD_ENET_REF_CLK__ENET_TX_CLK 0x1b0b0

MX6QDL_PAD_RGMII_RXC__RGMII_RXC 0x1b0b0

MX6QDL_PAD_RGMII_RD0__RGMII_RD0 0x1b0b0

MX6QDL_PAD_RGMII_RD1__RGMII_RD1 0x1b0b0

MX6QDL_PAD_RGMII_RD2__RGMII_RD2 0x1b0b0

MX6QDL_PAD_RGMII_RD3__RGMII_RD3 0x1b0b0

MX6QDL_PAD_RGMII_RX_CTL__RGMII_RX_CTL 0x1b0b0

MX6QDL_PAD_GPIO_16__ENET_REF_CLK 0x4001b0a8

>;

};

pinctrl_enet_irq: enetirqgrp {

fsl,pins = <

MX6QDL_PAD_GPIO_6__ENET_IRQ 0x000b1

>;

};

pinctrl_gpio_keys: gpio_keysgrp {

fsl,pins = <

MX6QDL_PAD_EIM_D29__GPIO3_IO29 0x1b0b0

MX6QDL_PAD_GPIO_4__GPIO1_IO04 0x1b0b0

/*

MX6QDL_PAD_GPIO_5__GPIO1_IO05 0x1b0b0

*/

>;

};

pinctrl_hdmi_cec: hdmicecgrp {

fsl,pins = <

MX6QDL_PAD_KEY_ROW2__HDMI_TX_CEC_LINE 0x108b0

>;

};

pinctrl_hdmi_hdcp: hdmihdcpgrp {

fsl,pins = <

MX6QDL_PAD_KEY_COL3__HDMI_TX_DDC_SCL 0x4001b8b1

MX6QDL_PAD_KEY_ROW3__HDMI_TX_DDC_SDA 0x4001b8b1

>;

};

pinctrl_edt_ft5x06: edt-ft5x06grp {

fsl,pins = <

MX6QDL_PAD_CSI0_DAT8__I2C1_SDA 0x4001b8b1

MX6QDL_PAD_CSI0_DAT9__I2C1_SCL 0x4001b8b1

>;

};

pinctrl_i2c1: i2c1grp {

fsl,pins = <

MX6QDL_PAD_CSI0_DAT8__I2C1_SDA 0x4001b8b1

MX6QDL_PAD_CSI0_DAT9__I2C1_SCL 0x4001b8b1

>;

};

pinctrl_i2c2: i2c2grp {

fsl,pins = <

MX6QDL_PAD_KEY_COL3__I2C2_SCL 0x4001b8b1

MX6QDL_PAD_KEY_ROW3__I2C2_SDA 0x4001b8b1

>;

};

pinctrl_flexcan1: flexcan1grp {

fsl,pins = <

MX6QDL_PAD_GPIO_7__FLEXCAN1_TX 0x1b0b0

MX6QDL_PAD_GPIO_8__FLEXCAN1_RX 0x1b0b0

>;

};

pinctrl_i2c3: i2c3grp {

fsl,pins = <

MX6QDL_PAD_GPIO_3__I2C3_SCL 0x4001b8b1

MX6QDL_PAD_GPIO_6__I2C3_SDA 0x4001b8b1

>;

};

pinctrl_ipu1: ipu1grp {

fsl,pins = <

MX6QDL_PAD_DI0_DISP_CLK__IPU1_DI0_DISP_CLK 0x10

MX6QDL_PAD_DI0_PIN15__IPU1_DI0_PIN15 0x10

MX6QDL_PAD_DI0_PIN2__IPU1_DI0_PIN02 0x10

MX6QDL_PAD_DI0_PIN3__IPU1_DI0_PIN03 0x10

MX6QDL_PAD_DI0_PIN4__IPU1_DI0_PIN04 0x80000000

MX6QDL_PAD_DISP0_DAT0__IPU1_DISP0_DATA00 0x10

MX6QDL_PAD_DISP0_DAT1__IPU1_DISP0_DATA01 0x10

MX6QDL_PAD_DISP0_DAT2__IPU1_DISP0_DATA02 0x10

MX6QDL_PAD_DISP0_DAT3__IPU1_DISP0_DATA03 0x10

MX6QDL_PAD_DISP0_DAT4__IPU1_DISP0_DATA04 0x10

MX6QDL_PAD_DISP0_DAT5__IPU1_DISP0_DATA05 0x10

MX6QDL_PAD_DISP0_DAT6__IPU1_DISP0_DATA06 0x10

MX6QDL_PAD_DISP0_DAT7__IPU1_DISP0_DATA07 0x10

MX6QDL_PAD_DISP0_DAT8__IPU1_DISP0_DATA08 0x10

MX6QDL_PAD_DISP0_DAT9__IPU1_DISP0_DATA09 0x10

MX6QDL_PAD_DISP0_DAT10__IPU1_DISP0_DATA10 0x10

MX6QDL_PAD_DISP0_DAT11__IPU1_DISP0_DATA11 0x10

MX6QDL_PAD_DISP0_DAT12__IPU1_DISP0_DATA12 0x10

MX6QDL_PAD_DISP0_DAT13__IPU1_DISP0_DATA13 0x10

MX6QDL_PAD_DISP0_DAT14__IPU1_DISP0_DATA14 0x10

MX6QDL_PAD_DISP0_DAT15__IPU1_DISP0_DATA15 0x10

MX6QDL_PAD_DISP0_DAT16__IPU1_DISP0_DATA16 0x10

MX6QDL_PAD_DISP0_DAT17__IPU1_DISP0_DATA17 0x10

MX6QDL_PAD_DISP0_DAT18__IPU1_DISP0_DATA18 0x10

MX6QDL_PAD_DISP0_DAT19__IPU1_DISP0_DATA19 0x10

MX6QDL_PAD_DISP0_DAT20__IPU1_DISP0_DATA20 0x10

MX6QDL_PAD_DISP0_DAT21__IPU1_DISP0_DATA21 0x10

MX6QDL_PAD_DISP0_DAT22__IPU1_DISP0_DATA22 0x10

MX6QDL_PAD_DISP0_DAT23__IPU1_DISP0_DATA23 0x10

>;

};

pinctrl_ipu1_2: ipu1grp-2 { /* parallel camera */

fsl,pins = <

MX6QDL_PAD_CSI0_DAT12__IPU1_CSI0_DATA12 0x80000000

MX6QDL_PAD_CSI0_DAT13__IPU1_CSI0_DATA13 0x80000000

MX6QDL_PAD_CSI0_DAT14__IPU1_CSI0_DATA14 0x80000000

MX6QDL_PAD_CSI0_DAT15__IPU1_CSI0_DATA15 0x80000000

MX6QDL_PAD_CSI0_DAT16__IPU1_CSI0_DATA16 0x80000000

MX6QDL_PAD_CSI0_DAT17__IPU1_CSI0_DATA17 0x80000000

MX6QDL_PAD_CSI0_DAT18__IPU1_CSI0_DATA18 0x80000000

MX6QDL_PAD_CSI0_DAT19__IPU1_CSI0_DATA19 0x80000000

MX6QDL_PAD_CSI0_DATA_EN__IPU1_CSI0_DATA_EN 0x80000000

MX6QDL_PAD_CSI0_PIXCLK__IPU1_CSI0_PIXCLK 0x80000000

MX6QDL_PAD_CSI0_MCLK__IPU1_CSI0_HSYNC 0x80000000

MX6QDL_PAD_CSI0_VSYNC__IPU1_CSI0_VSYNC 0x80000000

MX6QDL_PAD_SD1_DAT1__GPIO1_IO17 0x80000000

MX6QDL_PAD_SD1_DAT0__GPIO1_IO16 0x80000000

>;

};

pinctrl_pcie: pciegrp {

fsl,pins = <

MX6QDL_PAD_GPIO_17__GPIO7_IO12 0x1b0b0

>;

};

pinctrl_pcie_reg: pciereggrp {

fsl,pins = <

MX6QDL_PAD_EIM_D19__GPIO3_IO19 0x1b0b0

>;

};

pinctrl_pwm1: pwm1grp {

fsl,pins = <

MX6QDL_PAD_SD1_DAT3__PWM1_OUT 0x1b0b1

>;

};

pinctrl_uart1: uart1grp {

fsl,pins = <

/*MX6QDL_PAD_CSI0_DAT10__UART1_TX_DATA 0x1b0b1

MX6QDL_PAD_CSI0_DAT11__UART1_RX_DATA 0x1b0b1*/

MX6QDL_PAD_SD3_DAT7__UART1_TX_DATA 0x1b0b1

MX6QDL_PAD_SD3_DAT6__UART1_RX_DATA 0x1b0b1

>;

};

pinctrl_uart2: uart2grp{

fsl,pins = <

MX6QDL_PAD_EIM_D26__UART2_TX_DATA 0x1b0b1

MX6QDL_PAD_EIM_D27__UART2_RX_DATA 0x1b0b1

>;

};

pinctrl_uart4: uart4grp{

fsl,pins = <

MX6QDL_PAD_KEY_COL0__UART4_TX_DATA 0x1b0b1

MX6QDL_PAD_KEY_ROW0__UART4_RX_DATA 0x1b0b1

>;

};

pinctrl_uart5_1: uart5grp-1 {

fsl,pins = <

MX6QDL_PAD_KEY_COL1__UART5_TX_DATA 0x1b0b1

MX6QDL_PAD_KEY_ROW1__UART5_RX_DATA 0x1b0b1

MX6QDL_PAD_KEY_COL4__UART5_RTS_B 0x1b0b1

MX6QDL_PAD_KEY_ROW4__UART5_CTS_B 0x1b0b1

>;

};

pinctrl_uart5dte_1: uart5dtegrp-1 {

fsl,pins = <

MX6QDL_PAD_KEY_ROW1__UART5_TX_DATA 0x1b0b1

MX6QDL_PAD_KEY_COL1__UART5_RX_DATA 0x1b0b1

MX6QDL_PAD_KEY_ROW4__UART5_RTS_B 0x1b0b1

MX6QDL_PAD_KEY_COL4__UART5_CTS_B 0x1b0b1

>;

};

pinctrl_usbotg: usbotggrp {

fsl,pins = <

MX6QDL_PAD_ENET_RX_ER__USB_OTG_ID 0x17059

>;

};

pinctrl_usdhc2: usdhc2grp {

fsl,pins = <

MX6QDL_PAD_SD2_CMD__SD2_CMD 0x17059

MX6QDL_PAD_SD2_CLK__SD2_CLK 0x10059

MX6QDL_PAD_SD2_DAT0__SD2_DATA0 0x17059

MX6QDL_PAD_SD2_DAT1__SD2_DATA1 0x17059

MX6QDL_PAD_SD2_DAT2__SD2_DATA2 0x17059

MX6QDL_PAD_SD2_DAT3__SD2_DATA3 0x17059

/*

MX6QDL_PAD_NANDF_D4__SD2_DATA4 0x17059

MX6QDL_PAD_NANDF_D5__SD2_DATA5 0x17059

MX6QDL_PAD_NANDF_D6__SD2_DATA6 0x17059

MX6QDL_PAD_NANDF_D7__SD2_DATA7 0x17059

*/

>;

};

pinctrl_usdhc3: usdhc3grp {

fsl,pins = <

MX6QDL_PAD_SD3_CMD__SD3_CMD 0x17059

MX6QDL_PAD_SD3_CLK__SD3_CLK 0x10059

MX6QDL_PAD_SD3_DAT0__SD3_DATA0 0x17059

MX6QDL_PAD_SD3_DAT1__SD3_DATA1 0x17059

MX6QDL_PAD_SD3_DAT2__SD3_DATA2 0x17059

MX6QDL_PAD_SD3_DAT3__SD3_DATA3 0x17059

MX6QDL_PAD_SD3_DAT4__SD3_DATA4 0x17059

MX6QDL_PAD_SD3_DAT5__SD3_DATA5 0x17059

/*

MX6QDL_PAD_SD3_DAT6__SD3_DATA6 0x17059

MX6QDL_PAD_SD3_DAT7__SD3_DATA7 0x17059

*/

>;

};

pinctrl_usdhc4: usdhc4grp {

fsl,pins = <

MX6QDL_PAD_SD4_CMD__SD4_CMD 0x17059

MX6QDL_PAD_SD4_CLK__SD4_CLK 0x10059

MX6QDL_PAD_SD4_DAT0__SD4_DATA0 0x17059

MX6QDL_PAD_SD4_DAT1__SD4_DATA1 0x17059

MX6QDL_PAD_SD4_DAT2__SD4_DATA2 0x17059

MX6QDL_PAD_SD4_DAT3__SD4_DATA3 0x17059

MX6QDL_PAD_SD4_DAT4__SD4_DATA4 0x17059

MX6QDL_PAD_SD4_DAT5__SD4_DATA5 0x17059

MX6QDL_PAD_SD4_DAT6__SD4_DATA6 0x17059

MX6QDL_PAD_SD4_DAT7__SD4_DATA7 0x17059

>;

};

pinctrl_wdog: wdoggrp {

fsl,pins = <

MX6QDL_PAD_GPIO_1__WDOG2_B 0x80000000

>;

};

};

gpio_leds {

pinctrl_gpio_leds: gpioledsgrp {

fsl,pins = <

MX6QDL_PAD_GPIO_2__GPIO1_IO02 0x1b0b0

>;

};

};

};

&ldb {

status = "okay";

lvds-channel@0 {

fsl,data-mapping = "spwg";

fsl,data-width = <18>;

status = "okay";

display-timings {

native-mode = <&timing0>;

timing0: hsd100pxn1 {

clock-frequency = <65000000>;

hactive = <1024>;

vactive = <768>;

hback-porch = <220>;

hfront-porch = <40>;

vback-porch = <21>;

vfront-porch = <7>;

hsync-len = <60>;

vsync-len = <10>;

};

};

};

lvds-channel@1 {

fsl,data-mapping = "spwg";

fsl,data-width = <18>;

primary;

status = "okay";

display-timings {

native-mode = <&timing1>;

timing1: hsd100pxn1 {

clock-frequency = <65000000>;

hactive = <1024>;

vactive = <768>;

hback-porch = <220>;

hfront-porch = <40>;

vback-porch = <21>;

vfront-porch = <7>;

hsync-len = <60>;

vsync-len = <10>;

};

};

};

};

&mipi_csi {

status = "okay";

ipu_id = <0>;

csi_id = <1>;

v_channel = <0>;

lanes = <2>;

};

&mipi_dsi {

dev_id = <0>;

disp_id = <1>;

lcd_panel = "TRULY-WVGA";

disp-power-on-supply = <®_mipi_dsi_pwr_on>;

resets = <&mipi_dsi_reset>;

status = "okay";

};

&pcie {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_pcie>;

reset-gpio = <&gpio7 12 0>;

status = "okay";

};

&pwm1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_pwm1>;

status = "okay";

};

&snvs_poweroff {

status = "okay";

};

&ssi2 {

status = "okay";

};

&uart1 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart1>;

status = "okay";

};

&uart2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart2>;

status = "okay";

};

&uart4 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_uart4>;

status = "okay";

};

&usbh1 {

vbus-supply = <®_usb_h1_vbus>;

status = "okay";

};

&usbotg {

vbus-supply = <®_usb_otg_vbus>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usbotg>;

disable-over-current;

srp-disable;

hnp-disable;

adp-disable;

status = "okay";

};

&usbphy1 {

tx-d-cal = <0x5>;

};

&usbphy2 {

tx-d-cal = <0x5>;

};

&usdhc2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usdhc2>;

bus-width = <8>;

cd-gpios = <&gpio2 4 GPIO_ACTIVE_HIGH>;

wp-gpios = <&gpio2 2 GPIO_ACTIVE_LOW>;

no-1-8-v;

keep-power-in-suspend;

enable-sdio-wakeup;

status = "okay";

};

&usdhc3 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usdhc3>;

bus-width = <8>;

cd-gpios = <&gpio2 0 GPIO_ACTIVE_LOW>;

wp-gpios = <&gpio2 1 GPIO_ACTIVE_LOW>;

no-1-8-v;

keep-power-in-suspend;

enable-sdio-wakeup;

status = "okay";

};

&usdhc4 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_usdhc4>;

bus-width = <8>;

non-removable;

no-1-8-v;

keep-power-in-suspend;

status = "okay";

};

&wdog1 {

status = "disabled";

};

&wdog2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_wdog>;

fsl,wdog_b;

status = "okay";

};

/*dts文件*/

/*

* Copyright 2012=2015 Freescale Semiconductor, Inc.

* Copyright 2011 Linaro Ltd.

*

* The code contained herein is licensed under the GNU General Public

* License. You may obtain a copy of the GNU General Public License

* Version 2 or later at the following locations:

*

* http://www.opensource.org/licenses/gpl-license.html

* http://www.gnu.org/copyleft/gpl.html

*/

/dts-v1/;

#include "imx6q.dtsi"

#include "imx6q-krt.dtsi"/*这里引用了上面的dtsi设备树头文件,逻辑上这里应该更倾向于需要定制的部分,不过我把两个文件都单独写了,也就没有分的那么清楚*/

/ {

model = "Freescale i.MX6 Quad SABRE Smart Device Board";

compatible = "fsl,imx6q-sabresd", "fsl,imx6q";

};

&battery {

offset-charger = <1900>;

offset-discharger = <1694>;

offset-usb-charger = <1685>;

};

&ldb {

lvds-channel@0 {

crtc = "ipu2-di0";

};

lvds-channel@1 {

crtc = "ipu2-di1";

};

};

&mxcfb1 {

status = "okay";

};

&mxcfb2 {

status = "okay";

};

&mxcfb3 {

status = "okay";

};

&mxcfb4 {

status = "okay";

};

&sata {

status = "okay";

};

测试接收can数据,bitrate 500000//波特率500k

root@imx6qsabresd:~# ifconfig can0 down//需要先关闭can设备才能设置参数

root@imx6qsabresd:~# ip link set can0 type can bitrate 500000 triple-sampling on

root@imx6qsabresd:~# ifconfig can0 up

flexcan 2090000.flexcan can0: writing ctrl=0x13292085

root@imx6qsabresd:~# candump can0

can0 000 [8] 00 01 02 03 04 05 06 07

can0 000 [8] 00 01 02 03 04 05 06 07

can0 000 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 123 [8] 00 01 02 03 04 05 06 07

can0 122 [8] 00 01 02 03 04 05 06 08

root@imx6qsabresd:~# cansend can0 123#00 01 02 03 04 05 06 0 08//发送一帧 ID为123中间用“#”隔开后面接数据,数据默认是hex格式的,0x可以省略。

// 修改 /etc/network/interfaces 追加下面命令

auto can0

iface can0 inet manual

pre-up /sbin/ip link set $IFACE type can bitrate 500000 triple-sampling on restart-ms 10

up /sbin/ifconfig $IFACE up

down /sbin/ifconfig $IFACE down

ip -details link show can0//使用此命令查看设备信息

ip -details -statistics link show can0 //使用此命令查看can总线状态