stm32系统时钟详解&&移植

写作原由:今日接手用stm32f100xx芯片开发的项目,以前用的是stm8s 和stm32f103xx芯片;因为在别人的项目代码的基础上做2次开发,但是发现那个代码main函数中没有对系统时钟的设置的相关函数,一直纳闷,但也没有深究,直至昨日 调试时出现串口收发数据出错,源代码在原项目的板子上串口发送、接收数据正常,同样程序在项目板子上收发的数据不正确, 两块板子芯片一样,串口收发管脚一样,最后发现原来板子外部晶振是8MHZ ,新板子外部晶振是12MHZ; 而在STM32固件库中,默认的外部晶振是8MHZ,由于时钟源不正确,导致波特率不正确,当然收发的数据也不正确了.....我勒个去!都怪自己平时看问题“不求甚解”。

(波特率与时钟源关系公式:IntegerDivider = ((PCLKx) / (16 * (USART_InitStruct->USART_BaudRate)))

为了深入思考,我提出了一些疑问,通过解答这些问题更深入的了解时钟;

问题一:对系统时钟的设置的相关函数,在main函数中找不到,那在哪里?还是说根本没有对系统时钟进行配置?

问题二:既然用了外部晶振做系统时钟,那为什么没看到启动外部晶振的操作?

问题三:串口的时钟源是什么?串口时钟源跟系统时钟的关系?

问题四:程序中串口时钟源是怎样实现对波特率的关系的?

现附上我找到上面3个问题答案做的一张框架图:希望博友参考此图理解我后面的内容:

在进入主题之前我们先了解一些必要的基础知识----stm32系列芯片的种类和型号:

startup_stm32f10x_hd.s 大容量的STM32F101xx,STM32F102xx,STM32F103xx

startup_stm32f10x_hd_vl.s 大容量的STM32F100xx

startup_stm32f10x_ld.s 小容量的STM32F101xx,STM32F102xx,STM32F103xx

startup_stm32f10x_ld_vl.s 小容量的STM32F100xx

startup_stm32f10x_md.s 中容量的STM32F101xx,STM32F102xx,STM32F103xx

startup_stm32f10x_md_vl.s 中容量的STM32F100xx (我项目中用的是此款芯片 stm32f100CB)

startup_stm32f10x_xl.s FLASH在512K到1024K字节的STM32F101xx,STM32F102xx,STM32F103xx

cl:互联型产品,stm32f105/107系列

vl:超值型产品,stm32f100系列

xl:超高密度产品,stm32f101/103系列

ld:低密度产品,FLASH小于64K

md:中等密度产品,FLASH=64 or 128

hd:高密度产品,FLASH大于128

(下图中的startup_stm32f10_ld.s应改为:startup_stm32f10x_md_vl.s)

问题一:对系统时钟的设置的相关函数,在main函数中找不到,那在哪里?还是说根本没有对系统时钟进行配置?

解答:高人指点,我看了一下启动文件startup_stm32f10x_md_vl.s,其中有一段汇编:

; Reset handler routine

Reset_Handler PROC

EXPORT Reset_Handler [WEAK]

IMPORT __main

IMPORT SystemInit

LDR R0, =SystemInit

BLX R0

LDR R0, =__main

BX R0

ENDP

其中,

IMPORT __main IMPORT SystemInit //IMPORT 声明了需要引用C语言中的main函数、systeminit函数,

LDR R0, = systeminint //把systeminit 函数地址放到r0 寄存器;

BLX R0 //跳到到R0 寄存器中的地址执行;

所以,在跳到main函数执行前,已经在SystemInit 函数中把系统时钟给设置好了;

问题二:既然用了外部晶振做系统时钟,那为什么没看到启动外部晶振的操作?

我们在解答这个问题前,先到SystemInit函数里面做更深入的了解:

void SystemInit (void)

{

/* Reset the RCC clock configuration to the default reset state(for debug purpose) */

/* Set HSION bit */

RCC->CR |= (uint32_t)0x00000001;

/* Reset SW, HPRE, PPRE1, PPRE2, ADCPRE and MCO bits */

#ifndef STM32F10X_CL

RCC->CFGR &= (uint32_t)0xF8FF0000;

#else

RCC->CFGR &= (uint32_t)0xF0FF0000;

#endif /* STM32F10X_CL */

/* Reset HSEON, CSSON and PLLON bits */

RCC->CR &= (uint32_t)0xFEF6FFFF;

/* Reset HSEBYP bit */

RCC->CR &= (uint32_t)0xFFFBFFFF;

/* Reset PLLSRC, PLLXTPRE, PLLMUL and USBPRE/OTGFSPRE bits */

RCC->CFGR &= (uint32_t)0xFF80FFFF;

#ifdef STM32F10X_CL

/* Reset PLL2ON and PLL3ON bits */

RCC->CR &= (uint32_t)0xEBFFFFFF;

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x00FF0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL)

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

/* Reset CFGR2 register */

RCC->CFGR2 = 0x00000000;

#else

/* Disable all interrupts and clear pending bits */

RCC->CIR = 0x009F0000;

#endif /* STM32F10X_CL */

/* Configure the System clock frequency, HCLK, PCLK2 and PCLK1 prescalers */

/* Configure the Flash Latency cycles and enable prefetch buffer */

SetSysClock();

#ifdef STM32F10X_HD

#ifdef DATA_IN_ExtSRAM

SystemInit_ExtMemCtl();

#endif /* DATA_IN_ExtSRAM */

#endif /* STM32F10X_HD */

}我们进入setsysclock()函数,看其中作了哪些操作:

/**

* @brief Configures the System clock frequency, HCLK, PCLK2 and PCLK1 prescalers.

* @param None

* @retval None

*/

static void SetSysClock(void)

{

#ifdef SYSCLK_FREQ_HSE

SetSysClockToHSE();

#elif defined SYSCLK_FREQ_24MHz

SetSysClockTo24();

#elif defined SYSCLK_FREQ_36MHz

SetSysClockTo36();

#elif defined SYSCLK_FREQ_48MHz

SetSysClockTo48();

#elif defined SYSCLK_FREQ_56MHz

SetSysClockTo56();

#elif defined SYSCLK_FREQ_72MHz

SetSysClockTo72();

#endif

我项目中用的是此款芯片 stm32f100CB,内部晶振是24MHZ, 所以应进入执行SetSysClockTo24() 函数:

/**

* @brief Sets System clock frequency to 24MHz and configure HCLK, PCLK2

* and PCLK1 prescalers.

* @note This function should be used only after reset.

* @param None

* @retval None

*/

static void SetSysClockTo24(void)

{

__IO uint32_t StartUpCounter = 0, HSEStatus = 0;

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

/* Enable HSE */

RCC->CR |= ((uint32_t)RCC_CR_HSEON); //开启外部晶振

/* Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSEStartUp_TimeOut));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)//等待外部晶振起振

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

if (HSEStatus == (uint32_t)0x01)

{

#if !defined STM32F10X_LD_VL && !defined STM32F10X_MD_VL

/* Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/* Flash 0 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_0;

#endif

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1;

#ifdef STM32F10X_CL

/* Configure PLLs ------------------------------------------------------*/

/* PLL configuration: PLLCLK = PREDIV1 * 6 = 24 MHz */

RCC->CFGR &= (uint32_t)~(RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLSRC | RCC_CFGR_PLLMULL);

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLXTPRE_PREDIV1 | RCC_CFGR_PLLSRC_PREDIV1 |

RCC_CFGR_PLLMULL6);

/* PLL2 configuration: PLL2CLK = (HSE / 5) * 8 = 40 MHz */

/* PREDIV1 configuration: PREDIV1CLK = PLL2 / 10 = 4 MHz */

RCC->CFGR2 &= (uint32_t)~(RCC_CFGR2_PREDIV2 | RCC_CFGR2_PLL2MUL |

RCC_CFGR2_PREDIV1 | RCC_CFGR2_PREDIV1SRC);

RCC->CFGR2 |= (uint32_t)(RCC_CFGR2_PREDIV2_DIV5 | RCC_CFGR2_PLL2MUL8 |

RCC_CFGR2_PREDIV1SRC_PLL2 | RCC_CFGR2_PREDIV1_DIV10);

/* Enable PLL2 */

RCC->CR |= RCC_CR_PLL2ON;

/* Wait till PLL2 is ready */

while((RCC->CR & RCC_CR_PLL2RDY) == 0)

{

}

#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL)

/* PLL configuration: = (HSE / 2) * 6 = 24 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_PREDIV1 | RCC_CFGR_PLLXTPRE_PREDIV1_Div2 | RCC_CFGR_PLLMULL6);

#else

/* PLL configuration: = (HSE / 2) * 6 = 24 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE | RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLXTPRE_HSE_Div2 | RCC_CFGR_PLLMULL6);

#endif /* STM32F10X_CL */

/* Enable PLL */

RCC->CR |= RCC_CR_PLLON;

/* Wait till PLL is ready */

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* Wait till PLL is used as system clock source */

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

}

else

{ /* If HSE fails to start-up, the application will have wrong clock

configuration. User can add here some code to deal with this error */

}

}

#elif defined SYSCLK_FREQ_36MHz解析:

void SetSysClockTo24函数中主要做了下面几件事:(不同颜色功能分别对应上面对应颜色代码部分)

1.启动外部晶振作为系统时钟源;

2.等待外部晶振起振;

3.(起振后)对系统时钟源进行分频:(默认外部是HSE--8MHZ晶振) PLL configuration: = (HSE / 2) * 6 = 24 MHz

4. 配置HCLK、PCLK1、PCLK2 与系统时钟源的关系;

问题三:串口的时钟源是什么?串口时钟源跟系统时钟的关系?

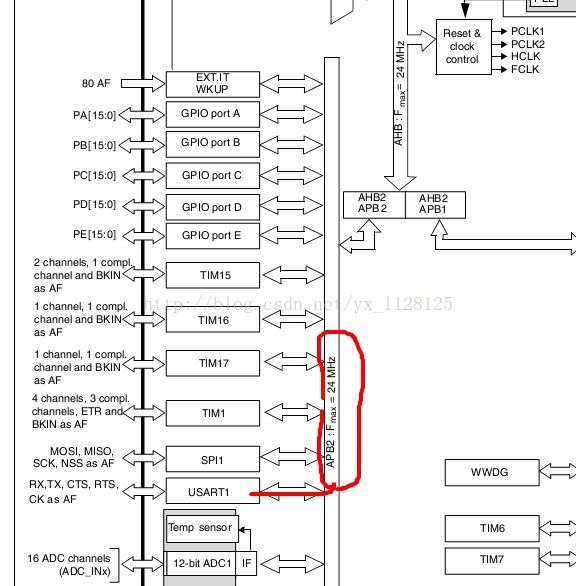

回答这个问题前,我们先来看stm32f100芯片手册数据图(第12页):

从图里面我们可看出串口1的时钟源是PCLK1;

上面问题2的代码中我们看到PCLK1是时钟源24MHZ的1分频,即还是24MHZ;

问题四:程序中串口时钟源是怎样实现对波特率的关系的?

由问题3我们知道串口时钟源是24mhz,依据公式:IntegerDivider = ((PCLKx) / (16 * (USART_InitStruct->USART_BaudRate)))

库中自动设置IntegerDivider 存入寄存器中;

附加: 转自http://blog.sina.com.cn/s/blog_542bad910101g1gu.html

(1)

在KEIL下可以在项目的选项C/C++/PREPROMCESSOR symbols的Define栏里定义,比如STM32F10X_CL

#define STM32F10X_HD

#endif

如果芯片更换,除了做如上所述的更改外,还需以下几步

#define SYSCLK_FREQ_24MHz 24000000

#else

#define SYSCLK_FREQ_72MHz 72000000

#endif

其中填入

D:\Keil\ARM\BIN40\fromelf.exe --bin -o ./obj/Project.bin ./obj/Project.axf

其中,Project.bin 和 Project.axf 要和 Output 选项卡中的 Name of Executable 的名字

if (*(uint32_t*)address!= dat)//字编程后校验