NAND-eMMC-SPINOR-SSD知识

1 NAND Flash

1.1 NAND Commands

read1:命令代码是00h/01h,分别读取上半页(A区)和下半页(B区)

read2:命令代码是50h,读取oob(C区)

第一个命令00h用来设置区域为0-255bytes的指针(A区)

第二个命令01h用来设置区域为256-511bytes的指针(B区)

第三个命令50h用来设置区域为512-527bytes的指针(C区)

nand flash一上电就进入read1 00h模式,所用page的528bytes数据会在12us内传输到数据寄存器。

1.2 BBT/BBM - Bad Block Management

BBT一般放在block 0,因为第一块由厂家保证一定是好的,小页512字节的Nand OOB的第6个字节(大页2K的OOB第1个字节)表示是不是坏块(0xff表示好块,0x00表示坏块);SPI Flash的第一块或者最后一块一定是好的。

Figure 1-1 Uboot的2种坏块管理方法对比

Figure 1-2 BBT/SBT映射示意图

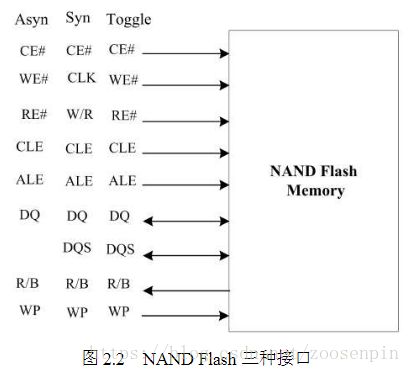

1.3 NAND Flash三种接口 - Legacy/ONFI/Toggle DDR

Figure 1-3 NAND Flash三种接口对比

Figure 1-4 NAND Flash三种接口信号说明

1.4 SLC和MLC Nand使用的文件系统

SLC时代,与其一起成长的软件技术有YAFFS/YAFFS2,它是第一个专门为Nand设计的,并具有WL(Wear Leveling)和POR(Power off Recovery)功能的嵌入式文件系统;以及JFFS/JFFS2,建立可以挂载Nand Driver的MTD设备之上的日志文件系统。

随着容量的增加,MLC技术的到来,JFFS2的继往开来者UBIFS/UBI也随之到来,还有与其形成竞争关系的LogFS。

2 eMMC/SD

2.1 支持的频率种类(达到最大数据速率的前提是8根DATx)

Legacy SDR:26MHz,max_dtr - 26MB/s

HS SDR:High Speed Single Data Rate 52MHz,max_dtr - 52MB/s

HS DDR:High Speed Double Data Rate 104MHz,max_dtr - 104MB/s

HS200:High Speed 200MHz,max_dtr - 200MB/s

HS400:High Speed 400MHz,需要Data Strobe信号,max_dtr - 400MB/s

2.2 命令和响应

2.2.1 命令

eMMC命令寄存器bit13-8:表示opcode,CMD0-63、ACMD0-63

eMMC超时寄存器bit3-0:表示DAT0-DAT3,哪个数据线超时

ACMD:Application Command

2.2.2 响应

R1b和R1的区别:在DAT0上存在忙信号(busy)的传输,R1的bit7表示响应包中CRC是否有错误,1表示有,否则没有

2.3 eMMC/SD初始化流程

1)配置时钟,慢速一般为400K,设置工作模式

2)发送CMD0,进入空闲态,该指令没有反馈

3)发送CMD8,如果有反应,CRC值与发送的值相同,说明该卡兼容SD2.0协议

4)发送CMD55+ACMD41,判断SD卡的上电是否正确,短反馈成功说明该卡为SD卡(短反馈第31位置1为HC卡),否则发送CMD0,有反应说明是MMC卡

5)发送CMD2,验证SD卡是否接入,长反馈CID(Card IDentification Register)

6)发送CMD3,读取SD卡的RCA(地址,Relative Card Address),短反馈

7)发送CMD9,读取CSD(Card Specific Data Register)寄存器获取卡的相关信息

8)发送CMD7,使能SD卡

9)配置高速时钟,准备数据传输,一般20M~25M

10)发送CMD55+ACMD51读取SCR(SD Card Configuration Register)寄存器,SD卡可以通过该值获得位宽,如果是MMC卡则需要使用主线测试来确定卡的位宽

11)SD卡发送CMD55+ACMD6配置为4bit数据传输模式(根据SCR读出来的值确定),MMC卡发送CMD6来设置位宽

12)发送CMD7,使能SD卡,使其进入传输状态,接着发送CMD16设置块大小(根据前面读取的CSD信息确定)

13) 把命令参数设置为0,再次发送CMD7,取消选中所有卡

Figure 2-1 SD卡的初始化和识别流程

2.4 eMMC5.1速度调试

2.4.1 速度调试

eMMC5.1支持的速度模式:DDR50、HS200 SDR、HS200 DDR(也叫HS400),代码中的配置如下例所示。

@ drivers/mmc/host/sdhci-pci-core.c

caps:MMC_CAP_1_8V_DDR

caps2:MMC_CAP2_HS400_1_8V | MMC_CAP2_HS200_1_8V_SDR

eMMC DTR低速的工作电压是3.3V,高速1.8V。类似于USB,低速全速DPDM是3.3V,高速DPDM是400mV。

@ drivers/mmc/core/mmc.c

mmc_attach_mmc(struct mmc_host *host); - eMMC异常时需要debug该函数

mmc_select_driver_type(struct mmc_card *card); - 设置驱动能力MMC_SET_DRIVER_TYPE_A{C/D}等类型

2.4.2 eMMC卡调试路径

/sys/class/mmc_host/mmcN/mmcN:00001

/sys/kernel/debug/mmcN

2.4.3 eMMC用户分区挂载路径

第一次挂载路径:

/mnt/media_rw/

第二次挂载路径(使用mount的bind方式):

/mnt/runtime/default

/mnt/runtime/read

/mnt/runtime/write

2.5 eMMC分区应用实例

Android手机系统中,各个分区的呈现形式如下:

- mmcblk0为eMMC的块设备

- mmcblk0boot0和mmcblk0boot1对应两个Boot Area Partitions

- mmcblk0rpmb则为RPMB Partition(Replay Protected Memory Block,具有安全特性的分区,猜想指纹数据就是放在这个分区)

- mmcblk0px为UDA(User Data Area)划分出来的SW Partitions

- 如果存在GPP(General Purpose Partitions),名称则为mmcblk0gp1、mmcblk0gp2、mmcblk0gp3、mmcblk0gp4

2.6 FFU - Field Firmware Update

eMMC Firmware Upgrade

https://blog.csdn.net/jgw2008/article/details/52555279

emmc field firmware update

https://blog.csdn.net/u013531497/article/details/43114805

2.7 eMMC芯片架构ARC

PS3105-S5:Phison(Phison = “Five-Person”, 由五位Flash 研发经验超过14年专业人士创立),群联,采用ARC的SSD主控;该公司提供eMMC、UFS和SSD全系列控制器

SM2246EN:Silicon Motion, Inc.,慧荣科技,采用ARC的SSD主控;该公司提供eMMC、UFS和SSD全系列控制器

SiliconGo/YEESTOR:硅格半导体;该公司提供eMMC、UFS和SSD全系列控制器

emmc总结

https://blog.csdn.net/qingfengtsing/article/details/50338403

2.8 SPI模式

SPI通信模式共有0~3四种,他们的区别是时钟相位和极性。适用于MMC和SD的模式是mode 0(CPHA=0,CPOL=0),但是mode 3多数情况下也管用。

SPI总线有四种工作方式,哪几种最为广泛

http://m.elecfans.com/article/569374.html

2.9 command queuing

2.9.1 CSD寄存器

struct mmc_ext_csd {}

card->ext_csd.cmdq_en

kernel parameter:mmc_cmdqueue=off

ps -A | grep mmc

2.9.2 URLs

eMMC and Extended CSD Registers

https://blog.kylemanna.com/linux/parse-emmc-extended-csd-ecsd-registers-with-python/

2.10 Tools

external/mmc-utils/

read_extcsd

do_ffu (it is only for kernel version >= 4.4)

e2label

2.11 编程器

P800Flash

3 SPI Flash之Top-Boot or Bottom-Boot

顶部和底部启动设备启动代码和定制数据的大小一般比标准块小很多,为了避免浪费宝贵的空间,很多Flash ROM把第一块或最后一块分割为更小的子块,例如8KB。这使你更好的控制这些块的内容。

依赖于启动代码在ROM中的所在位置,这些设备有两种风格:顶部启动和底部启动设备。这取决于CPU在重启动/加电后从哪里获取指令:不论是存储空间顶部(例如Intel)或者存储空间底部(例如Motorola)。一些Flash ROM可通过外部端脚来配置顶部或底部启动。

举例说明top和bottom的区别:

总结:Top boot类型的Flash的小块(block)放在高地址位上,而Bottom boot类型的flash的小块(block)起始位置为0x000000.

4 SSD

4.1 FTL - Flash Translation Layer

NAND FLASH均衡算法笔记

http://blog.chinaunix.net/xmlrpc.php?r=blog/article&uid=26716973&id=4009646

4.2 SSD芯片架构

MGX:Samsung

5 UFS固件

UFS固件分成如下的三部分:

- 前端,host接口协议

- 中端,FTL(Flash Transport Layer)算法

- 后端,NFC(Nand Flash Controller)驱动

6 URLs

nand flash驱动编写与移植

https://wenku.baidu.com/view/f4693ed3240c844769eaee09.html

7 Abbreviations

MISO:mi s əu

MOSI:m əu si

QUP:高通平台的SPI总线和I2C共用core和引脚,称为QUP(QCOM Universal Peripheral);而UART和QUP又共用引脚,并且称为BLSP

DQS:Data Query Strobe,时钟CLK是被用来指引命令和地址的传输;而数据阀门信号DQS则是用来指引数据应该被传输到哪里去。DQS是一个双向总线,也是由和时钟同样的频率来进行驱动。

MfgTool:Manufacturing Tool

ONFI:Open NAND Flash Interface,上电时异步模式,下指令切换到同步模式(有CLK信号)

P/E循环:Nand Flash编程/擦除次数

R/B#:Ready/Busy#

Nand Flash RBA:Reserve Block Area,预留块区

POR:Nand Flash Power off Recovery,掉电恢复

SAS:Serial Attached SCSI

SAM:SCSI Architecture Model

SPC:SCSI Primary Commands,基础指令集

SBC:SCSI Block Commands,特定设备指令集

TA:Trusted Application

VCCQ:VCC Quality,nand flash的供电电压