计算机组成原理实验四

上机实验04 逻辑运算编程实验

一、实验要求和目的

1.了解汇编语言的逻辑运算指令;

2.熟悉汇编语言中逻辑运算指令的使用方法;

3.掌握利用汇编语言逻辑运算指令实现程序设计的方法。

二、软硬件环境

1.硬件环境:微机CPU 486以上,500MB以上硬盘,32M以上内存;

2.软件环境:装有MASM 5.0、DEBUG、LINK和EDIT等应用程序。

三、实验涉及的主要知识单元

1.逻辑非指令NOT

格式:NOT OPD

操作形式:OPD←。

描述:

指令的功能是把操作数中的每位变反,即:1←0,0←1。将目的地址中的内容逐位取反后送入目的地址。操作数不能用立即数,指令执行后对标志位无影响,也可用于求补。

举例:

MOV AX,1234H ;(AX)=1234H

NOT AX ;(AX)=EDCBH

2.逻辑与指令AND

格式:AND 目的操作数,源操作数

操作形式:DOPD ← DOPD∧SOPD。

描述:

(1)逻辑与运算法则为1∧1=1,1∧0=0,0∧1=0,0∧0=0。

(2)指令的功能是把源操作数中的每位二进制与目的操作数中的相应二进制进行逻辑乘运算操作,操作结果存入目的操作数中。

(3)受影响的标志位:CF、OF为0,PF、SF和ZF根据运算定, AF无定义。

(4)利用AND指令与0或1相与可对操作数的某些位进行屏蔽和保留操作。

举例:

将AL中第0位和第7位清零。

MOV AL,0FFH

AND AL,7EH

3.逻辑或指令OR

格式:OR 目的操作数,源操作数

操作形式:DOPD ← DOPD∨SOPD

描述:

(1)逻辑或运算法则:1∨1=1,1∨0=1,0∨1=1,0∨0=0。

(2)指令的功能是把源操作数中的每位二进制与目的操作数中的相应二进制进行逻辑加运算操作,操作结果存入目的操作数中。

(3)受影响的标志位:CF、OF为0,PF、SF和ZF根据运算定, AF无定义。

(4)利用OR指令与1或0相或,可对操作数置1操作,和保留原位不变。

举例:

将AL中第0位和第7位置1。

MOV AL,0

OR AL,81H

4.逻辑异或指令XOR

格式:XOR目的操作数,源操作数

操作形式:DOPD ← DOPDSOPD

描述:

(1)逻辑异或运算法则:11=0,10=1,01=1,00=0。

(2)指令的功能是把源操作数中的每位二进制与目的操作数中的相应二进制进行逻辑“异或”操作,操作结果存入目的操作数中

(3)受影响的标志位:CF、OF为0,PF、SF和ZF根据运算定, AF无定义。

(4)利用该指令与1和0相异或,分别可以操作数对应位变反和保持不变。

(5)对操作数自身异或运算可对寄存器和CF、OF置0。

举例:

(1)将AL中的0、7位变反

XOR AL,81H

(2)将AX清零

XOR AX,AX

5.逻辑测试指令TEST

格式:TEST 目的操作数,源操作数

操作形式:DOPD∧SOPD。

描述:

(1)该指令与指令AND的区别在于,两操作数相与后不保存结果。

(2)指令的功能是把源操作数的每位二进制与目的操作数中的相应二进制进行逻辑“与”操作,根据所得结果设置有关标志位,为随后的条件转移指令提供条件,由于不保存差值,所以不会改变指令中的操作数。

(3)受影响的标志位:CF、OF为0,PF、SF和ZF根据运算定, AF无定义。

举例:

(1)TEST AX,100B;B表示二进制

JNZ AA ;如果AX右数第三位为1,JNZ将跳转到AA处。

(2)测试寄存器是否为空

TEST AX,AX

JZ AA

如果AX为零,则ZF标志为1,JZ将跳转到AA处。

四、实验内容与步骤

1、实验内容

(1)用A命令编写程序片段,实现逻辑非,逻辑与,逻辑或,逻辑异或,逻辑测试运算;(2)得到实际的结果,用T或P命令查看结果正确性。

(3)实验例子,逻辑非:NOT 14H

逻辑与:32H AND 0FH

逻辑或:32H OR 0FH

逻辑异或:32H XOR 0FH

(4)进行逻辑测试运算中,注意状态和标志位的变化,并记录。

2、实验步骤

(1)预习逻辑运算中的基本指令知识,根据实验内容,整理思路;

(2)利用在DEBUG调试中的A命令输入对应程序片段;

(3)对写好的程序片段,利用DEBUG的T、P命令或G命令查看数据区,核对实验结果。

五、实验要求与提示

1、实验要求

(1)写出实现每个逻辑运算的例子答案;

(2)记录具体实现逻辑运算例子的实验步骤;

(3)回答思考问题;

(4)记录实验结果。

2、实验提示

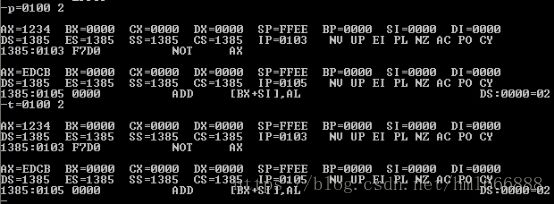

(1) 进入DEBUG调试环境,用A命令输入程序片段如图3-1所示。

(2)图3-1是实现的是逻辑非的运算验证。然后,用P或T命令查看寄存器AX内容的

实验结果分析

|

|

|

|

|

|

;***************************************************** ;写出下面程序各语句运行后寄存器和状态字的值 DATA SEGMENT STR DB 'HELLO WORLD!',13,10,'$' DATA ENDS

STACK SEGMENT STACK DB 20 DUP(?) STACK ENDS CODE SEGMENT ASSUME CS:CODE,DS:DATA,SS:STACK |

|

||||

START: |

寄存器AX |

寄存器BX |

寄存器CX |

寄存器CX |

状态标志 |

MOV AX,0FF03H |

FF03 |

0000 |

0000 |

0000 |

NV UP EI PL NZ NA PO NC |

MOV BX,0H |

FF03 |

0000 |

0000 |

0000 |

NV UP EI PL NZ NA PO NC |

MOV CX,5H |

FF03 |

0000 |

0005 |

0000 |

NV UP EI PL NZ NA PO NC |

MOV DX,0AH |

FF03 |

0000 |

0005 |

000A |

NV UP EI PL NZ NA PO NCT |

NOT AX |

00FC |

0000 |

0005 |

000A |

NV UP EI PL NZ NA PO NC |

AND AX,0FF0H |

00F0 |

0000 |

0005 |

000A |

NV UP EI PL NZ NA PE NC |

OR BX,AX |

00F0 |

00F0 |

0005 |

000A |

NV UP EI PL NZ NA PE NC |

OR DX,CX |

00F0 |

00F0 |

0005 |

000F |

NV UP EI PL NZ NA PE NC |

XOR AX,0033H |

00C3 |

00F0 |

0005 |

000F |

NV UP EI PL NZ NA PE NC |

XOR AX,AX |

0000 |

00F0 |

0005 |

000F |

NV UP EI PL ZR NA PE NC |

MOV AX,DATA |

141B |

00F0 |

0005 |

000F |

NV UP EI PL ZR NA PE NC |

MOV DS,AX |

141B |

00F0 |

0005 |

000F |

NV UP EI PL ZR NA PE NC |

LOOP1: |

|

|

|

|

|

SUB AX,1H |

141A |

00F0 |

0005 |

000F |

NV UP EI PL NZ NA PO NC |

TEST AX,AX |

141A |

00F0 |

0005 |

000F |

NV UP EI PL NZ NA PO NC |

JNZ LOOP1 |

141A |

00F0 |

0005 |

000F |

NV UP EI PL NZ NA PO NC |

MOV DX,OFFSET STR |

0000 |

00F0 |

0005 |

000F |

NV UP EI PL ZR NA PE NC |

MOV AH,09 |

0900 |

00F0 |

0005 |

0000 |

NV UP EI PL ZR NA PE NC |

INT 21H |

0900 |

00F0 |

0005 |

0000 |

NV UP EI PL ZR NA PE NC |

MOV AH,4CH |

4C24 |

00F0 |

0005 |

0000 |

NV UP EI PL ZR NA PE NC |

INT 21H |

4C24 |

00F0 |

0005 |

0000 |

NV UP DI ZR NA PE NC |

CODE ENDS |

|

|

|

|

|

END START |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|