直接扩频通信(下)仿真

今天给大侠带来直接扩频通信,由于篇幅较长,分三篇。今天带来下篇,也是最后一篇,仿真,话不多说,上货。

导读

本篇适用于有一定通信基础的大侠,本篇使用的理论不仅仅是扩频通信。为了便于学习,本章将会以实战的方式,对整个工程的仿真。并对一些关键的仿真结果进行说明。各位大侠可依据自己的需要进行阅读,参考学习。

第三篇内容摘要:本篇会介绍系统的仿真设计。

仿真

一、模块的建立及其仿真环境的生成

1.1、在计算机上,找一个没有中文字符的目录,新建以下几个文件,如图 6:

图6

上图为可以建立的文件,sim_wave.do 是仿真波形保存文件.tt.do。

其代码如下:

#建立 library 名为”work”vlib workvmap work work#编译当前目录(./)中的 top.v、mcu.v ….vlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./top.vvlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./mcu.vvlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./slaver.vvlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./coder.vvlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./add_noise.vvlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./decoder.vvlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./correct.vvlog -work work -L mtiAvm -L mtiOvm -L mtiUPF ./Correct_Decoder.v#仿真 work 中的 top 模型vsim -novopt work.top

以上是输入方式进行仿真,也可以直接使用图形化的方式进行仿真。但没有开始仿真,因为我们以下还要添加一条语句。但没有响应的文件。

tt.bat 的代码如下:

echopausevsim -do .\tt.dopause

tt.bat 文件为批处理文件,仅为打开 modelsim、运行 tt.do 文件使用。也可以不使用该文件(以下不会详细介绍)。

1.2、将对应的代码写到相应的文件中(sim_wave.do、tt.bat 文件可以不管)。

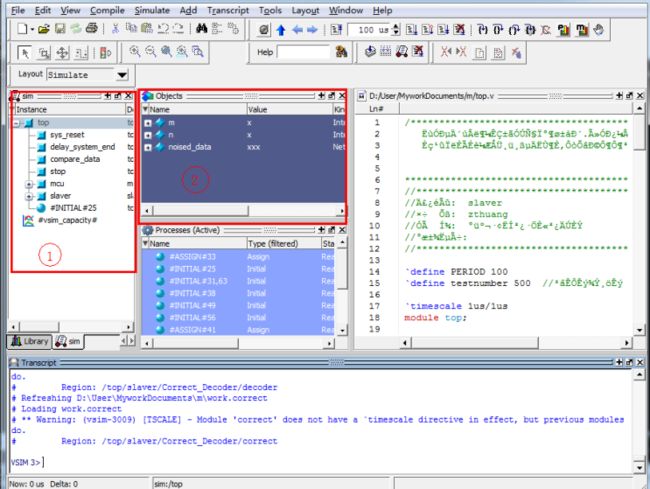

1.3、用 modelsim 的打开方式打开 top.v 文件(或者你先打开 modelsim,然后把目录修改成以上所述的目录也可)。运行的界面如图 7(modelsim6.5d):

图7

图中的乱码均为modelsim不兼容我所使用的notepad软件编写的中文字符,大侠均可不以理睬。

1.4、在 Transcript 中输入”do tt.do”,运行当前目录下的 tt.do 文件。

运行过程中,最后跳出如图 8 的窗口。如果有错误,会在 Transcript 中用红色字体说明(当然,这里都是英文)。

图8

在框图 1 中为整个仿真平台上的模型,可以点击模型+展开。框图 2 显示当前模型所含的项目。

1.5、添加波形,如图 9、10、11,对模块 coder 添加波形,并对波形进行分组。

图9

图10

图11

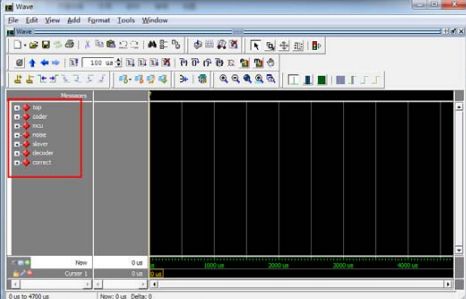

对所有仿真模型添加波形,并且分组,如图 12。

图12

图13

1.6、仿真开始

在 Transcript 中输入”run -all” 等待结果。以上将生成仿真环境的全过程。下面会将对各个模块进行说明。

二、模块仿真

2.1、模块 mcu 仿真

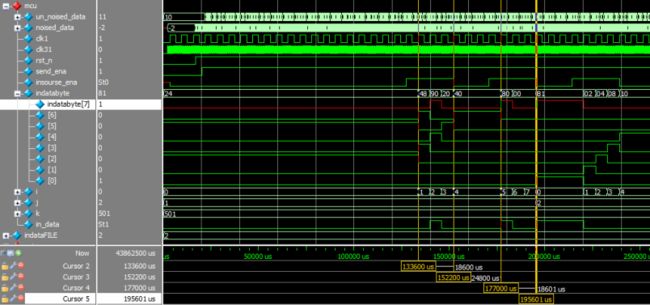

mcu 扮演一个信源产生模块,其波形如图 14。

图14

在 send_ena 使能的情况下,当 insourse_ena 为高时,数据从 indatabyte 第 7 位端口输出到 coder 模块,图中发送十六进制 24 的过程,仅在 insourse_ena 为高时发送。该模块还产生两个时钟,两个时钟分别是 31 倍的频率。clk1 和 clk31。

2.2、模块 coder 仿真

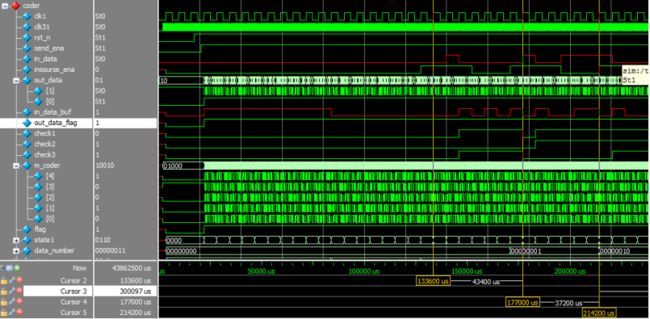

模块 coder 将对 mcu 传送的数据进行编码、扩频。仿真波形如图 15。

图15

图中的 in_data_buf 为发送码,当接收到 send_ena 后,先发送头和数据帧,然后才发送数据如图中从 133600us 开始发送数据”0010”(十六进制 2)后发送监督码的”101”,在 177000us 开始发送数据”0100”(十六进制 4)后发送监督码”110”。所有数据经过信道编码后,out_data 发送出去。

2.3、模块 noise 仿真

添加干扰,经 coder 发送的 2bit 数据扩展到 3bit 数据,并与噪声进行加性。

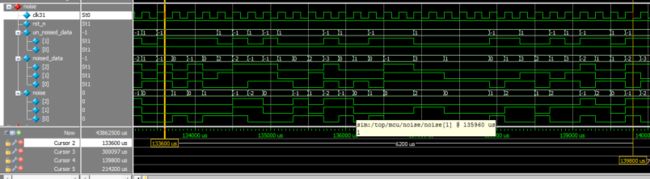

仿真波形如图 16。

图16

图中是对 1bit 数据进行扩频后,其中 un_noised_data 为输入数据(无噪声)、经过与 noise 数据相加,得到数据 noised_data。

这模块就是充当信道中的加性干扰源。

2.4、模块 decoder 仿真

解扩是本系统的设计重点。它包含同步头的同步和数据的接收等。

本设计采用一个循环伪随机作为解扩码。采用一个 31bit 的寄存器,初始化为级数为 5 的 m 序列,首尾循环。那么,在寄存器每一位上采数,都可以得到一个伪随机序列。分别得出 31 个 m 序列。而且靠近的寄存器位,采集的 m 序列只有一位的移位。因此,可以采用该方法,在发送端发送的数据,不管为何时发送,在 31bit个寄存器中的 1 个寄存器中与之对应。更通俗的说法,不管发送设备何时开始发送。都可以在 31bit 的寄存器中找到一个寄存器采到的 m 序列与之对应。

由于在 31 比特的寄存器同时采数是比较耗费 FPGA 内部资源,所以本设计采用寄存器的每 10 个 bit 位进行一一处理。如果前 10 个没能找到对应的 m 序列,则累加到后 10 个,以此类推,在 3 次的累加中,总能完全扫描完 31bit 位的寄存器。此时可以找到对应的比特位。

由于发送设备的数据头为 10 个”1”和 1 个”0”,而在 10 个”1”中的 1 是延伸的,没法直接得到相邻”1”的交界,而在得到合适的 m 序列位后,必须进行同步,同步的方法为采集最后一个”0”作为同步。

在接收完成数据头后,进行数据帧同步。数据帧是 4bit 数据”0000”和 3bit 监督位”000”。

接收完成数据帧之后才是数据的开始。由于数据比较大,累加基数这里是 100,阀值为 30,那么,当接收到 130,说明接收到一个”1”。

仿真结果如下:

图17

图17 为接收的整体工作状态,sum1~sum10 分别采集 10 个寄存器比特位,当有1 个接收超过 130,说明寄存器该为上的 m 序列可以接收到 1 个”1”,sum 是对数据帧和数据的解扩统计。

图18

图18 是一个完整数据解扩的过程,clk31 是采集时钟,数据为 in_data_buf,从输入到输出,延迟一段时间后传送到解扩模块。psumi 为解扩的值,通过累加得到sum(in_data[2]判断。为 1,则加;为 0,则减)。如果 sum 超过 130,说明发送数据为”1”,否则为”0”。(以上为数据”1”的例子)

通过解扩的数据,送到 correct 模块进行纠错。

2.5、模块 correct 仿真

模块 correct 为纠错模块。它将解扩后的数据进行分析,即对汉明码的反运算。该模块的仿真过程省略。

2.6、模块 Slaver 仿真

Slaver 是接收模块端,它将解扩、纠错后的数据进行存储。仿真过程省略。

2.7、模块 Top 仿真

Top 模块应该放第一块讲解,因为它是一个仿真平台,它的子模块包括 mcu 和slaver。它将两个模块的发送接收进行统计、并且进行计算、输出,并对模块参数设置。以下设置发送数据比特位为 500 的输出结果(图 19、图 20):

图19

图20

以上是整个设计的仿真过程。

本篇到此结束,直接扩频通信也到此结束,各位大侠,有缘再见!

END

后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。

大侠们,江湖偌大,继续闯荡,愿一切安好,有缘再见!

往期推荐

-

嵌入式中位宽的计算

-

源码系列:基于FPGA的中值滤波器设计(附源码)

-

基于 FPGA Vivado 的数字钟设计(附源工程)