ZCU104开发板:开发板组件描述

1. Zynq UltraScale+ XCUZU7EV MPSoC

ZCU104板上安装了Zynq UltraScale + XCZU7EV-2FFVC1156 MPSoC,它在同一设备中集成了功能强大的处理系统(PS)和可编程逻辑(PL)。Zynq UltraScale + MPSoC中的PS采用Arm®旗舰产品Cortex®-A53 64位四核处理器和Cortex-R5双核实时处理器。支持调整电压达到多种速度等级需要。

用户可以通过PMBus调节VCCINT电源,电压范围如表3-1所示,以支持多个Zynq UltraScale + MPSoC速度等级。

Zynq UltraScale + MPSoC PS模块有三个主要处理单元:

- Cortex-A53应用处理单元(APU)-Arm v8基于架构的64位四核多处理CPU。

- Cortex-R5实时处理单元(RPU)-Arm v7基于架构的32位双实时处理单元,带有专用的紧耦合存储器(TCM)。

- Mali-400图形处理单元(GPU) - 图形处理单元,具有像素和几何处理器以及64 KB L2缓存。

Zynq UltraScale + MPSoC PS具有四个支持这些协议的高速串行I / O(HSSIO)接口:

- 适用于PCIExpress®接口的集成模块 - 符合PCIe™基本要求2.1版本

- SATA 3.1规格兼容接口

- DisplayPort接口 - 实现DisplayPort仅源接口,视频分辨率高达4K x 2K-30(300 MHz像素速率)

- USB 3.0接口符合USB 3.0规范,实现5 Gb / s线速

- 串行GMII接口 - 支持1 Gb / s SGMII接口

PS和PL可以与多个接口和其他信号耦合,以有效地将用户创建的硬件加速器和PL逻辑中的其他功能集成到处理器可访问的位置。他们还可以访问PS中的内存资源。PS I / O外设(包括静态/闪存接口)共享多达78个MIO引脚的多路复用I / O(MIO)。Zynq UltraScale + MPSoC还可以将PL域中的I / O用于许多PS I / O外设。通过扩展的多路复用I / O接口(EMIO)完成的,并在上电或复位时启动

有关Zynq UltraScale + MPSoC器件的更多信息,请参见Zynq UltraScale + MPSoC数据手册:概述(DS891)[参考1]。有关Zynq UltraScale + MPSoC配置选项的更多信息,请参见Zynq UltraScale + MPSoC技术参考手册(UG1085)[参考2]。

2. Encryption Key Battery Backup Circuit

XCZU7EV MPSoC U1实现了比特流加密密钥技术。ZCU104板提供加密密钥备用电池电路,如图3-2所示

Seiko TS518FE可充电1.5V锂纽扣型电池B1焊接到电路板上,正极输出连接到XCZU7EV MPSoC U1 VCC_PSBATT引脚Y23。

当电路板电源关闭时,电池电源电流IBATT规格最大为150 nA。B1通过串联二极管从UTIL_1V8 1.8V电压轨充电,典型正向压降为0.38V,限流电阻为4.7ΩK。标称充电电压为1.42V。

3.I/O Voltage Rails

图3-2中列出了ZCU104板上的XCZU7EV MPSoC PL I / O组电压。

4. PS-side:DDR4内存

PS侧存储器连接到XCZU7EV DDRC bank 504硬核存储器控制器。PS端内存是一个2 GB,64位宽的DDR4内存系统,由4个256 Mb x 16 SDRAM,U2和99-101组成。

Zynq UltraScale + MPSoC数据手册中记录了ZCU104 XCZU7EV FFVC MPSoC PS DDR接口性能:直流和交流开关特性(DS925)[参考文献3]。DDR4 0.6V VTT终端电压由吸收源稳压器U178提供。表3-3列出了DDR4存储器与U1 XCZU7EV bank 504之间的连接。

ZCU104板DDR4 64位组件PS存储器接口符合UltraScale架构PCB设计用户指南(UG583)[参考文献4]中“DDR4的PCB指南”部分中记录的约束准则。ZCU104 DDR4 PS组件接口采用40Ω阻抗实现。UltraScale架构FPGA存储器接口解决方案产品指南(PG150)[参考文献5]中也提供了其他存储器接口详细信息。有关更多详细信息,请参阅Micron网站上的Micron MT40A256M16HA-083E数据表[参考11]。

5. PL-Side:DDR4 SODIMM插座

XCZU7EV PL侧组64,65和66连接到DDR4 SODIMM插座J1。ZCU104套件出厂时未安装DDR4 SODIMM。

推荐的SODIMM是:

Zynq UltraScale + MPSoC数据手册中记录了ZCU104 XCZU7EV FFVC MPSoC PL DDR接口性能:直流和交流开关特性(DS925)[参考文献3]。DDR4 0.6V VTT终端电压由吸收源稳压器U177提供。表3-4列出了DDR4 SODIMM插座J1连接。

ZCU104板PL DDR4 SODIMM接口符合UltraScale架构PCB设计用户指南(UG583)[参考文献4]中“DDR4的PCB指南”部分中记录的约束准则。PL DDR4 SODIMM接口是40Ω阻抗实现。UltraScale架构FPGA存储器接口解决方案产品指南(PG150)[参考文献5]中也提供了其他存储器接口详细信息。

6.PSMIO

表3-5提供了在ZCU104板上实现的PS MIO外设映射。有关PS MIO外设映射的更多信息,请参见Zynq UltraScale + MPSoC技术参考手册(UG1085)[参考2]。

7. Quad SPI Flash Memory (MIO 0–5)

Micron MT25QU512ABB8ESF串行NOR闪存Quad SPI闪存可以保存MPSoC系统的启动映像。该接口用于支持Zynq UltraScale + MPSoC技术参考手册(UG1085)[参考文献2]中定义的QSPI32引导模式。

Quad SPI闪存(U119)位于电路板的底部,提供512 Mb的非易失性存储,可用于配置和数据存储。

Zynq UltraScale + MPSoC技术参考手册(UG1085)[参考2]的配置和Quad SPI闪存部分提供了有关使用存储器的详细信息。有关Quad SPI的更多详细信息,请参阅Micron网站上的Micron MT25QU512ABB8ESF-0SIT数据表[参考资料11]。

USB0(MIO 52-63)

PS端的USB接口作为主机或设备控制器提供多种角色。MPSoC GTR接口支持USB 3.0接口,而SMSC USB3320C控制器的USB 2.0功能在通用USB 3.0 USB AB型接口(J96)上共享。

8. USB 3.0收发器和USB 2.0 ULPI PHY

ZCU104板在U116上使用标准微系统公司的USB3320 USB 2.0 ULPI收发器,以支持与主机的USB连接(见图3-3)。ZCU104评估套件中提供USB电缆(标准A连接器连接到主机,micro-B连接器连接到ZCU104板连接器J96)。USB3320是一款支持UTMI +低引脚接口(ULPI)接口标准的高速USB 2.0 PHY。ULPI标准定义了USB控制器IP和PHY设备之间的接口,PHY设备驱动物理USB总线。使用ULPI标准可减少USB控制器IP与PHY设备之间的接口引脚数

USB3320采用24 MHz晶振。有关时钟模式的详细信息,请参见标准微系统公司(SMSC)USB3320数据手册[参考资料12]。USB3320 PHY的接口通过XCZU7EV MPSoC PS中的IP实现。ZCU104 USB3320 PHY支持仅主机模式。表3-7列出了U116的USB 2.0 PHY与XCZU7EV MPSoC之间的连接。

USB3320 ULPI U116收发器电路(见图3-4)有一个Micrel MIC2544高端可编程限流开关(U121)。该开关在引脚2上有一个漏极开路输出故障标志,如果检测到过流或热关断条件,它会打开LED DS51。DS51位于按钮SW4附近的U116电路区域(图2-1,标注20)。

9. SD1(MIO 45-51)

提供SD卡连接器的PS侧接口,用于引导和文件系统存储。此接口用于SD引导模式,并支持启动后的SD3.0访问。

SD卡接口

ZCU104板包含一个安全的数字输入/输出(SDIO)接口,可以访问通用的非易失性SDIO存储卡和外设。有关SD I/O卡规范的更多信息,请参见SanDisk Corporation [Ref 13]或SD Association [Ref 14]网站。ZCU104 SD卡接口支持Zynq UltraScale + MPSoC技术参考手册(UG1085)[参考文献2]中记录的SD1_LS配置引导模式。

SDIO信号连接到XCZU7EV MPSoC PS bank 501,其VCCMIO设置为1.8V。六个MIOxx_SDIO_ *网络中的每一个都在源极上有一个30Ω串联电阻。MAX13035E电压电平转换器(U145)位于XCZU7EV MPSoC和SD卡连接器(J100)之间。

表3-8列出了与XCZU7EV MPSoC的SD卡接口连接

表3-8:通过U145与SD插槽的XCZU7EV MIO连接

10.可编程逻辑JTAG编程选项

ZCU104板JTAG链如图3-6所示

当FPGA夹层卡(FMC)连接到J5时,它会通过电子控制的单刀单掷(SPST)开关U27自动添加到JTAG链中。SPST开关通常处于关闭状态,并在连接FMC时转换为打开状态。交换机U27根据FMC_LPC_PRSNT_M2C_B信号确定将附加的FMC添加到JTAG链。附加的FMC卡必须使用器件或旁路跳线实现TDI到TDO连接,以确保JTAG链连接到U1 XCZU7EV MPSoC

11.PS M.2 SATA连接器

[图2-1,标注32]

M.2 SATA接口用于使用PS侧bank 505 GTR收发器进行SATA SSD访问。图3-7显示了M.2连接器U170

带有按键M的插座2 SATA适配器引脚排列如表3-9所示。SATA-A数据连接用于TX,SATA-B用于RX。M.2连接器U170是插座2上使用的2242型(有源元件部分22 mm宽,总长度42 mm)

12.时钟生成

ZCU104板提供IDT8T49N287FemtoClock®NG八通道通用频率转换器(U182)时钟发生器。表3-12列出了每个时钟的频率

表3-13列出了每个时钟的连接。

IDT8T49N287 FemtoClock NG Octal Universal Frequency Translator

- •时钟发生器:IDT8T49N287A-501NLGI

- 抖动:典型值<0.3 ps RMS

IDT8T49N287A-501NLGI U182(位于电路板底部)是一次性可编程时钟源,可通过I2C总线进行频率调整。时钟电路如图3-8所示。

有关更多详细信息,请参见IDT8T49N287A数据表[参考文献21]。

X-Ref目标 - 图3-8图

有关更多详细信息,请参见IDT8T49N287A数据表[参考文献21]。

13 GEM3 Ethernet (MIO 64-77)

PS端千兆以太网MAC(GEM)实现10/100/1000 Mb / s以太网接口(见图3-9),该接口连接到路由到RJ45以太网连接器的TI DP83867IRPAP以太网RGMII PHY U98。RGMII以太网PHY绑定到PHY地址5'b01100(0x0C),自动协商设置为启用。DP83867 RGMII PHY数据手册[参考文献16]中介绍了与器件的通信。

10/100/1000 MHz三速度以太网PHY

[图2-1,标注9]

ZCU104板使用TIDP83867IRPAP以太网RGMII PHY [Ref 16](U98)进行10 Mb / s,100 Mb / s或1000 Mb / s的以太网通信。该板仅支持RGMII模式。与用户提供的以太网电缆的PHY连接是通过Bel Fuse L829-1J1T-43 RJ-45连接器(P12),内置磁性元件和LED指示灯。表3-14列出了XCZU7EV MPSoC U1与DP83867IRPAP PHY器件U98(电路板底部)的连接。

Ethernet PHY Reset

DP83867IRPAP PHY复位门U169如图3-10所示。DP83867IRPAP可由MAX16025 U22 MPSoC PS侧POR复位器件(PS_POR_B)或I2C0连接的U97 TCA6416A I / O扩展器引脚10端口P06(GEM3_EXP_RESET_B)复位。

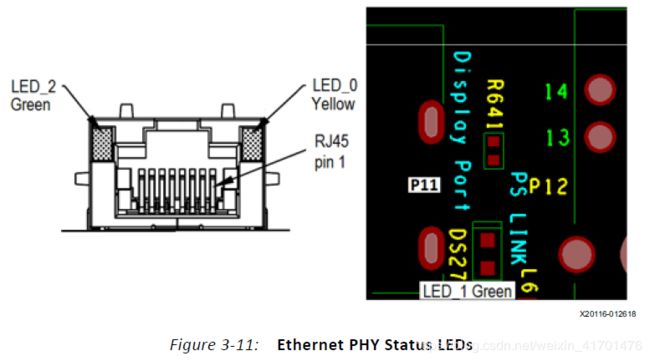

以太网PHY LED接口

[图2-1,标注9] DP83867IRPAP PHY U98 LED接口(LED_0,LED_2)使用嵌入在P12 RJ45连接器挡板中的两个LED。LED功能描述如表3-15所示。

通过PHY的管理数据接口MDIO / MDC可以通过LEDCR1寄存器写入来重新使用LED功能。LED_2分配给活动指示器(ACT),LED_0指示建立链路。有关更多以太网PHY详细信息,请参见TI DS83867数据手册[参考资料16]。

DP83867IRPAP PHY LED指示灯如图3-11所示

- LED_0是RJ-45 P12挡板右侧黄色LED,链路建立指示灯。

- LED_2是RJ-45 P12边框左侧绿色LED,TX / RX活动指示灯。

- LED_1是绿色DS27 LED,安装在显示端口连接器P11和以太网RJ-45连接器P12之间的ZCU104板顶部,表示建立了1000BASE-T链路

13. I2C1(MIO 16-17)

[图2-1,标注12和13] I2C1接口通过I2C开关TCA9548A U34提供对I2C外设的访问。TCA6416A端口扩展器U97也连接到I2C1总线。I2C1 PS侧bank 500连接与PL侧bank 87共享。图3-12显示了表3-16和表3-17中所示的I2C1总线连接的高级视图。TCA9548A U34设置为0x74,TCA6416A设置为0x20。

表3-16和表3-17分别显示了U34和U97(位于电路板底部)的连接。