【ZYNQ-7000开发之三】ZYNQ平台的HDMI驱动测试

高清显示是ZYNQ的一大特色,显示有利于观察数字图像处理的输出和人际交互。在本篇文章中,将在Xilinx ZYNQ平台上对HDMI进行测试,参考ADI的官方Demo。

官方Demo链接:https://wiki.analog.com/resources/fpga/xilinx/kc705/adv7511

这个Demo涉及到vivado自动化工程TCL脚本文件的使用,PL和PS的联合处理,AXI接口的使用。

本文所使用的开发板是Miz702(兼容zedboard)

PC 开发环境版本:vivado 2015.2 SDk 2015.2

一、下载库和脚本文件

1.1HDL脚本和库下载,用来自动构建PL端的硬件架构链接:

https://git.oschina.net/fengshuaigit/hdl (由于GITHUB有时打不开,我把官方的Demo clone到了oschina,速度较快)

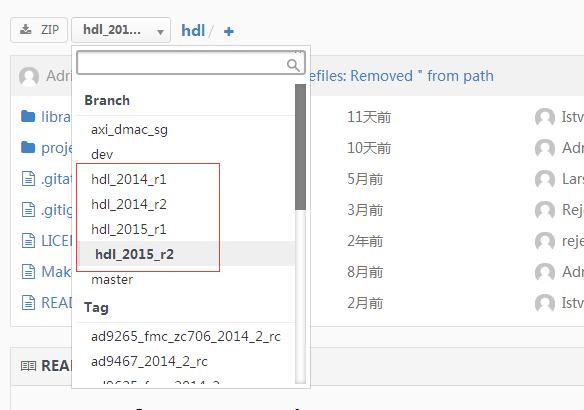

打开链接之后,在红框里选择和自己vivado最接近的版本,点击ZIP下载

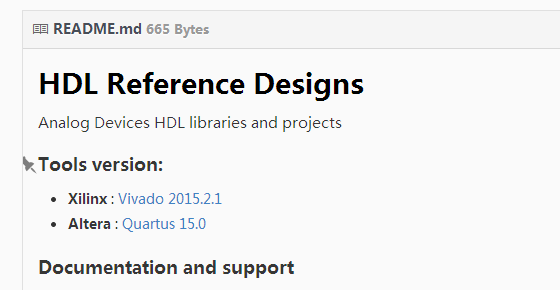

本人的版本是vivado2015.2,所以选择hdl_2015_r2,选择后,下面的README可以看到具体的版本信息,可见它的版本是2015.2.1(和本人的版本不一样,等会要解决这个问题)

1.2没有操作系统的软件库文件的下载,用来在PS端运行的库

下载链接:https://git.oschina.net/fengshuaigit/no-OS

下载方法如上

1.3下载完成,解压,放在没有中文目录的路径下

二、编译HDL库,我们要把构建HDMI需要使用的库预先编译,然后才能使用TCL构建整个项目

使用到的库如下:

- hdl/library/axi_clkgen

- hdl/library/axi_hdmi_tx

- hdl/library/axi_i2s_adi

- hdl/library/axi_spdif_tx

- hdl/library/util_i2c_mixer

下面开始编译:

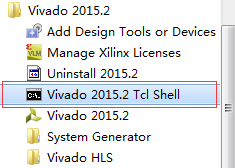

2.1打开vivado,调出Tcl Console

2.2输入cd F:/HDMI/hdl/library/axi_clkgen/ (按自己的路径)

回车:

2.3输入source ./axi_clkgen_ip.tcl 回车

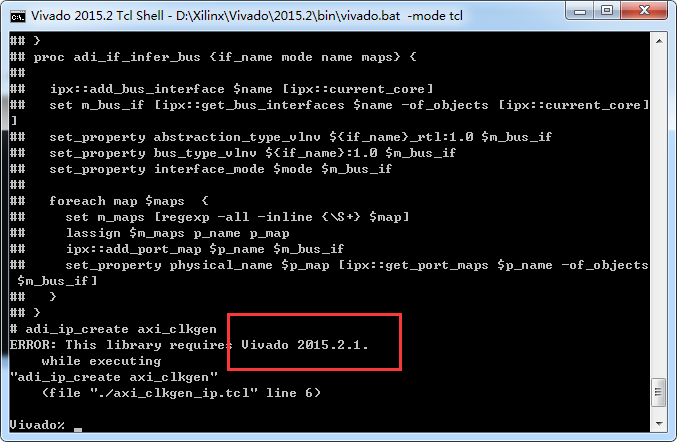

注意此时本人出现了版本不兼容的问题,如下:

解决办法如下:

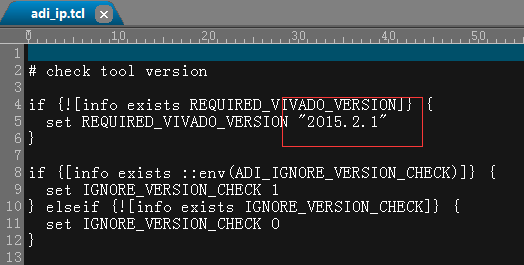

a.把路径F:\HDMI\hdl\library\scripts 下的adi_ip.tcl里的版本修改为2015.2

b.把路径F:\HDMI\hdl\projects\scripts下的adi_project.tcl里的版本控制信息,也修改为2015.2

然后先退出Tcl shell

再依次输入

cd F:/HDMI/hdl/library/axi_clkgen/

source ./axi_clkgen_ip.tcl

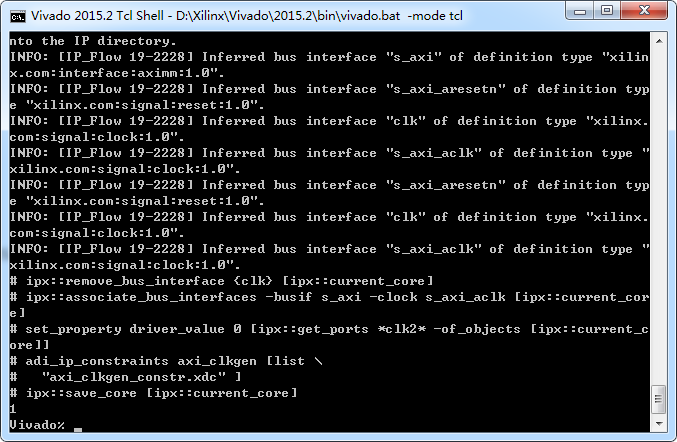

2.4成功后信息如下所示:

2.5然后依次剩下的编译

- hdl/library/axi_hdmi_tx

- hdl/library/axi_i2s_adi

- hdl/library/axi_spdif_tx

- hdl/library/util_i2c_mixer

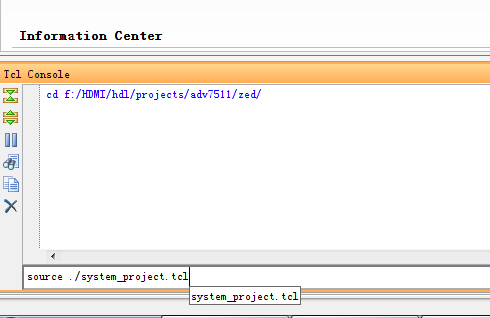

三、构建整个项目,为了方便观察项目进度,关闭Tcl shell,打开vivado gui版,在tcl concle 里输入:

cd F:\HDMI\hdl\projects\adv7511\zed

source ./system_project.tcl

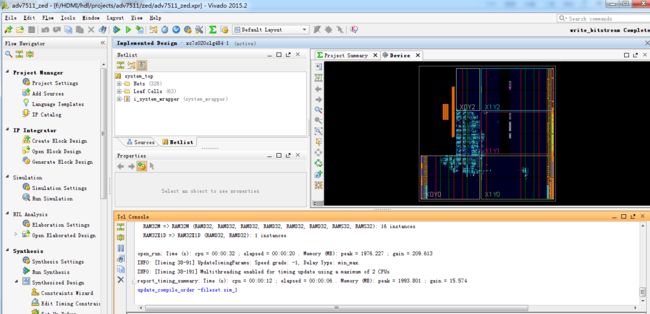

图示:

然后整个工程开始自动构建,我们可以看到整个过程,这个自动化的构建项目确实很方便,值得学习啊。

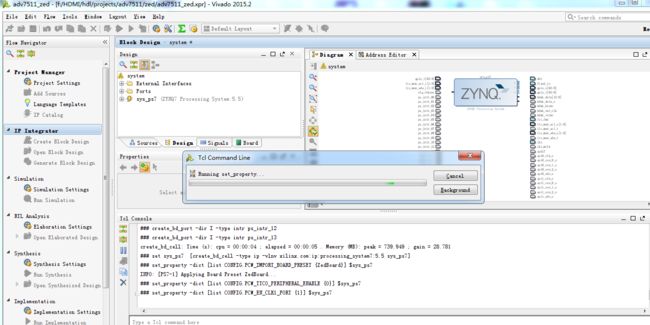

根据电脑配置的不同,持续时间大约20-40分钟,构建完成的结果如图所示:

打开Block Design,可以看到自动构建的模块,包含ZYNQ PS,AXI_STREAM,HDMI Core 等等

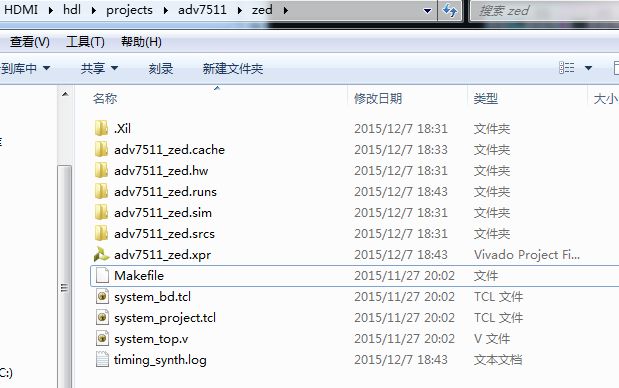

在F:\HDMI\hdl\projects\adv7511\zed的下面可以看到自动构建的工程目录

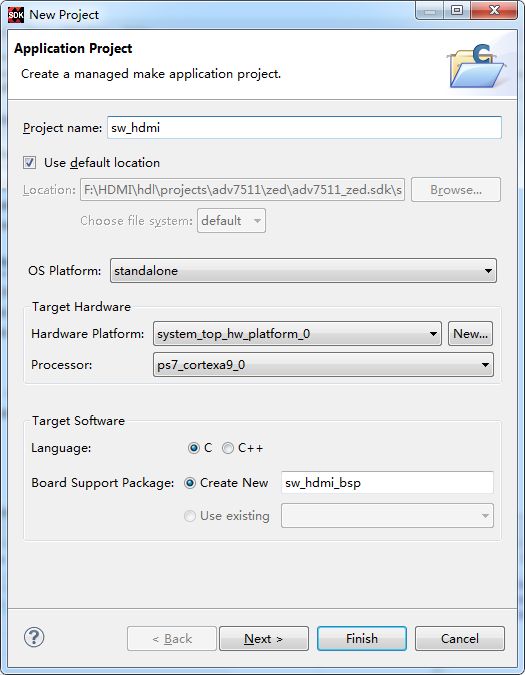

四、打开SDK,选择 Launch SDK

4.1新建hello world 工程

点击next,选择hello world

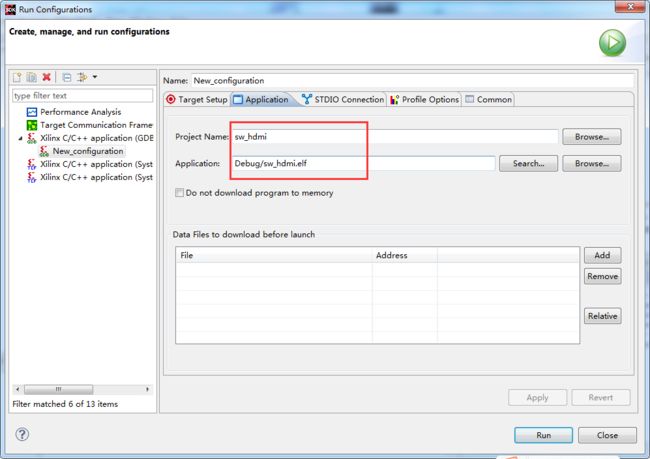

4.2 打开F:\HDMI\hdl\projects\adv7511\zed\adv7511_zed.sdk\sw_hdmi\src

把helloworld.c文件删除

打开F:\HDMI\no-OS\adv7511\zed

把里面的文件copy到F:\HDMI\hdl\projects\adv7511\zed\adv7511_zed.sdk\sw_hdmi\src

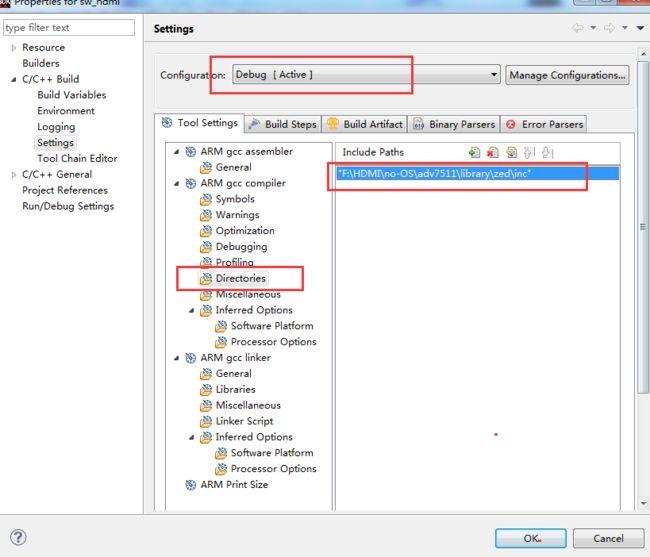

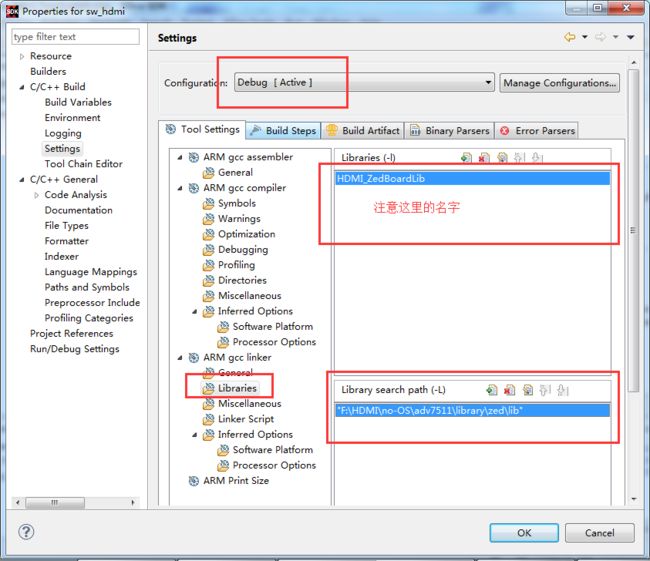

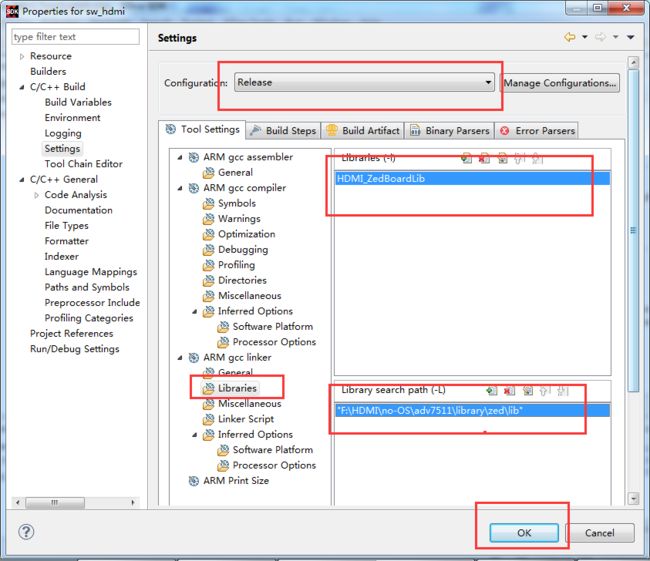

4.3设置链接库

在工程名字(sw_hdmi)上右击,选择properties

a.

b.

c.

d.

e.

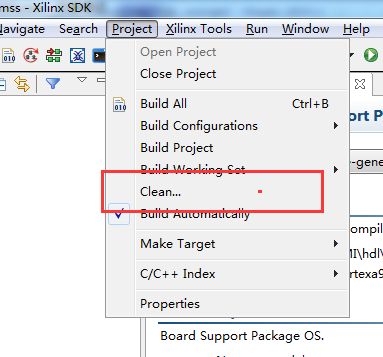

选择Project -> clean 编译整个工程

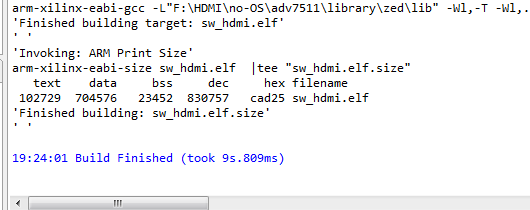

编译成功后会生成如图所示的log:

五、终于到最后一步了,上板测试!

连接好仿真器和串口后

首先program FPGA

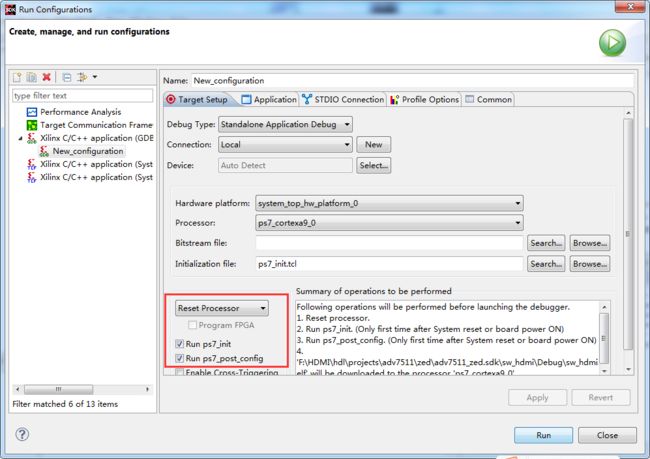

RUN Configure

点击run

(⊙o⊙)结果如下

串口打印信息如下

********************************************************************

ADI HDMI Trasmitter Application Ver R1.1.1

HDMI-TX: ADV7511 Rev 0x12

Created: Dec 7 2015 At 19:23:57

********************************************************************

To change the video resolution press:

'0' - 640x480; '1' - 800x600; '2' - 1024x768; '3' - 1280x720

'4' - 1360x768; '5' - 1600x900; '6' - 1920x1080.

Mute audio and video.

APP: Driver Enabled

HPD changed to HI

MSEN changed to HI

APP: Changed system mode to Transmitter

Un-mute audio and video.

HPD changed to LOW

MSEN changed to LOW

HPD changed to HI

MSEN changed to HI

A new EDID segment was read.

DVI device.

------------------------- EDID BLOCK 0 -------------------------

Edid Version 1.3

Mon Timing:

Pixel clock = 148.50 MHz

H Active = 1920

V Active = 1080

Progressive

No stereo

Separate sync = 3

+ve VSync

ADI HDMI Trasmitter Application Ver R1.1.1

HDMI-TX: ADV7511 Rev 0x12

Created: Dec 7 2015 At 19:23:57

********************************************************************

To change the video resolution press:

'0' - 640x480; '1' - 800x600; '2' - 1024x768; '3' - 1280x720

'4' - 1360x768; '5' - 1600x900; '6' - 1920x1080.

Mute audio and video.

APP: Driver Enabled

HPD changed to HI

MSEN changed to HI

APP: Changed system mode to Transmitter

Un-mute audio and video.

HPD changed to LOW

MSEN changed to LOW

HPD changed to HI

MSEN changed to HI

A new EDID segment was read.

DVI device.

------------------------- EDID BLOCK 0 -------------------------

Edid Version 1.3

Mon Timing:

Pixel clock = 148.50 MHz

H Active = 1920

V Active = 1080

Progressive

No stereo

Separate sync = 3

+ve VSync

+ve HSync

Mon Timing:

Pixel clock = 119.0 MHz

H Active = 1680

V Active = 1050

Progressive

No stereo

Separate sync = 3

-ve Vsync

-ve HSync

Mon Name: ËÉÈË

Mon Name: ´´Ï뼯ÍÅ

Edid extensions blocks: 0

########################### EDID END ###########################

Pixel clock = 119.0 MHz

H Active = 1680

V Active = 1050

Progressive

No stereo

Separate sync = 3

-ve Vsync

-ve HSync

Mon Name: ËÉÈË

Mon Name: ´´Ï뼯ÍÅ

Edid extensions blocks: 0

########################### EDID END ###########################

六、总结

这个Demo里用到的tcl很方便,要学习下使用,还有就是想用好ZYNQ 那么要很了解AXI,不然很难把FPGA和ARM协同好。

以后会利用HDMI传输视频图像

更多关于zynq开发相关的文章和问题请点击:

http://www.osrc.cn/forum.php?mod=forumdisplay&fid=292

http://blog.csdn.net/rzjmpb