XILINX 的 MIG IP(非AXI4)接口时序以及控制

一、 MIG 控制器概述

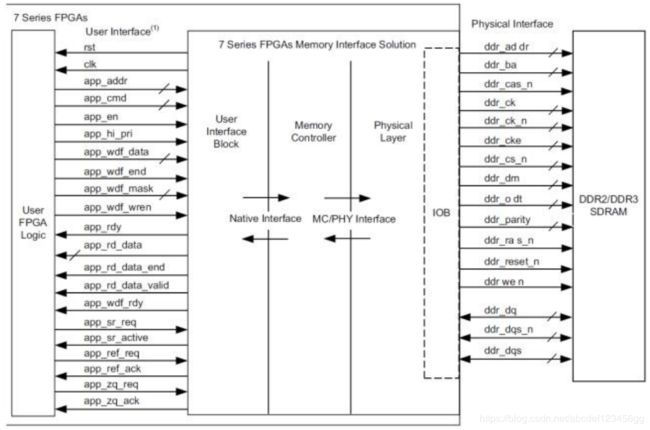

7 系列 FPGA 存储器接口解决方案核心如图所示。

二、 用户 FPGA 逻辑接口

上图所示的用户 FPGA 逻辑模块可以连接到外部 DDR2 或 DDR3 SDRAM 的任何 FPGA 设计。用户 FPGA 逻辑通过用户界面连接到内存控制器。IPCORE 提供了一个用户 FPGA 逻辑示例。

AXI4 从接口块

AXI4 从站接口将 AXI4 事务映射到 UI,以向内存控制器提供行业标准总线协议接口。

用户界面块和用户界面

UI 块向用户提供 FPGA 逻辑块。它通过呈现平面地址空间和缓冲读写数据来提供对本机接口的简单替代。

内存控制器和本机接口

内存控制器(MC)的前端显示 UI 块的本机接口。本地接口允许用户设计提交存储器读写请求,并提供将数据从用户设计移动到外部存储器件的机制,反之亦然。内存控制器的后端连接到物理接口,并处理该模块的所有接口要求。 内存控制器还提供了重新排序选项,重新排序接收的请求以优化数据吞吐量和延迟。

PHY 和物理接口 PHY 的前端连接到存储控制器。PHY 的后端连接到外部存储设备。 PHY 处理所有存储器件信号顺序和定时。IDELAYCTRL 任何使用 IDELAYs 的 bank 都需 IDELAYCTRL。 IDELAY 与数据组(DQ)相关联。 任何使用这些信号的 BANK/时钟区域都需 IDELAYCTRL.MIG 工具实例化一个IDELAYCTRL,然后使用 IODELAY_GROUP 属性(参见 iodelay_ctrl.v 模块)。基于此属性,Vivado Design Suite 可根据需要在设计中正确复制 IDELAYCTRL IDELAYCTRL 参考频率由 MIG 工具设置为 200 MHz,300 MHz 或 400 MHz,具体取决于 FPGA 的存储器接口频率和速度等级。 根据设置的 IODELAY_GROUP 属性,Vivado Design Suite 会复制 IDELAY 块所在区域的 IDELAYCTRL。

当用户自己创建一个多控制器设计时,每个 MIG 输出都具有用原语实例化的组件。 这违反了IDELAYCTRLs 的规则和 IODELAY_GRP 属性的使用。IDELAYCTRL 需要只有一个组件的实例化才能正确设置属性,并允许工具根据需要进行复制。

用户接口

UI 连接到 FPGA 用户设计,以允许访问外部存储设备。

| app_addr | i | 此输入表示当前正在提交给用户界面的请求的地址。 UI 聚合外部 SDRAM 的所有地址字段,并向您显示一个平面地址空间。 |

| app_cmd | i | read:001 write:000 |

| app_en | i | 此信号在输入请求中使用,用户必须赋值于 app_addr ,app_cmd 和 app_hi_pri,然后断言 app_en 将该请求提交给 UI。这将通过断言 app_rdy 启动 UI 确认的握手。 |

| app_hi_pri | i | 该输入表示当前请求是高优先级。 |

| app_wdf_data | i | 该总线提供当前正在写入外部存储器的数据。 |

| app_wdf_end | i | 该输入表示当前周期中 app_wdf_data 总线上的数据是当前请求的数据。 |

| app_wdf_wren | i | 该输入表示 app_wdf_data 总线上的数据有效。 |

| app_rd_data | o | 该输出包含从外部存储器读取的数据。 |

| app_rd_data_end | o | 此输出表示当前周期中 app_rd_data 总线上的数据为当前请求的最后数据。 |

| app_rd_data_valid | o | 该输出表示 app_rd_data 总线上的数据有效。 |

| app_rdy | o | 此输出向用户显示当前正在提交给 UI 的请求是否被接受。如果在 app_en 被断言之后,UI 不会声明此信号,则必须重试当前的请求。如果以下情况,则不会声明 app_rdy 输出: 1)PHY /内存初始化尚未完成 2)所有的 bank 机器都被占用(可以看作命令缓冲区已满) - 请求读取,读取缓冲区已满 - 请求写入,并且没有写缓冲区指针可用 3)正在插入定期读取 |

| app_wdf_rdy | o | 该输出表示写入数据 FIFO 准备好接收数据。 接受写入数据 当 app_wdf_rdy 和 app_wdf_wren 都被断言时。 |

| app_wdf_mask | i | 该总线指示 app_wdf_data 的哪些位被写入外部存储器,哪些位保持在当前状态。 |

| ui_clk | o | 这是 UI 的输出时钟。 它必须是出口到外部 SDRAM 的时钟频率的一半或四分之一,这取决于GUI 中选择的 2:1 或 4:1 模式。 |

| ui_clk_sync_rst | o | 这是从与 ui_clk 同步的 UI 重置。 |

| init_calib_complete | o | 当校准完成时,PHY 会断言 init_calib_complete。 在向内存控制器发送命令之前,应用程序无需等待 init_calib_complete。 |

三、 MIG内存控制器用户逻辑时序

3.1 控制命令时序

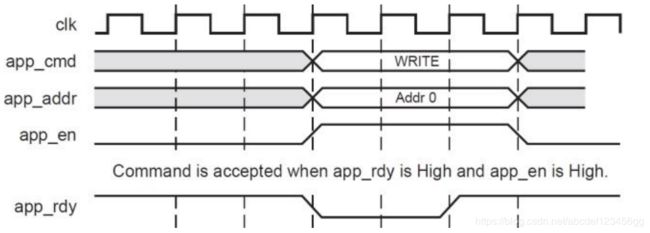

app_rdy:这个信号由DDR3输出,告诉用户在app_rdy拉高的时候拉高app_en。地址app_addr才是有效的。

当用户逻辑 app_en 信号被断言并且 app_rdy 信号从 UI 被断言时,命令被 UI 接受并写入 FIFO。当 app_rdy 被取消置位时,UI 会忽略该命令。用户逻辑需要将 app_en 保持为高电平以及有效的命令和地址值,直到 app_rdy 被断言,如图所示。

3.2 写操作及时序

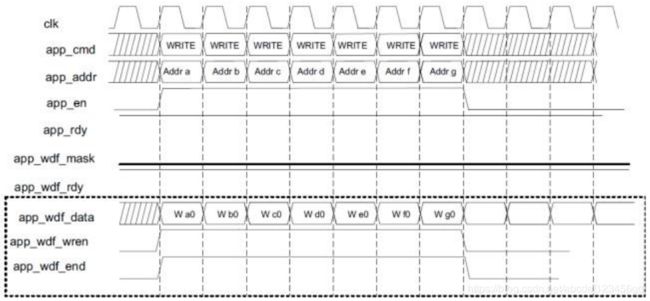

app_cmd :操作命令,确定是读还是写。读: app_cmd = 3'b001; 写:app_cmd = 3'b000;

app_addr:操作地址(往哪写,从哪读)

app_en :操作地址app_addr的使能,只有它拉高的时候,对应的app_addr才是有效的

app_wdf_data:写入数据的接口(往DDR3里面写什么)

app_wdf_wren:写入的数据接口app_wdf_data的使能,只有它拉高的时候。对应的app_wdf_data才是有效的

app_wdf_end:这里不需要管他。只需要使app_wdf_end = app_wdf_wren。

app_rdy:这个信号由DDR3输出,告诉用户在app_rdy拉高的时候拉高app_en。地址app_addr才是有效的。

app_wdf_rdy:这个信号由DDR3输出,告诉用户在app_wdf_rdy拉高的时候拉高app_wdf_wren,写入的数据app_wdf_data才是有效的。

所以写入数据的时候你只需要处理好这8个信号就可以

app_cmd

app_addr

app_en

app_wdf_data

app_wdf_wren

app_wdf_end

app_rdy

app_wdf_data

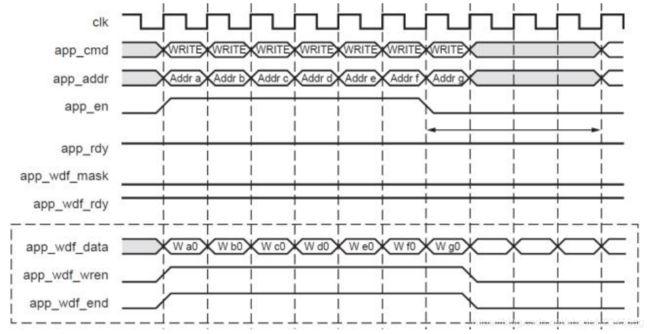

在app_rdy和app_wdf_rdy都拉高的时候,把app_en拉高、app_wdf_wren拉高、给出相应的地址、写入相应的数据 就可以把相应的数据写入到DDR3中相应的地址。但是,需要注意的是,在app_rdy 或者app_wdf_rdy没有拉高的时候,需要把相应的数据和地址保持不变。app_wdf_mask 信号可用于屏蔽写入外部存储器的字节。

写入数据和相关联的写入命令之间的单次写入的最大延迟是两个时钟周期。当发出背靠背写入命令时,写入数据和相关的背靠背写命令之间没有最大延迟。

必须使用 app_wdf_end 信号来指示存储器写入突发的结束。对于 8 位的内存突发类型,应该在第二个写入数据字上断言 app_wdf_end 信号。应用程序接口数据到 DRAM 输出数据的映射可以是以一个例子解释。

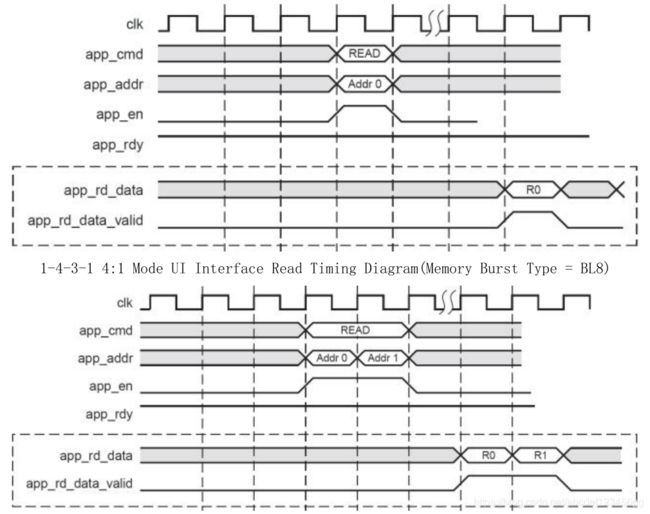

3.3 读操作及时序

读数据的时候只需要操作以下三个信号(这里的三个信号和上面是一样的)

app_cmd

app_addr

app_en读取的数据由 UI 以请求的顺序返回,并且在 app_rd_data_valid 被断言时有效。app_rd_data_end 信号表示每个读命令脉冲串的结束,在用户逻辑中不需要。

在读的时候,只需要在app_rdy拉高的时候给出地址app_addr和使能app_en即可。然后就等着接数就可以,给几个周期的使能就出几个周期的数据。

返回的读取数据总是与地址/控制总线上的请求顺序相同。

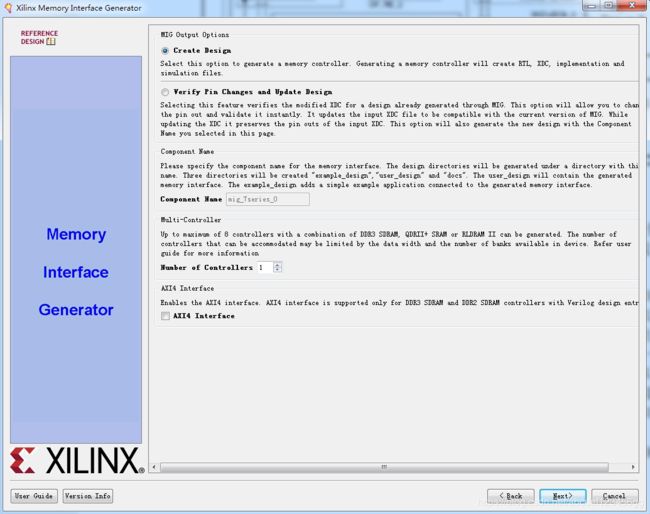

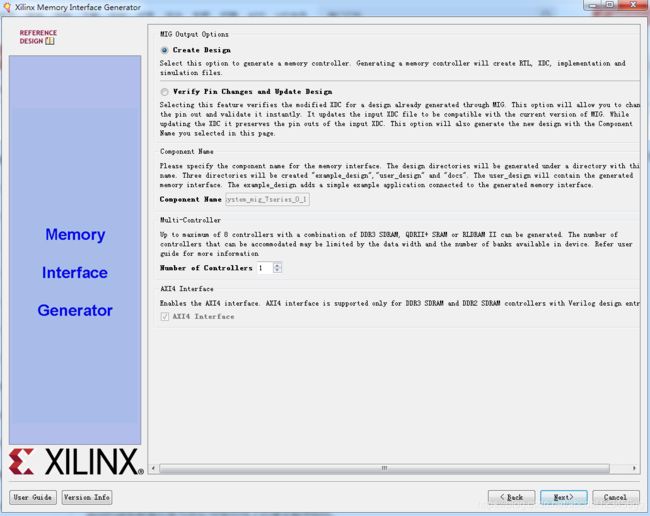

特别

vivado 2016.2 版本之前的软件可以修改接口类型。

vivado 2016.2 版本之后的软件生来就是 AXI4 接口标准,不能修改,所以下一期来介绍axi4接口的MIG控制器设计方案。