在ASIC设计中,有两种HDL construct来描述delay信息:

1)Distributed delays:通过specify event经过gates和nets的time,来描述delay;

对于net和gate都有三种delay信息: 1)rise delay 2)fall delay 3)transition to high-impedance value

只有一种delay时,所有change都使用这种delay,两个delay值时,才分为rise/fall

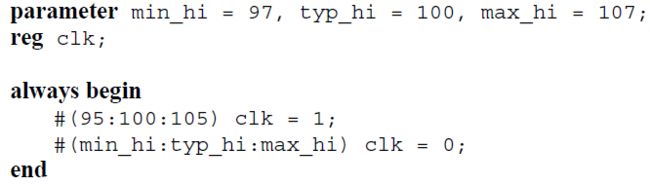

每一种delay信息又分为:min:typical:max三种。

gate和net的model例子:

但是trireg类型的变量一般建模cap的信号:第三个delay信息表示他storage的信号值不再保证的时间;

2)Module path delays:通过描述event从source(input/inout port)到destination(output/inout port)的time,来描述delay;

使用specify......endspecify来进行描述。

在specify block中一般有三种信息:

1)various paths across the module;

2)Assign delays to those paths;

3)Perform timing check;

path的declaration包括三类:

1)simple path declaration;

2)edge sensitive path declaration; 加 posedge/negedge

表示FF的有效沿是posedge,从in到out是一个positive的polarity,rise delay是10, fall delay是8。

3)state dependent path declaration; 加if/ifnone

4)Edge-sensitive state-dependent paths

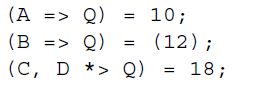

“ *>”表示 full conection, “ =>”表示parallel conection

对于会改变polarity的 path,可以通过+/-来进行描述,否则按unknown polarity分析(rise edge可能引起fall edge/rise/edge/no transition)。

"+"表示positive polarity, rise 可能引起rise edge或no transition

"-"表示positive polarity, rise 可能引起fall edge或no transition

Specifying transiiton delay on module path

按rise---fall---to-z的三种来区分,每一种delay信息可以再细分min/typ/max

前三者用","区分,后三者用":"区分

在delay path中,有一些是到同一个output的,这是选择最近有效的一路来计算,如果还是有多条

同时有效,选择delay较小的那一条path。

当Y从0变为1时,如果A transition more recently,那么选择6的delay,否则选择5的delay;

如果A和B都有效,那么选择5的delay;

对于module path delay和distributed delay都存在的情况,选择两者之间大的那一个值。

对于path的distination必须是的单一driver的,所以一些wire类型的信号,必须变为gate输出的signal

TIming Check,在给定的timing limit内,保证critical event occur;

可以分为两大类:

1)检查stability time window----------$setup, $hold, $setuphold, $recovery, $removal, $recrem

2)检查two event之间的time----------$skew, $width, $period, $nochange

注意这些timing check并不是task,specify内也不允许有task;

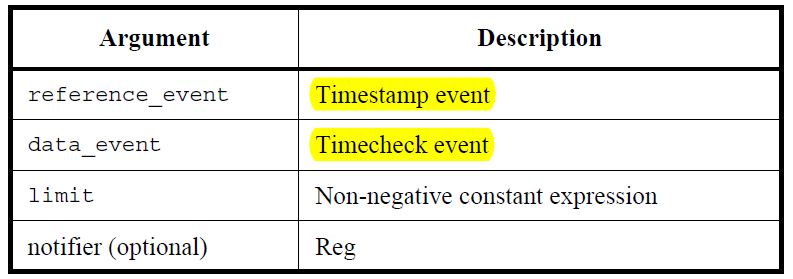

所有的这些timing check都有两个基准时间点:reference event和data event;

两个时间评估点:timestamp event和timecheck event;

不报violation,必须保证data event在正确的time window下发生

$setup check: $setup(data_event, reference_event, time_check_limit,notifier)

保证timestamp的时间在time window之内,否则会报violation

![]()

当limit设置为0时,表示这个检查永远不会报violation

$hold check: $hold(reference_event, data_event, time_check_limit,notifier)

当limit设置为0时,表示这个检查永远不会报violation

$setuphold check: $setuphold(reference_event, data_event, setup_time_check_limit,hold_time_check_limit,notifier)

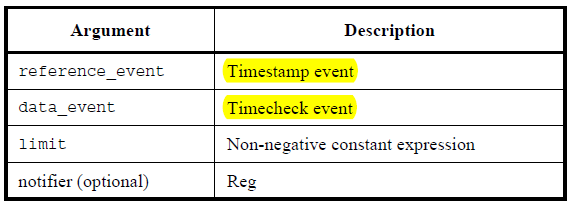

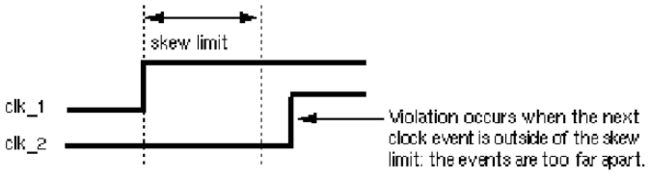

$skew(reference_event, data_event, time_check_limit, notifier)

![]()

$width(reference_event, time_check_limit, threshold)

reference必须是一个trigger的event,另一个edge作为data event,两者时间间隔大于threshold(防止glitch),小于limit。

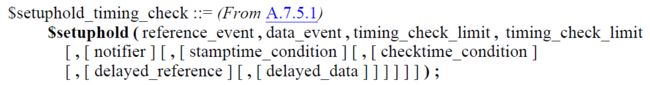

$setuphold的完整定义:支持negtive timing

notifier作为一个reg类型变量,在timing check invoke的地方声明,

当检测到timing violation时,notifier通过FF的行为,打印violation信息,并propagate X to the output。

在timing check过程中,data和reference clock的delay copysignal会被创建,

用户可以显式的定义,delayed_reference或者delayed_data。

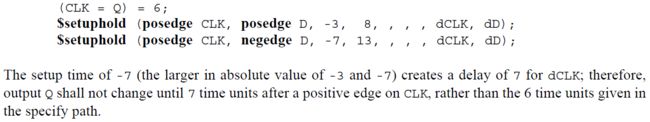

dclk在setup为负值时,表示clk延时7个cycle,在dclk之前D不再变化,就不会出现violation。

dD在hold为正值时,表示D延时13个cycle,如果dD发生在CLK之后,则不会出现violation。

在多个$setuphold的函数中,选择大的一个赋值。

在做后仿的过程中,默认选择sdf中的delay值,之后选择specify中的delay值。