Xilinx FPGA内部资源之时钟篇1

以下时钟介绍以Virtex5系列芯片作为参考芯片

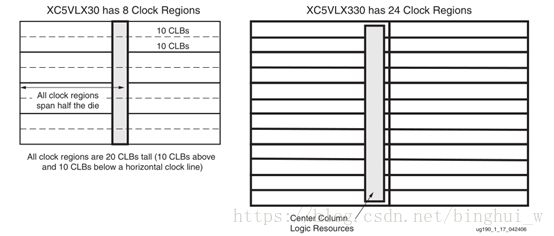

从时钟的角度可以将Xilinx FPGA划分为若干个时钟域(Clock Region),不同的FPGA芯片具有不同数量的时钟域,XC5VLX30有8个时钟域,XC5VLX330有24个时钟域。事实上每个时钟域的大小都是固定的,在Virtex5系列芯片中,每个时钟域的大小固定为20个CLB,这就导致了芯片越大,时钟域就越多。

Xilinx FPGA的时钟包括全局时钟、局部时钟和I/O时钟;下面将一一介绍。

**

全局时钟

**

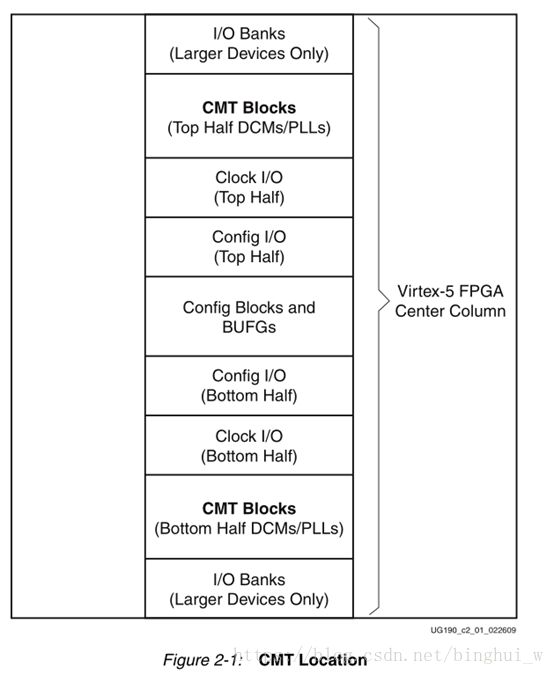

首先放一张Xilinx FPGA Virtex 5器件时钟域的整体布局图:

图中以中间灰色条块为界将FPGA分为了左右两个对称部分。全局时钟位于中间灰色条块中,局部时钟分布在左右两个对称区域。

灰色条块中包含以下各个部分,如下图所示:

对Virtex5(以下简称V5)器件来说,有32条全局时钟线,这些时钟线可以给器件中所有的时序资源提供时钟,而局部时钟的作用域仅限于该时钟所在时钟域或相邻时钟域。

这些全局时钟线只能由全局时钟缓冲器(global clock buffer)来驱动;而每一个全局时钟缓冲器通常是由一个Clock Management Tile(CMT)来驱动,以减少时钟分布式延迟,调节时钟之间的相对延迟。全局时钟的个数要多于CMT,后面我们可以看到,V5器件最多只有6个CMT,但是一个CMT可以驱动多个全局时钟。

全局时钟资源和网络包括以下几个部分:

1、 全局时钟输入(Global Clock Inputs)

2、 全局时钟缓冲器(Global Clock Buffers)

3、 时钟树和网络(Clock Tree and Nets-GCLK)

4、 时钟域(Clock Regions)

全局时钟输入

V5器件具有20个特殊的全局时钟输入位置(20条时钟输入线,它们位于灰色条块的Clock I/O),这些时钟从I/O口输入,这些I/O口在不用于时钟输入的时候还可以当做普通I/O口使用,输入的时钟可以是单端或差分。在实际工程中如果要用到这些全局时钟输入,我们可以在模块中直接例化时钟原语(Primitives)

其中IBUFG表示输入时钟为单端时钟,IBUFGDS为差分时钟输入。Verilog语言表示如下:

IBUFG #(

.IOSTANDARD("DEFAULT")

) IBUFG_inst (

.O(O), // Clock buffer output

.I(I) // Clock buffer input (connect directly to top-level port)

);

IBUFGDS #(

.DIFF_TERM("FALSE"), // Differential Termination

.IOSTANDARD("DEFAULT") // Specifies the I/O standard for this buffer

) IBUFGDS_inst (

.O(O), // Clock buffer output

.I(I), // Diff_p clock buffer input

.IB(IB) // Diff_n clock buffer input

);

V5器件还有时钟门原语(BUFGCE,后面将会介绍),用来对输入时钟进行使能控制,从而达到降低功耗的目的。

全局时钟缓冲器

每一个V5器件包含32个全局时钟缓冲器。

可以作为全局时钟缓冲器输入的信号源包括:

1、 全局时钟输入(不同的全局时钟缓冲器的输入可以共享)

2、 CMT输出(DCMs时钟输出和PLLs时钟输出)

3、 其他全局时钟缓冲器输出

4、 通用互连网络

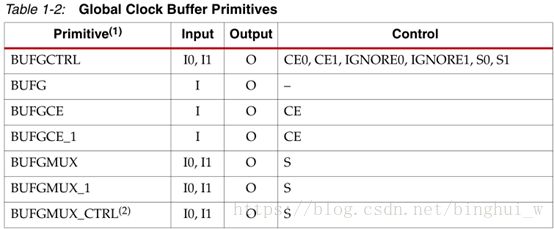

全局时钟缓冲器原语表示如下表:

表格中所有的原语都来源于BUFGCTRL原语。BUFGCTRL原语的原理图如下所示:

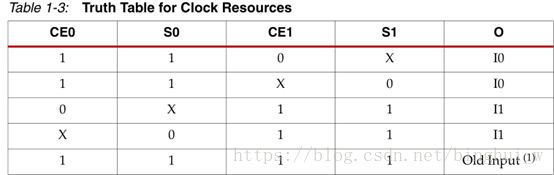

实际就是根据控制端来选择输出的时钟是I0还是I1;真值表如下所示:

BUFG :

BUFG是一个简单的全局时钟缓冲器,BUFG和BUFGCTRL的关系如图所示:

时钟缓冲器可以用作时钟的相位移动,在做输出时钟缓冲器使用时可以增强时钟的驱动能力防止负载对时钟源的干扰等等作用。在做相位移动时的输入输出时序图如下所示:

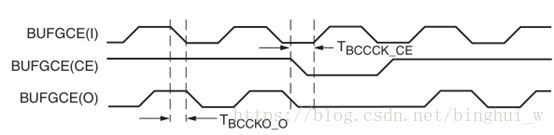

BUFGCE和BUFGCE_1

不同于BUFG,BUFGCE是一个带有时钟输入、时钟输出和时钟使能端的时钟缓冲器。使能端CE是高电平有效的,BUFGCE和BUFGCTRL的关系如下图所示:

这里注意使能端CE的使用:如果CE在输入时钟的上升沿之前变为低,那么输入时钟将不能通过BUFGCE,从而输出时钟保持为低电平。而如果CE在时钟的上升沿之后(高电平期间)变为低,将不会对输出有影响,直到上升沿到来。时序图如下所示:

BUFGCE_1和BUFGCE类似,这里不再赘述。

还有其他一些的全局时钟缓冲器,这里不再详细介绍,有需要的可以查看Xilinx官方手册。

此处需要注意的是,在实际使用中往往需要用到各个时钟缓冲器的级联使用。例如你可能会把全局时钟输入缓冲器(IBUFG和IBUFGDS)和全局时钟缓冲器(BUFG等等)级联使用,这时一定要确保IBUFG和IBUFGDS处于级联线路的最前端,否则会报错。

对差分时钟缓冲器而言,它同时也可以当做单端来使用,此时一定要确保连接的端口是P端口而不是N端口,N端口应该保持悬空。

时钟树和网络

V5时钟树是专为低抖动、低功耗而设计的。所有的全局时钟线和缓冲器都是差分互补的,这样可以得到一个更好的占空比和共模噪声抑制。

时钟域

前面对时钟域进行了简单的介绍,这里说明以下,单独看每一个时钟域,它是属于局部时钟,但是从整体上看,每一个时钟域同时也是全局时钟的组成部分;

划分时钟域的主要目的就是为了使时钟在FPGA内部能够均匀的分布,尽量减少因为距离而导致的时钟延迟从而产生时钟抖动。其中,XC5VLX30有8个时钟域,XC5VLX330有24个时钟域,如下图所示:

局部时钟

局部时钟网络包括局部时钟和I/O时钟,它是一组独立于全局时钟网络的时钟网络。不同于全局时钟信号,局部时钟信号(BUFR)只能跨越3个时钟域,其中,I/O时钟信号仅能驱动一个时钟域的信号。这些局部时钟网络对于源同步接口的设计是非常有用的。在V5器件中,局部时钟源和网络由以下四个路径和部分组成:

1、 Clock Capable I/O

2、 I/O时钟缓冲器(BUFIO)

3、 局部时钟缓冲器(BUFR)

4、 局部时钟网络

Clock Capable I/O

通常一个时钟域中含有4个clock-capable I/O管脚对(中间列除外)。Clock-capable I/O对是一种在和周围时钟资源具有特殊硬件连接位置上的常规I/O对,一些全局时钟输入也是clock-capable I/O。当这些I/O被用作时钟输入,它能够驱动BUFIO和BUFR,但是它不能直接和全局时钟缓冲器相连。需要注意的是,处于中间列位置的clock-capable I/Os 不能够驱动BUFRs。当clock-capable I/O管脚对只用单端引脚时,和前述global clock buffers一样,输入信号应该和P端相连而不是N端(只有P端是和输出直接相连的)。

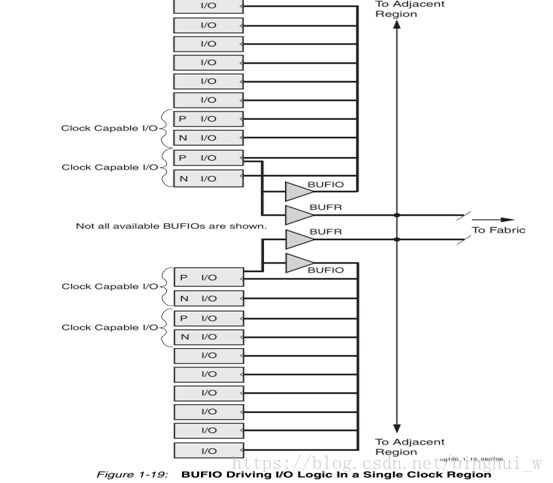

BUFIO

BUFIO(I/O Clock Buffer)独立于全局时钟,它被用来驱动位于I/O列里面的专用时钟网络。因此,BUFIOs特别适合源同步数据捕获类的应用。BUFIOs仅能由位于相同时钟域的clock-capable I/Os来驱动,一个时钟域里面包含4个BUFIO;同BUFR一样,每一个BUFIO可以驱动相同时钟域或bank中的一条I/O时钟网络,但是, BUFIO不能够驱动逻辑资源如:CLB,block RAM,IODELAY等;如下图所示:

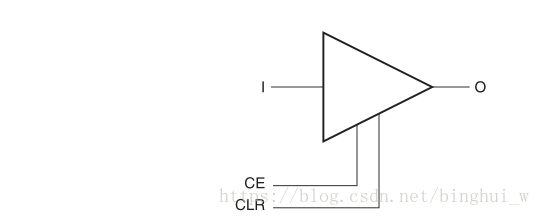

BUFIO的原语特别简单,仅包含一个时钟输入和一个时钟输出:

图中我们可以看到,clock-capable I/O是和普通I/O相类似的I/O,且是以一对的形式存在的。clock-capable I/O的输入接外部时钟,输出接BUFIO或BUFR,通过这两种缓冲器将时钟送入专用时钟网络。

BUFR

BUFR是另一种在V5器件中存在的局部时钟缓冲器,BUFR用来驱动一个时钟域中的专用时钟信号,它独立于全局时钟树。每一个BUFR可以驱动它所在时钟域里面的4条时钟网络,以及和当前时钟域相邻的两个时钟域里面的时钟网络。不同于BUFIO,BUFR除了可以驱动I/O逻辑之外,还可以驱动其他逻辑资源(CLB,blockRAM等)。此外,BUFR还可以用作时钟分频器,分频值在1到8之间的整数,它的原语如下:

以下是BUFR的用户使用模型:

图中可以看到,BUFR的输入同样来自clock-capable I/O的输出,不同于BUFIO的输出仅能指向其他I/O,BUFR的输出可以指向当前时钟区域和I/O以及各种逻辑资源,向上To Region Above,向下To Region Below;包含当前域最多时钟跨度为三个时钟域。

局部时钟网络

局部时钟网络和全局时钟网络驱动能力和设计意图相同,不同的是作用域。局部时钟网络作用域仅限于一个时钟域,不会在整个器件中传播,一个时钟域里面有四个独立的局部时钟网络:

图中大方框里面包含四个小的矩形方框,这四个矩形方框就是时钟域,在时钟域里面的四条黑线就是四条独立的局部时钟网络。

例化BUFR是使用局部时钟网络的前提,一个BUFR可以最多驱动两个相邻时钟域的局部时钟网络(共三个),而处于顶部和底部的BUFR则只能驱动顶部的下面和底部的上面相邻的时钟域。

以上的资料大部分来自于官方的数据手册,如果想要了解更多的时钟方面的内容,可以查阅官方手册UG190.