MIPI_DSI协议简要介绍

MIPI-DSI是一种应用于显示技术的串行接口,兼容DPI(显示像素接口,Display Pixel Interface)、DBI(显示总线接口,Display Bus Interface)和DCS(显示命令集,Display Command Set),以串行的方式发送像素信息或指令给外设,而且从外设中读取状态信息或像素信息,而且在传输的过程中享有自己独立的通信协议,包括数据包格式和纠错检错机制。下图所示的是MIPI-DSI接口的简单示意图。MIPI-DSI具备高速模式和低速模式两种工作模式,全部数据通道都可以用于单向的高速传输,但只有第一个数据通道才可用于低速双向传输,从属端的状态信息、像素等格式通过该数据通道返回。时钟通道专用于在高速传输数据的过程中传输同步时钟信号。此外,一个主机端可允许同时与多个从属端进行通信。

1.DSI应用电路分层

MIPI-DSI是一个应用于接口方面的通信协议,其整体电路工作依据协议所定义的各个层协同工作,其协议分层如下图所示。以下各个层的工作方式及原理:

物理层:在接收到低速发送请求时,逻辑电路将待发送的指令或数据串行化,并控制输出高摆幅低功耗电平进行低功耗传送请求,随后将指令或数据串行地加载到通道,接收端则识别传送模式完成串行数据的并行转换。当接收到高速请求后,电路发送高摆幅低功耗电平进行高速传送请求,然后将待发送数据经过串行转换之后驱动差分驱动模块以低摆幅信号在通道上传送,接收端则识别高速模式后正确地检测其同步信号将高速串行数据完成串并转换成功地接收。除此之外,总线控制权可在主机端与从属端之间交换,发送端发送放弃总线请求,接收端接收请求之后控制总线发起应答,总的过程为TA(turn around)操作。当主机端需要获取从属端接收数据的状况或者读取显示模块的参数或显示数据的时候,主机端发起TA操作,在从属端发送数据完毕之后自动发起TA操作,归还总线控制权。

通道管理层:依据设计所设定N(N最多为4)个数据通道,该层在发送端将需要发送的数据按照通道次序分成N组输送到相应的数据通道,使其经数据通道同时发送至从属端。在接收端,该层需要做的是将接收到的N组数据组合在一起恢复成原始的数据序列。

协议层:信息传送采用数据包格式,包括长数据包和短数据包。发送数据的时候,将数据按照信息类型及内容进行压包,完成ECC码的生成和 CRC码的添加。接收数据的时候,依据ECC码和CRC码就整个数据包进行检错纠错,完成对包头和数据内容的译码并合理输送到应用层中。

应用层:根据应用模块的需要,在发送端对发送的命令和数据进行初步编码转化为MIPI-DSI所规定的格式,而在接收端则将接收的数据还原为应用模块所支持的数据格式及时序要求。

物理层模块详细介绍:

按照D-PHY协议,在整个协议的物理层中,在主机端和从属端之间采用的是同步连接,时钟通道用于传送高速时钟,一个或多个数据通道用于传送低功耗数据信号或高速数据信号。每一个通道都是利用两根互连线实现主机端和从属端的连接,并且支持高速模式和低速ESCAPE模式。在高速模式下,发送端同时驱动该通道仅有的两根互连线,输出低摆幅差分信号,例如200mV;低速模式下,发送端分别驱动互连线,各自输出单端信号,但摆幅相对较大,例如1.2V。两种模式下的互连线电平如下图所示。

互连线两端是驱动单元和接收单元。驱动单元有差分发送模块(HS_TX)和低功耗单端发送模块(LP_TX),接收单元有差分接收模块(HS_RX)、低功耗单端接收模块(LP_RX)。

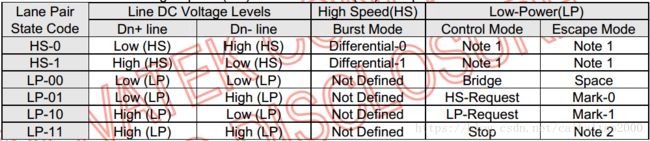

差分发送模块(HS_TX)以差分信号驱动互连线,高速通道上呈现两种状态:differential-0和differential-1。低功耗单端发送模块(LP_TX)独立地驱动两根互连线,通道上则有四种不同的状态:LP00、LP01、LP10和LP11。协议针对线路电平作了具体的定义并设置了三种工作模式:高速模式、控制模式和ESCAPE模式。如下表所示。通道默认为控制模式,线路处于STOP状态。当通道需要进入高速模式或ESCAPE模式,发送模块则需驱动线路为LP01或LP10向接收端发送请求。发送完请求序列之后便进行相应工作模式,发送LP11便可退出结束传送回到STOP控制状态。接收端需要时刻进行LP-RX接收,侦测线路电平明确通道的工作模式。

物理层釆用1对源同步的差分时钟和4对差分数据线来进行数据传输。时钟为高速时钟通道,以DDR(双边沿采样)的方式进行高速数据传输,由主机发送至从机。Lane0在HS(高速)模式时为单向数据通道,速度最大为1Gbps;在LP(低功耗)模式时为双向数据通道,速度最大为10Mbps,主要用于传输命令参数以进一步降低功耗。Lane1~Lane3为高速单向数据通道,每天Lane最大提供1Gbps的带宽,由主机发送至从机。物理层可能包含低功耗发送器(LP-TX)、低功耗接收器(LP-RX)、高速发送器(HS-TX)、高速接收器(HS-RX)。物理层传输的都是差分信号,LP模式时电压摆幅为0-1.2V,此时功耗较小;HS模式时电压摆幅为100mV-300mV,此时速度较快,功耗较大。

主机与从机之间是以同步方式进行传输数据的,并且是DDR模式,即双边沿触发;这样可以在时钟频率不变的情况下将数据传输

速率提高一倍,更加有效的利用带宽资源。主机的物理层将通道管理层分发下来的数据串行地转换成差分信号送到数据线上,同时产生差分时钟,每个数据通道是并行发送的,最多为4个通道,最小为1个通道,根据带宽需要而定。从机的物理层负责从差分串行比特流中捕获0或1,即Dp比Dn高时为1,Dn比Dp高时为0,然后组成8位数据送到通道管理层。同时还可以从数据包中检出水平同步信号和垂直同步信号。高速模式时序如下图1所示,低功耗模式如下图2所示。从图中可以看出HS模式时需要依靠高速时钟,LP模式是不需要高速时钟,只需差分信号线即可,此时的时钟由差分线Dp和Dn异或得到。

图1 高速传输模式

图2 低功耗传输模式

通道管理层详细介绍:

主机的通道管理层负责把协议层的数据分发到每个通道上,发送时的通道分配关系如下图所示。需要指出的是,每个通道不一定是同时传输完成的。相反的,从机的通道管理层负责把物理层送上来的数据组合好。

协议层的详细介绍:

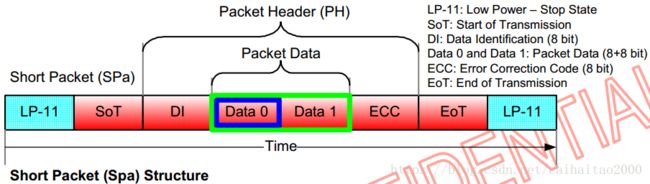

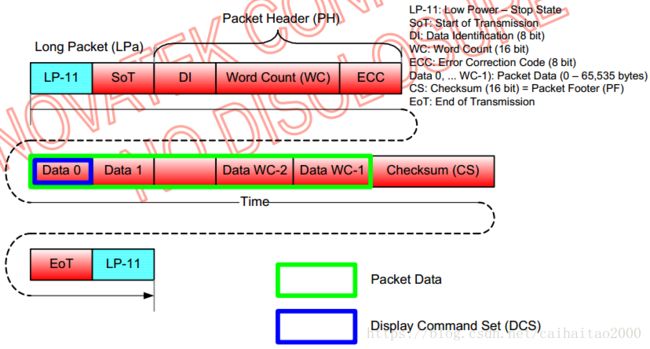

DSI协议是一个基于数据包传送的通信协议,主机端和显示模块之间传送的命令和数据基本上都以数据包格式进行。DSI所定义的数据包有两种:端数据包(short packet)和长数据包(long packet)。如下图所示。短数据包主要用于传输命令、读写寄存器。长数据包主要用用于传输大量图象数据或部分控制命令。

长数据包长度为6~65541字节,包括4byte数据包头、0~65535byte有效数据、2byte数据包尾。短数据包长度为4byte,只有数据包头。发送数据的时候,主机的协议层将根据协议进行打包,并生成ECC和CRC添加到数据包里面。相反的,从机的协议层负责把接收到的数据包根据ECC和CRC对数据包进行纠错,并且把有用数据提取出来送到应用层。

应用层详细介绍:

应用层模块直接连接到显示模块,负责着与显示模块的通信。按照协议要求,接口电路支持命令模式和视频模式,命令模式则是经过接口转换之后主机端依然得以"命令+参数"格式对显示模块进行读写操作,而视频模式下,主机端可以直接将显示数据写入显示模块,无需命令操作,实时显示视频。该模块在设计的过程中应支持命令模式和视频模式。

阅读芯片Spec笔记:

显示串行接口标准定义了主处理器和外围设备之间的协议,是遵守MIPI联盟移动设备接口的标准。DSI标准建立在现有的DPI(显示像素接口)和DBI(显示总线接口)标准上,采用MIPI联盟标准中定义的像素格式和命令集。

使用DSI接口的外设支持两种基本操作模式:命令模式和视频模式。使用哪种模式取决于外设的体系结构和能力。模式定义反映了DSI用于显示互连的主要用途,但并不是限制DSI在其他应用中操作。通常,LCD外设即可以进行命令模式操作,也可以进行视频模式的操作。

一些支持视频模式的显示模块还包括命令模式操作的简化形式,其中显示模块可以从很小的帧缓冲器中刷新其屏幕,并且可以将与主处理器的接口(DSI)关闭以降低功耗。

命令模式指的是主要采取向显示控制器的外围设备(例如显示模块)发送命令。显示控制器可能包含本地寄存器和帧缓冲器。系统可以使用命令写入和读取寄存器。主处理器可以通过向显示控制器发送命令和参数来间接控制外设的功能。主处理器还可以读取显示模块状态信息。命令模式操作需要使用双向接口。

视频模式是指从主机处理器向外设采用实时像素流的形式传输显示数据。在正常操作中,显示模块依靠主机处理器以足够的带宽提供图像数据以避免显示图像中的闪烁或其他可见伪像。视频信息只能使用高速模式进行传输。一些视频模式架构可能包括一个简单的时序控制器和小帧缓冲区,用于在待机或低功耗模式下保持屏幕图像的显示,这允许关闭DSI接口以减少功耗。为了降低复杂性和成本,视频模式的运行可能会仅使用单向传输路径。

引脚配置:

主处理器与显示模块之间的通信可以分为两个不同的级别:

接口级别:低级别通信;

数据包级别:高级别通信;

接口级别通讯详细介绍:

显示模块使用DSI接口定义的数据和时钟通道差分信号对的形式;这两种差分信号对都可以工作在低功耗(LP)或高速(HS)模式。低功耗模式意味着在单端模式下使用差分对的每一条信号线,并禁用接收端的差分对,可以在低功耗模式下工作。高速模式意味着差分信号线不是在单端模式下使用,当需要将信息从主机传输到显示模块时,在每个模式中都使用不同的模式和协议,反之亦然。下面定义了高速(HS)和低功率(LP)模式下通道的状态码。

注释:

1.当lane处于高速(HS)模式时,每条lane的低功率接收器(LP-Rx)都会检查LP-00状态码。

2.如果每条lane的低功率接收器(LP-Rx)识别LP-11状态码时,则lane返回到LP-11模式状态,也就是控制模式。

DSI-CLK Lanes详细介绍:

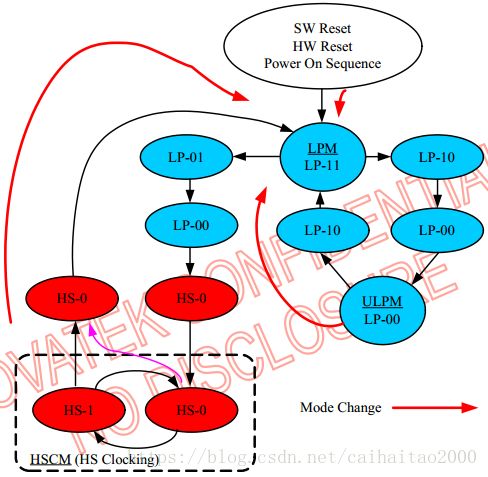

时钟lane可以工作在三种不同的功率模式:低功耗模式(LPM)、超低功耗模式(ULPM)或高速时钟模式(HSCM)。当进入或退出低功耗模式(LPM)或超低功率模式(ULPM)时,时钟lane处于单端模式(LP低功耗)。当进入或退出高速时钟模式(HSCM)时,时钟lane处于单端模式(LP低功耗)。这些进入和退出协议在单端模式中使用时钟lane来生成进入或退出时钟序列。

时钟lane在不同的功率模式的原理流程图如下图所示。

图. 时钟lane的不同功率模式

时钟lane低功耗模式:

时钟lane可以被驱动到低功率模式(LPM),当DSI-CLK通道进入LP-11状态时,有三种不同的方式:

1.在软件、硬件复位后,或上电之后进入LP-11状态。

2.在时钟lane退出超低功率模式后(ULPM,LP-00状态码)=>LP-10=>LP-11(LPM);这个序列如下所示:

图. 从ULPM状态进入LPM状态

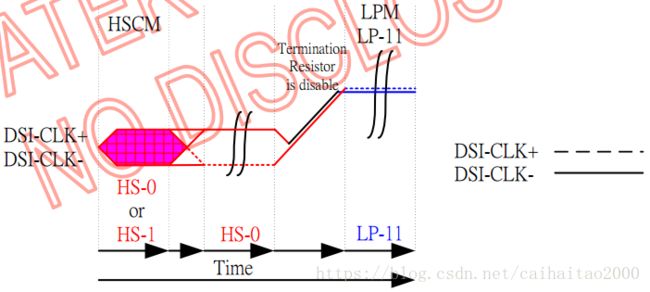

3.在时钟lane退出高速时钟模式(HSCM,HS-0或HS-1状态码)=>HS-0=>LP-11(LPM)。这个序列和所有三种模式的改变如下图所示:

图. 从HSCM状态进入LPM状态

这三种模式的切换如下面的流程图所示。

图. 时钟lane在三种工作模式下的切换流程图

时钟lane超低功耗模式:

时钟lane可以被驱动到超低功率模式(ULPM),当DSI-CLK通道进入LP-00状态码时。

进入超低功耗模式的唯一途径是从低功耗模式(LPM,LP-11状态码)=>LP-10=>LP-00(ULPM)。这个序列如下所示。

图. 时钟lane从低功耗模式进入超低功耗模式时序图

模式转换如下图所示。

图. 模式从LPM到ULPM的切换流程图

时钟lane的高速运行模式:

时钟lane可以被驱动到高速时钟模式(HSCM),DSI-CLK通道开始在HS-0和HS-1状态码之间工作。

进入高速时钟模式唯一可能性是从低功率模式(LPM,LP-11状态码)=>LP-01=>LP-00=>HS-0=>HS-0/1(HSCM)。时序图如下所示:

图. 模式从LPM到HSCM的切换流程图

模式转换如下图所示。

图. 模式从LPM到HSCM的切换流程图

高速时钟(DSI-CLK+/-)是在高速数据通道DSI-Dn+/-lane发送数据之前启动的。高速数据发送停止后,高速时钟会继续计时一段时间。

![]()

图. 高速时钟时序图

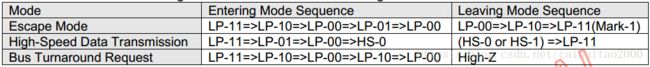

DSI接口数据Lane详细介绍:

DSI的数据lane0可以工作在不同的模式:

1.Escape模式;

2.高速数据传输模式;

3.总线反转请求模式;

这些模式及其进入状态码在下表中定义。

Escape模式详细介绍:

当数据通道处于低功耗(LP)模式时,数据通道lane0可以用于不同的Escape模式。

这些Escape模式可以用于:

1.发送"低功耗数据传输(LPDT)命令",从主机到显示模块;

2.驱动数据lane工作于"超低功耗(ULPS)"模式;

3.发送"远程复位(RAR)"命令,即重置显示模块;

4.发送"TE信号",它用于从显示模块到主机的TE触发器事件;

5.发送"确认(ACK)"信号,它用于从显示模块到主机的非错误事件;

Escape模式的基本序列如下:

开始:LP-11状态;

Escape模式进入序列:LP-11=>LP-10=>LP-00=>LP-01=>LP-00

Escape命令:当一个数据lane的状态从低到高再到低,这个变化的数据lane时展示当前数据位的值(Dn+=1,Dn-=0);

接收方就会锁存当前的值,其值就是逻辑0,接收方就会使用这种低到高到低的转换来实现内部时钟。

如果需要的话,可以加载数据;

退出Escape模式:LP-00=>LP-10=>LP-11;

结束:LP-11。

基本命令如下图所示:

图. 一般的Escape模式序列

Escape命令(EC)有8种不同形式。这八种不同的Escape命令(EC)可以分为两个不同的组:模式(Mode)或触发(Trigger)。主机通知显示模块,它控制数据通道(DSI-D0+/-)使用这个模式。主机可以通知显示模块,它将数据通道设置为低功耗模式下。主机等待从显示模块发出的事件信息,主机必须设置为触发状态。当显示模块识别传输数据包没有错误时,如果主机请求,显示模块发送给主机确认信号(ACK)。Escape命令在下表中定义。

注释:

1.这个Escape命令的支持还没有在显示模块上实现;

2.n=1、2和3;

3."X"表示支持;

4."-"表示不支持。

低功耗数据传输(LPDT):

当数据lane进入Escape模式,并且低功耗数据传输命令已经被发送给显示模块,主机可以发送数据到显示模块在低功耗模式下。

当显示模块发送数据到主机时也使用相同的序列。低功耗数据传输(LPDT)使用以下序列:

开始:LP-11状态;

Escape模式进入:LP-11=>LP-10=>LP-00=>LP-01=>LP-00;

在Escape模式下低功耗数据传输命令是:1110_0001(LSB);

加载数据:一个或多个8bit数据,当数据通道在字节之间停止(两通道都是低的)时,数据通道处于暂停状态;

退出Escape模式:LP-00=>LP-10=>LP-11;

结束:LP-11。

其时序如下图所示:

超低功耗状态(ULPS):

当数据lane进入Escape模式时,主机可以强制数据通道进入超低功率状态(ULPS)。

进入超低功耗状态(ULPS)使用以下序列:

开始:LP-11状态;

进入Escape模式:LP-11=>LP-10=>LP-00=>LP-01=>LP-00;

超低功耗进入命令:0001_1110;

超低功耗(ULPS)时主机保持数据通道为低;

退出:LP-00=>LP-10=>LP-11;

结束:LP-11。

详细序列如下图所示:

图. 进入超低功耗状态

远程复位详细介绍:

当数据通道进入Escape模式时,在远程复位触发模式下,主机可以通知显示模块进行复位操作。

远程复位重置(RAR)使用以下序列:

开始:LP-11状态;

进入Escape模式:LP-11=>LP-10=>LP-00=>LP-01=>LP-00;

远程复位命令:0110_0010;

退出:LP-00=>LP-10=>LP-11;

结束:LP-11。

操作序列如下图所示:

图. 远程复位操作序列

应答操作(ACK):

当用错误被确认时,显示模块可以通过使用ACK通知主机。

应答操作(ACK)使用以下序列:

开始:LP-11状态;

进入Escape模式:LP-11=>LP-10=>LP-00=>LP-01=>LP-00;

ACK命令:0010_0001;

退出:LP-00=>LP-10=>LP-11;

结束:LP-11。

操作序列如下图所示:

图. ACK操作序列

高速数据传输(HSDT)操作:

进入高速数据传输操作:

当时钟通道DSI-CLK+/-已经由主机设置进入高速时钟模式(HSCM)后,显示模块可以进入高速数据传输(HSDT)模式。

显示模块的数据lane进入高速数据传输模式使用如下的操作序列:

开始:LP-11状态;

HS请求:LP-01;

HS决定:LP-00=>HS-0(接收端lane终端使能);

接收端同步:011101,发送端同步:0001_1101;

结束:高速数据传输(HSDT)——准备好接收高速加载的数据。

进入高速数据传输的序列如下图所示:

图. 进入高速数据传输序列

离开高速数据传输操作:

当时钟通道DSI-CLK+/-在主机的高速时钟模式(HSCM)中时,显示模块离开高速数据传输(HSOT),并保持该HSCM直到数据通道处于LP-11模式。显示模块的数据通道离开高速数据传输模式使用如下的操作序列:

开始:高速数据传输模式;

停止:如果最后的加载位是HS-0,则主机更改为HS-1;如果最后一个加载位是HS-1,主机更改为HS-0。

结束:LP-11。

离开高速数据参数操作序列:

图. 离开高速数据传输模式序列

高速数据传输的突发操作:

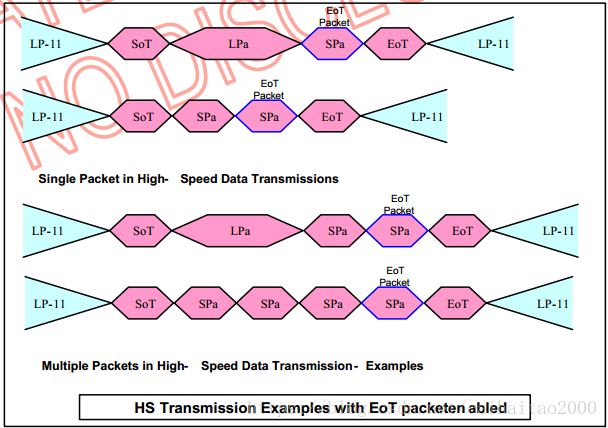

高速数据传输(HSDT)的突发操作可以由一个数据包或几个数据包组成。这些数据包可以是长或短数据包。

不同的高速数据传输突发情况如下图所示:

总线反转操作:

正在控制DSI-D0+/-数据通道的主机或显示模块可以在接收到请求信息时进行总线反转过程。

主机或显示模块可以使用相同的操作序列,使总线控制权发生反转。

如果主机想要对显示模块执行总线控制权反转操作,则按照下面的操作序列进行:

开始(主机): LP-11;

总线控制权反转请求:LP-11=>LP-10=>LP-00=>LP-10=>LP-00;

主机等待显示模块开始控制DSI-D0+/-数据lane,主机停止控制DSI-D0+/-数据lane,并设置为高阻状态;

显示模块更改到停止模式:LP-00=>LP-10=>LP-11。

总线控制权反转操作序列如下图所示:

图. 总线控制权反转过程

如果总线控制权反转请求是从显示模块发到主机,则主机和显示模块位置在上图中交换。

数据包级通信协议:

短数据包和长数据包的结构详细介绍:

在低功耗数据传输(LPDT)或高速数据传输(HSDT)模式下完成数据传输时,始终使用短数据包(SPa)和长数据包(LPa)。

数据包的长度分别是:

短包:4字节;

长包:6~65541字节;

数据包的类型(SPa或LPa)可以从它们的包头(PH)中被识别。

注释:

上图中短分包(SPa)结构和长包(LPa)结构是呈现单个包发送(包括用于每个分组发送的LP-11,SoT和EoT)。

另一种可能性是,如果数据包以多个数据包格式发送,则在数据包之间不需要SoT,EoT和LP-11。

LP-11=>SoT=>SPa=>LPa=>SPa=>SPa=>EoT=>LP-11

LP-11=>SoT=>SPa=>SPa=>SPa=>EoT =>LP-11

LP-11=>SoT=>LPa=>LPa=>LPa=>EoT=>LP-11

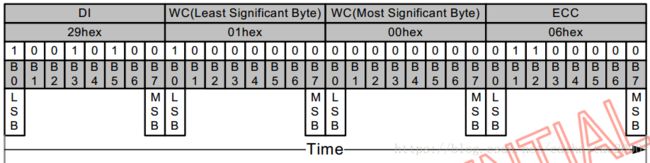

数据包中字节的位顺序:

字节的位顺序(即数据包使用的内容)是字节的最低有效位(LSB)先发送,并且字节的最高有效位(MSB)在最后发送。

具体发送顺序如下图所示:

图. 数据包中字节的位顺序

数据包的多个字节信息的位顺序:

多字节信息的字节顺序是在数据包上使用的信息的最低有效字节(LS)在第一个字节中发送,而信息的最高有效字节(MS)字节在最后发送。字数(WC)由2个字节(16位)组成,而LS字节在第一个字节发送,MS字节在最后一个字节发送。

发送顺序如下图所示:

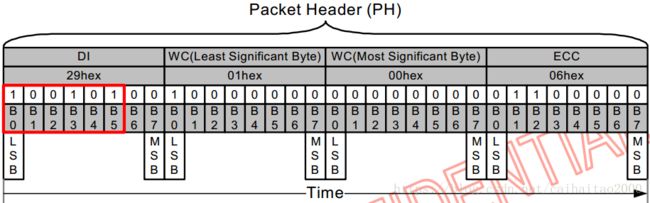

包头详细介绍:

数据包的包头是由4个字节组成。如果用于短数据包(SPa)或长数据包(LPa),这4个字节的内容是不同的。

短包:

1st:数据ID,用于表示此数据包是短包;

2st和3st:Data0和Data1;

4st:错误校验代码(ECC)。

图. 短包中的包头结构

长包:

1st:数据ID,用于表示此数据包是长包;

2st和3st:字节数量(WC);

4st:错误校验代码(ECC)。

图. 长包中的包头结构

数据标识(Data Identification)详细介绍:

数据标识(DI)是数据包标题(PH)的一部分,它由两部分组成:

虚拟通道(VC),2位,DI[7.6];

数据类型(DT),6位,DI[5.0];

数据标识(DI)结构如下表所示:

数据标识(DI)在数据包包头(PH)上的说明,以供参考:

虚拟通道(VC)在这里不做详细介绍。

数据类型(Data Type )介绍:

数据类型(DT)是数据标识(DI[5..0])结构的一部分,它用于定义数据包中使用的数据的类型。

数据类型(DT)的在位信息如下图所示:

图. 数据包头(PH)上的数据类型(DT)表示

数据类型(DT)还定义了使用的数据包是什么:短数据包(SPa)或长数据包(LPa)。从主机到显示器发送的数据类型是和显示器到主机发送的数据类型不同的。

从主机到显示模块的数据类型(DT)在下表中定义:

注释:

1.当主机希望确保在高速数据传输(HSDT)模式下有传输结束时,可以使用此功能。

2.当希望数据通道保持高速数据传输(HSDT)模式时,可以使用此功能。

3.接收方使用与数据类型(DCS写/读)相同的方式处理数据类型(通用写/读)的数据包。

4.具有1个参数的通用写入/读取:有效负载字节=命令+00h。

5.带2参数的通用写入/读取:有效负载字节=命令+参数。

6.接收方将忽略数据包,这些数据类型既未在表中列出,也未在MIPI_DSI规范中列出。

从显示模块(或其他设备)到主机的数据类型(DT):

短数据包中的数据介绍:

短数据包中的数据是在DI之后,表示需要发送的数据。

字数(WC)表示包头之后发送的字节数据(PD)的个数。

短数据包中的数据字节有2byte,Data0和Data1。发送顺序是先发送第一个字节,再发送第二个字节。如果信息长度是1个字节,则Data1的位被设置为'0'。

当虚信道(VC)为0时,短信息包(SPa)中的数据(PD),当信息长度为1或2字节时,可以参考下面的组成信息。

数据包数据信息:

Data0:带一个参数的显示命令,DI(15h);

Data1:01h(显示命令集参数);

数据包数据信息:

Data0:10h(不带参数的显示命令集,DI(05h));

Data1:00h(NULL);

长数据包中的字节数:

长数据包中的字节数(WC)是定义在数据类型(DT)之后,用来表示长数据包要发送多少个字节的数据。字节数使用两个字节表示。字节数中的两个字节发送顺序是LSB先发送,MSB后发送。长数据包中的WC格式如下图所示。

错误校验码(ECC):

错误校验码是包头的一部分,其目的用于识别包头中的错误。

错误校验码保护下面的区域:

短包:数据识别字节(8bits,D[0...7])、数据两个字节(16bits,D[8...23])和ECC(8bits:P[0…7])。

长包:数据识别字节(8bits,D[0...7])、字节数两个字节(16bits:D[8…23])和ECC(8bits:P[0…7])。

D[23…0]位和P[7…0]位的分布如下图所示:

错误校验码(ECC)可以识别一个错误或多个错误,并在某一位错误的情况下进行纠正。

错误校验码中的位(P[7…0])定义如下图所示,其中,“^”符号表示异或运算;如果存在偶数个“1”,则Pn等于1;如果存在奇数个1,则Pn等于0。计算方式如下所示。

• P7 = 0

• P6 = 0

• P5 = D10^D11^D12^D13^D14^D15^D16^D17^D18^D19^D21^D22^D23

• P4 = D4^D5^D6^D7^D8^D9^D16^D17^D18^D19^D20^D22^D23

• P3 = D1^D2^D3^D7^D8^D9^D13^D14^D15^D19^D20^D21^D23

• P2 = D0^D2^D3^D5^D6^D9^D11^D12^D15^D18^D20^D21^D22

• P1 = D0^D1^D3^D4^D6^D8^D10^D12^D14^D17^D20^D21^D22^D23

• P0 = D0^D1^D2^D4^D5^D7^D10^D11^D13^D16^D20^D21^D22^D23

P7和P6被设置为“0”,因为错误校验码(ECC)是基于64位值。但是这个实现是基于24位值的。因此,错误校验码(ECC)只需要6位(P [5 ... 0])。

详细的计算方式如下图所示:

发送方(主机或显示模块)发送数据位D[23...0]和校验码(ECC)P[7...0]。接收方(显示模块或主机)根据接收到的数据位D[23...0]计算出一个内部校验码(IECC),并将接收到的校验码(ECC)和内部校验码(IECC)进行比较。当ECC和IECC的每个功能位已完成XOR功能时,完成此比较。该XOR计算的结果是PO[7...0]。以下为参考图片说明了这种功能,其中发送方是主机,接收方是显示模块。

图. 显示模块(接收方)上的内部纠错码(IECC)

如果PO[7...0]的值为00h,发送的数据位(D[23...0])和校验码ECC(P[7...0])说明被正确的接收。如果PO[7...0]的值不为00h,发送的数据位(D[23...0])和校验码ECC(P[7...0])说明未被正确的接收。

当校验码(ECC)功能不用于发送方侧的数据值D[23...0]时,接收到的纠错码(ECC)可以是00h。

当PO[7 ... 0]的值与下表中的值进行比较时,可以定义错误的数量(一个或多个)。

校验码(ECC)中的一位错误值比照表格:

如果PO[7...0]的值打开,则检测到一个错误:校验码(ECC)的一位错误值,接收方可以纠正这一位错误,因为该找到的值还定义了是那个位出现错误位置。例如:

• PO[7…0] = 0Eh;

• 数据的位(D[23...0]),不正确的是D[3]位。

长数据包中的数据部分详细介绍:

长数据包中的数据部分是定义在包头之后的。数据部分的长度是在包头中的(数据字节数)WC部分定义的。

长数据包中的包脚部分详细介绍:

长数据包中的包脚部分是定义在数据部分之后;包脚(PF)是从长数据包(LPa)的数据部分计算出的校验和(checksum)的值。校验和使用16位循环冗余码校验(CRC)值,该值由多项式X16+X12+X5+X0生成,如下所示。

图. 16位循环冗余校验(CRC)计算

计算前将16位循环冗余校验(CRC)发生器初始化为FFFFh。数据部分的数据字节的最低有效位(LSB)是输入到16位循环冗余校验(CRC)中的第一位。以下将逐步说明16位循环冗余校验(CRC)的示例,其中长数据包(LPa)的数据部分(PD)为01h。

在本例中,数据包脚(PF)的值为1E0Eh。 这个例子(发送命令01h)如下图所示。

接收方从接收到的数据部分中(PD)计算自己的校验和值。接收方比较自己的校验和和数据包脚(PF)发送方发送的校验和内容。

如果接收方和长包包脚(PF)的自身校验和相等,则接收到的数据部分(PD)和包脚(PF)是正确的,反之亦然,计算的包脚与接收方的数据包脚(PF)的自身校验和不相等。

数据包的发送过程详细介绍:

1.从主机到显示模块的数据包传输;

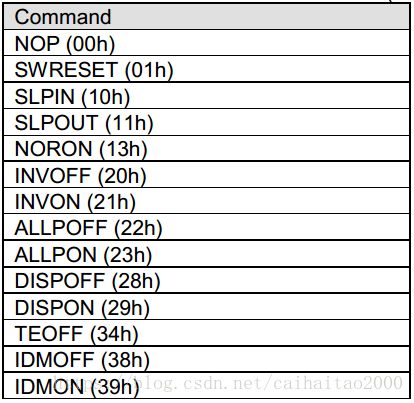

显示命令集详细介绍:

显示命令集(DCS)在章节"6.指令描述"中定义,用于主机到显示模块发送数据使用。

显示命令集(DCS)总是在数据部分(PD)的Data0上定义,它包含在短包(SPa)和长包(LPa)中,如下所示。

图. 短包(SPa)和长包(LPa)上的显示命令集(DCS)

通用写入,1个参数(GENW1-S),数据类型=00010011(13h):

此数据类型只使用于短包,是由数据类型(13h)定义的,2个有效发送字节的内容是"命令"和00h。

这些命令在下表格中定义。

短包的定义举例:

数据识别定义:

虚拟通道(VC):00b

数据类型(DT):010011b

包数据定义:

Data0:休眠(10h),显示命令

Data1:00h

错误校验码(ECC);

这写数据在短包(SPa)上的定义如下:

图. 短包示例

通用写入,2参数(GENW2-S),数据类型=00100011(23h):

此数据类型只适用于短包,是由数据类型(23h)定义的,从主机往显示模块发送命令时使用;2个有效发送字节的内容分别是"命令"和"参数"。

这些命令在下表格中定义。

短包的定义举例:

数据识别定义:

虚拟通道(VC):00b

数据类型(DT):00100011b

包数据定义:

Data0:PMCSET(3Ah),显示命令;

Data1:01h,显示命令DCS的参数;

错误校验码(ECC);

这写数据在短包(SPa)上的定义如下:

通用长写(GENW-L),数据类型=00101001(29h):

此数据类型只适用于长包,是由数据类型(29h)定义的,从主机往显示模块发送命令时使用;命令(没有参数)和写(1个或多个参数),

这些命令在下表格中定义。

备注:

Note1:短数据包(Spa)也可以使用,请参阅通用写,1个参数(GENW1-S)。

Note2:短数据包(Spa)也可以使用,请参阅通用写,2个参数(GENW2-S)。

使用长数据包发送命令(无参数)的示例如下:

数据识别定义:

虚拟通道(VC):00b

数据类型(DT):00101001b

字节数(WC):0001h

错误校验码;

数据部分:Data0,休眠10h,显示命令;

包脚部分;

示例定义如下图所示:

使用长数据包发送命令(1个参数)的示例如下:

数据识别定义:

虚拟通道(VC):00b

数据类型(DT):00101001b

字节数(WC):0002h

错误校验码;

数据部分:

Data0:伽玛设置((3Ah),显示命令;

Data1:01h,命令的参数。

包脚部分;

此长包的定义示例如下:

通用读,1个参数(GENR1-S),数据类型=00010100(14h)

此数据类型只适用于短包,是由数据类型(14h)定义的,从主机往显示模块发送命令时使用;这些命令在下表格中定义。

第一个参数(虚拟数据)不返回,因为它在MeSSI-8/16情况下完成。第一个返回的参数是DSI情况下的第二个参数。

MCU必须向显示模块定义返回数据包的最大大小。

一个用于此目的的命令是"设置最大返回包大小"(SMRPS-S),其数据类型(DT)为110111b(37h),并使用短包(SPa)在MCU发送"显示命令设置(DCS)读取,无参数"到显示模块。

下图是其时序说明。

第一步:

当主机要从显示模块返回一个字节时,主机向显示模块发送"设置最大返回数据包大小"(短包)命令,

数据识别定义:

虚拟通道(VC):00b

数据类型(DT):00110111b

返回包大小:

Data0: 01h

Data1:00h

错误校验码;

发送包的格式如下所示:

第二步:

当主机向显示模块发送"通用读取,1参数"命令时,主机希望从显示模块接收"读取ID1(DAh)寄存器"的值;

数据识别定义:

虚拟通道(VC):00b

数据类型(DT):00010100b

数据部分:

Data0: "读取ID1(DAh)",显示命令;

Data1: 00h;

错误校验码;

第三步:

在发生总线周转(BTA)后,显示模块可以向主机发送2个不同的信息;

如果发生错误以接收命令,则使用短包(SPa)的错误报告(AwER)进行确认。

收到的命令的信息。短包(SPa)或长包(LPa)。