用verilog 实现 74LS160,然后实现2000分频占空比50的分频器

因为这周有个作业要求用3个160实现一个类似2000分频占空比50的分频器,然后没用过verilog,就直接从网上抄了一个,但是并不好使,索性自己来

module LS160(clk,ep,et,ld,clr,dn,qn,cout);

input clk,ep,et,ld,clr;

output cout;

input [3:0] dn;

output [3:0] qn;

reg [3:0]temp;

reg cout;

always @(posedge clk or negedge clr)

begin

if(clr==0)

temp<=4'd0;

else

begin

if(clk==1&ld==0)

temp<=dn;

else if(clk==1&ld==1)

begin

if((ep&et)==0)

begin

temp<=temp;cout=0;

end

else

begin

temp<=temp+1;cout=0;

end

end

if(temp==4'd9)

begin

cout=1;

temp<=4'd0;

end

end

end

assign qn=temp;

endmodule

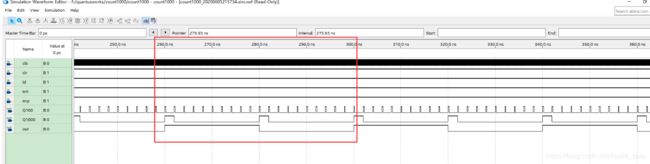

module count1000(clk,enp,ent,ld,clr,dn,qn,Q1000,Q100,out);

input clk,enp,ent,ld,clr;

input [11:0] dn;

output [11:0] qn;

output out;

reg [3:0]temp;

wire rco1,rco2,cout;

output Q100,Q1000;

reg out;

LS160 LS0 (clk,enp,ent,ld,clr,dn[3:0],qn[3:0],rco1);

LS160 LS1 (~rco1,1,1,ld,clr,dn[7:4],qn[7:4],rco2);

LS160 LS2 (rco2,1,1,ld,clr,dn[11:8],qn[11:8],cout);

assign Q100=rco2,Q1000=cout;

always@(posedge cout)

begin

if(cout==1)

out=~out;

end

endmodule