COMS原理及门电路设计

目录

1.N/P MOS管的物理结构图

2.N/P MOS管的工作原理

3.N/P MOS管的抽象模型

4.典型门电路设计

1.cmos反相器设计

2.coms与非门与或非门设计

3.与或非门、或与非门设计

4.异或、同或设计

5.设计方法总结

参考资料

关于CMOS进一步的组合逻辑与时序逻辑设计请参考:

CMOS的宽/长比、传输门与三态门、锁存器与触发器、简单版图、竞争与冒险

前言:现代集成电路就是在硅晶片上制作CMOS电路,CMOS是在集成电路设计中,同时采用两种MOS器件NMOS管和PMOS管,并通常配对出现的一种电路结构。所以理解其原理以及基本构成门电路结构是必要的。

MOSFET 金属氧化物半导体场效应晶体管 Metal-Oxide-Semiconductor Field Effect Transistor

COMS 互补金属氧化物半导体 Complementary Metal-Oxide-Semiconductor Transistor

1.N/P MOS管的物理结构图

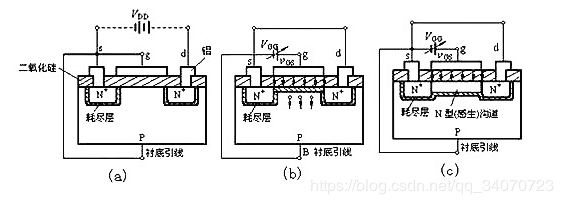

[1]以NMOS为例,在P在一块p型衬底(p-sub,衬底又叫Bulk或Body)上,通过选择掺杂形成两个的n+区,分别为源极(Source)和漏极(Drain);衬底之上用SiO2做一块绝缘层,绝缘层之上用高掺杂的多晶硅(Poly-silicon)做栅极,称作多晶硅栅,即为栅极(Grid);栅在源漏方向的长度称作栅的长L,垂直方向称为栅的宽W,需要注意的是,在数量上W比L要大。

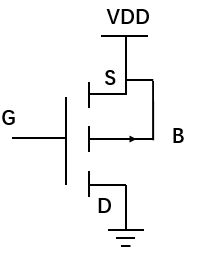

上面的图中画出了MOSFET的三个极:源(S)、漏(D)和栅(G),但其实MOSFET是个四端器件,因为还有衬底(B)没有引出管脚来。下图中将衬底引出管脚来:

在电路连接中,一般将MOS的衬底B与源S连接到一起,使其电位相等。如果衬底的电位与源电位不等,则会存在体效应,引起阈值电压的偏移。

如果不连在一起的话,其源和漏是完全对称的,也就是说源和漏是可以互换的。在MOS中,源为提供载流子的端,而漏为接收载流子的端。源和漏也正是依据这一定义来区分:NMOS中导电的载流子是电子,因此接到电路的最低电位以提供电子的是源极;而PMOS中导电的载流子是空穴,因此接到电路最高电位以提供空穴的是源极。

MOSFET中的导电沟道也是在衬底中形成:栅极与衬底之间隔有SiO2绝缘层,因此栅与源、漏、衬底之间不导通,而是形成平行板电容器,加电压时栅与衬底之间形成电场,在该电场的影响下衬底中形成导电沟道,MOS管就开始导通,因此叫场效应晶体管(Field Effect Transistor)。

集成电路中大规模应用的CMOS技术,要求在一块硅片上同时做多个NMOS和PMOS。但是NMOS与PMOS的衬底类型不同,这就要求在工艺上为其中一类晶体管做一个局部衬底,称为阱,这类晶体管就做在阱中。因此,目前采取的技术是:NMOS直接做在p衬底上,而在需要做PMOS的区域做一块掺杂的n区,称为n阱(well),PMOS就做在这个阱中。 如下图:

2.N/P MOS管的工作原理

注意上图都把衬底与源极连在一起了。

MOS管分为增强型与耗尽型,以增强型NMOS管为例[2]。

(1)vGS=0

在漏源间加电压vDS,栅源无电压时,两个N+之间无法导通,因为漏极d和源极s之间有两个背靠背的PN结,而且不论vDS的极性如何总有一个PN结处于反偏状态,漏源极间没有导电沟道,所以这时漏极电流iD≈0。如上图1(a)

(2)vGS>0

若vGS>0,则栅极和衬底之间的SiO2绝缘层中便产生一个电场。电场方向垂直于半导体表面的由栅极指向衬底的电场。这个电场能排斥空穴而吸引电子。排斥空穴:使栅极附近的P型衬底中的空穴被排斥,剩下不能移动的受主离子(负离子),形成耗尽层。吸引电子:将 P型衬底中的电子(少子)被吸引到衬底表面。如上图1(b)

导电沟道的形成:

当vGS数值较小,吸引电子的能力不强时,漏—源极之间仍无导电沟道出现,如图1(b)所示。vGS增加时,吸引到P衬底表面层的电子就增多,当vGS达到某一数值时,这些电子在栅极附近的P衬底表面便形成一个N型薄层,将两个N+区相连通,在漏——源极间形成N型导电沟道,其导电类型与P衬底相反,故又称为反型层,如图1(c)所示。vGS越大,作用于半导体表面的电场就越强,吸引到P衬底表面的电子就越多,导电沟道越厚,沟道电阻越小。

开始形成沟道时的栅——源极电压称为开启电压,用VT表示。

上面讨论的N沟道MOS管在vGS<VT时,不能形成导电沟道,管子处于截止状态。只有当vGS≥VT时,才有沟道形成。这种必须在vGS≥VT时才能形成导电沟道的MOS管称为增强型MOS管。沟道形成以后,在漏——源极间加上正向电压vDS,就有漏极电流产生。

vDS对iD的影响:

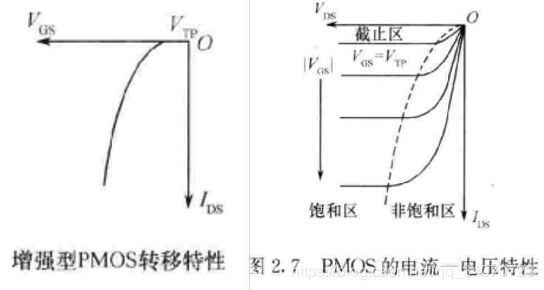

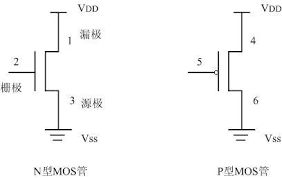

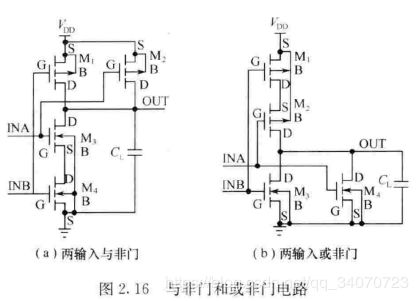

漏极电流iD沿沟道产生的电压降使沟道内各点与栅极间的电压不再相等,靠近源极一端的电压最大,这里沟道最厚,而漏极一端电压最小,其值为VGD=vGS-vDS,因而这里沟道最薄,如图2(a)。但当vDS较小(vDS 随着vDS的增大,靠近漏极的沟道越来越薄,当vDS增加到使vGD=vGS-vDS=VT(或vDS=vGS-VT)时(疑问1:为什么夹断点的vDS电压是这个关系?),沟道在漏极一端出现预夹断,如图2(b)所示。再继续增大vDS,夹断点将向源极方向移动,如图2(c)所示。由于vDS的增加部分几乎全部降落在夹断区,故iD几乎不随vDS增大而增加,管子进入饱和区(疑问2:为什么“夹断”后还有电流并且电流饱和不变?),iD几乎仅由vGS决定。其iD随着vDS变化的图如图3左图。 增强型与耗尽型的区别:增强型需要vGS>VT时才会使得漏源电流产生,耗尽型则vGS>0即可,不存在阈值电压,不加电压导电沟道就有了。 原因:制造N沟道耗尽型MOS管时,在SiO2绝缘层中掺入了大量的碱金属正离子Na+或K+(制造P沟道耗尽型MOS管时掺入负离子),如图1(a)所示,因此即使vGS=0时,在这些正离子产生的电场作用下,漏——源极间的P型衬底表面也能感应生成N沟道(称为初始沟道),只要加上正向电压vDS,就有电流iD。 PMOS管与NMOS管相似,只是相反的是需要在栅上相对于源极施加负电压,栅上施加的是负电荷电子,而在衬底感应的是可运动的正电荷空穴和带固定正电荷的耗尽层。当达到强反型时(到达阈值电压VTP),在相对于源端为负的漏源电压的作用下,源端的正电荷空穴经过导通的 P 型沟道到达漏端,形成从源到漏的源漏电流。同样的vGS越负(绝对值越大),沟道的导通电阻越小,电流的数值越大[4]。其电流特性如下图2.7所示: 疑问回答: 1.为什么夹断点的vDS电压是这个关系? 导电沟道里都是电子,vDS增大会使电子都流向D端,从而使得沟道靠近D端导电沟道变窄,当vDS=vGS-VT时,他们正好相互抵消这种吸引电子的能力,所以就出现夹断点。 2.为什么“夹断”后还有电流并且电流饱和不变? 在夹断后出现的是耗尽层,横向电场大部分落在这个区,电场方向漏端指向源端,该夹断区边缘的反型电子(nmos),由于扩散,一旦电子进入该区域就会被电场加速扯到漏端,从而形成电流。 至于为什么电流恒定即饱和,因为电子迁移率不再与电场成线性增加的关系了,电子漂移速度达到饱和[3]。 芯片中,我们使用MOS管时是让其工作在饱和区的。也就是说: 对于NMOS管来说,在其漏极加电压VDD,源极接地: 在栅极加高电平(vGS>VT),则导通,导通电阻(D与S之间的电阻)很小,则S端为高电平; 在栅极加低电平 ,则截止,导通电阻(D与S之间的电阻)很大,S端为低电平; 当然实际这么接会烧坏管子的,这么画为了方便理解。 对于PMOS管来说,在其源极加电压VDD,漏极接地: 在栅极加低电平(|vGS|>|VT|),则导通,导通电阻(S与D之间的电阻)很小,则D端为高电平; 在栅极加高电平 ,则截止,导通电阻(S与D之间的电阻)很大,D端为低电平; 当然实际这么接会烧坏管子的,这么画为了方便理解。 两种MOS的另一种画法: 如图2.15:输入高电平,下面的NMOS导通电阻极小,上面的PMOS截止电阻极大,根据电阻串联的分压原理,所以OUT高电平。输入低电平就相反。其中CL为负载电容,输出的电平转换时间取决于CL[5]。 如图2.16(a)与非门NAND:上并下串,任意一个输入为低电平,下面有NMOS会截止,电阻极大而输出高电平 如图2.16(b)或非门NOR:上串下并,任意一个输入为高电平,上面有PMOS会截止,电阻极大而输出低电平 设计如下与或非门: 如上图2.17所示: 设计如下或与非门: 如上图2.18所示,其分析原理与与或非门相似。 上图可以看出,同或的两种设计中,下面的方法使用更少的MOS管。 至此,我们可以总结一下, (1)输出out将设计分成上面PMOS下面NMOS两层,且上下数量相等,即一个输入要占用N与P各一个(输入没有取反的情况,若取反的话要加一个倒向器),即m个输入要2m个mos管。 (2)整体是与非逻辑时,NMOS串联,PMOS并联;整体是或非逻辑时,NMOS并联,PMOS串联 以或与非门为例,我们先把整体看成三部分的与非,那么这三部分的NMOS就是串联,PMOS并联,然后再看各部分内部是或关系,NMOS就是并联,PMOS串联。 (3)设计步骤: 根据逻辑公式化简为整体与非门或者整体或非门的形式,然后用门电路画出来,最后用MOS管画出来。 [1]从器件物理层面看MOSFET的内部结构 https://www.cnblogs.com/Atsea/p/3723858.html [2]详解,N沟道MOS管和P沟道MOS管https://blog.csdn.net/wuhenyouyuyouyu/article/details/83585461 [3]mos管在饱和区时,其电子沟道已经被夹断了,为什么还有漏电流存在了? [4]VLSI设计基础,第三版,李伟华著(主要参考书,这是我本科学过的一本书) [5]反向器的性能分析https://wenku.baidu.com/view/c5491b795acfa1c7aa00cc0b.html3.N/P MOS管的抽象模型

4.典型门电路设计

1.cmos反相器设计

2.coms与非门与或非门设计

3.与或非门、或与非门设计

![]()

4.异或、同或设计

5.设计方法总结

参考资料: