基于ZYNQ的LVDS收发传输仿真

基于ZYNQ的Lvds收发仿真实验

1.工程概述:

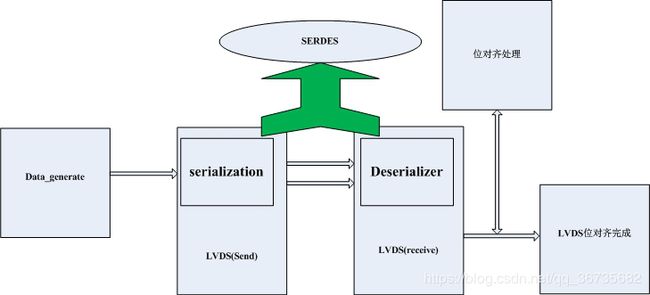

图1.1

我们通过分别建立LVDS发送和接收模块,将两者进行互联,实现LVDS数据收发实验。数据源通过编写数据产生模块来实现所需传输的数据。时钟源采用VIVADO自带的IP核。从图1.1可以看出,LVDS发送模块具备serialization功能,它是将Dater_generate发送过来的并行数据进行串化处理,接收模块具备deserializer功能。

为什么要进行serialization和deserializer 处理呢?原因是因为一般通过LVDS传输的数据速率都比较快,一般的FPGA IO接口是难以读取较高速率的数据信号。例如摄像头输出的LVDS信号速率会达到600M以上。又有一个问题,为什么不直接采用并行数据进行传输呢,并行传输速率不应该更快吗?其实在Serdes之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据。如图1.2和图1.3所示,分别是系统同步和源同步并行接口。

图1.2 system synchronous interface

图1.2为系统同步接口方式,该方式随着频率的增加,有以下几个因素限制了有效数据窗口宽度。

(1)时钟到达两个芯片的延时不相等。

(2)并行数据各个bit的传播延时不相等。

(3)时钟的传播延时和数据的传播延时不一致。

这几种因素限制了有效数据窗口宽度,从而不能够传输高速数据信号。

图1.3 source synchronous interface

图1.3为源同步接口,该方式是在发送端Tx把时钟伴随数据一起发送出去, 限制了时钟延时差对有效数据窗口的危害。通常在发送端芯片内部,源同步接口把时钟信号和数据信号作一样的处理,也就是让它和数据信号经过相同的路径,保持相同的延时。这样PVT变化时,时钟和数据会朝着同一个方向增大或者减小相同的量,对skew最有利。

利用源同步接口,数据的有效窗口可以提高很多。通常频率都在1GHz以下。在实际应用中可以见到如SPI4.2接口的时钟可以高达700MHz x 16bits位宽。DDR Memory接口也算一种源同步接口,如DDR3在FPGA中可以做到大约800MHz的时钟。

要提高接口的传输带宽有两种方式,一种是提高时钟频率,一种是加大数据位宽。那么是不是可以无限制的增加数据的位宽呢?这就要牵涉到另外一个非常重要的问题-----同步开关噪声(SSN)。

SSN = L N di/dt。L是芯片封装电感,N是数据宽度,di/dt是电流变化的斜率。

随着频率的提高,数据位宽的增加,SSN成为提高传输带宽的主要瓶颈。不可能靠无限的提高数据位宽来继续增加带宽。一种解决SSN的办法是使用差分信号替代单端信号,使用差分信号可以很好的解决SSN问题,代价是使用更多的芯片引脚。使用差分信号仍然解决不了数据skew的问题,很大位宽的差分信号再加上严格的时序限制,给并行接口带来了很大的挑战。

源同步接口的时钟频率已经遇到瓶颈,由于信道的非理想(channel)特性,再继续提高频率,信号会被严重损伤,就需要采用均衡和数据时钟相位检测等技术。这也就是SerDes所采用的技术。SerDes是Serializer-Deserializer的简称。因此这也就解释了为什么采用这种方式解决高速数据传输的原因。

2.工程建立:

2.1添加lvds IP核,建立lvds 接收模块。

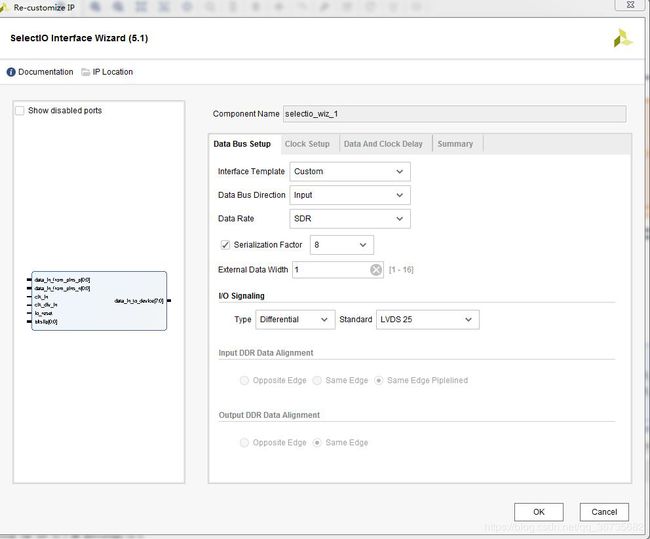

Vivado中没有专用lvds核,需要添加selection interface wizard IP,双击打开该IP,如图2.1所示。在interface template 中点击下拉菜单,可以选择Custom 或 chip to chip。在Data Bus Direction 中选择 input用于接收数据,在serialization factor 前打勾,表示使能serdes功能,完成数据的并/串转换,我们选择serialization factor值为8,表示将8位数据位宽转换为串行数据。External Data Width 表示serdes的通道数目,设为1,表示只有1个serdes传输通道。 I/O signaling选项中TYPE 选择Differential差分信号,电平标准选择LVDS25。

图2.1

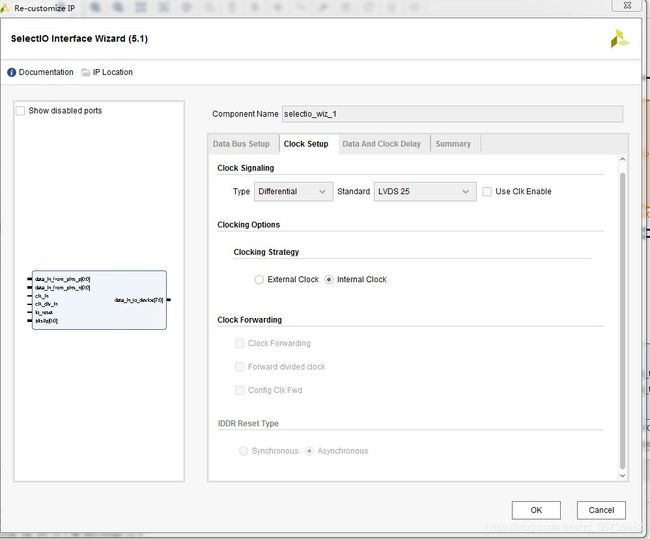

如图2.2所示,CLOCK Setup 页面中时钟类型同样为差分信号,电平标准同样为LVDS25。Clocking strategy 选择内部时钟(internal clock)。

图2.2

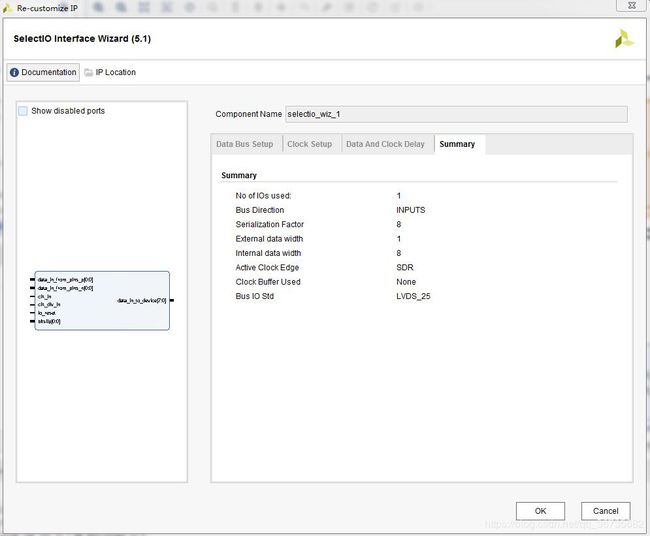

其他选项默认,如图2.3和2.4所示:

图2.3

图2.4

2.2添加lvds IP核,建立lvds 发送模块。

发送模块与接收模块设置基本一致,只有在图2.1中将Data Bus Direction 中选择 output用于发送数据。

2.3数据产生模块。

FPGA 内部产生固定的1024 字节为单位的有效数据帧以及作用同步的pattern 数据,通过LVDS 发送出去。模块代码如下:

module data_generate(

input clk,

input reset,

output BS_EN,

output [7:0] data_output

);

parameter PATTERN = 8’b1100_1101; //pattern when training timing

//0-2047计数,0-1023时发送固定pattern = 8'hbc,1024-2048发送递增数据

reg[7:0] data;

reg[15:0] cnt;

always @(posedge clk)

if(reset)

cnt <= 16'd0;

else if(cnt < 2048)

cnt <= cnt+1'b1;

else

cnt <= 16'd0;

wire pattern_en = (cnt < 16'd1024); //发送pattern有效标志位

wire data_en = (cnt >= 16'd1024); //发生1024个数据有效标志位

wire data_rst = (cnt == 16'd1024);

always@(posedge clk )

if(reset)

data <= 8'd0;

else if(pattern_en)

data <= PATTERN;

else if (data_en) begin

if(data_rst)

data <= 8'd0;

else

data <= data + 1'b1;

end

assign data_output = data;

assign BS_EN = pattern_en;

endmodule

2.4位对齐模块:

模块对接收到的LVDS数据进行位对齐判断和处理。代码如下:

module lvds_bitslip(

input clk,

input rst,

input bitslip_en,

input [7:0] data_to_device,

output bitslip,

output bitslip_done

);

parameter PATTERN = 8’b1100_1101; //pattern when training timing

reg bslp;

reg bs_done;

reg [2:0] BS_STATE ;

always @ (posedge clk)

if(rst) begin

bslp <= 0;

BS_STATE <= 3’d0;

bs_done <= 0;

end

else begin

case(BS_STATE)

3’d0: begin

bslp <= bslp;

bs_done <= bs_done;

BS_STATE<= BS_STATE +1’b1;

end

3’d1: begin

if(data_to_device == PATTERN && bitslip_en && (!bs_done)) begin

BS_STATE<= BS_STATE +1’b1;

end

else if (bs_done) begin

BS_STATE<= BS_STATE;

bslp <= bslp;

bs_done <=bs_done;

end

else begin

bs_done <= 0;

BS_STATE <= 3’d5;

end

end

3’d2: begin

if(data_to_device == PATTERN) begin

BS_STATE<= BS_STATE +1’b1;

end

else begin

BS_STATE<= 3’d1;

end

end

3’d3: begin

bs_done <= 1;

BS_STATE<= BS_STATE +1’b1;

end

3’d4: begin

BS_STATE<= 3’d0;

end

3’d5: begin

bslp <= 1;

BS_STATE<= BS_STATE +1’b1;

end

3’d6: begin

bslp <= 0;

BS_STATE<= 3’d0;

end

default: begin

bslp <= 0;

bs_done <= 0;

BS_STATE<= 3’d0;

end

endcase

end

assign bitslip_done = bs_done;

assign bitslip = bslp;

Endmodule

2.5打包IP核

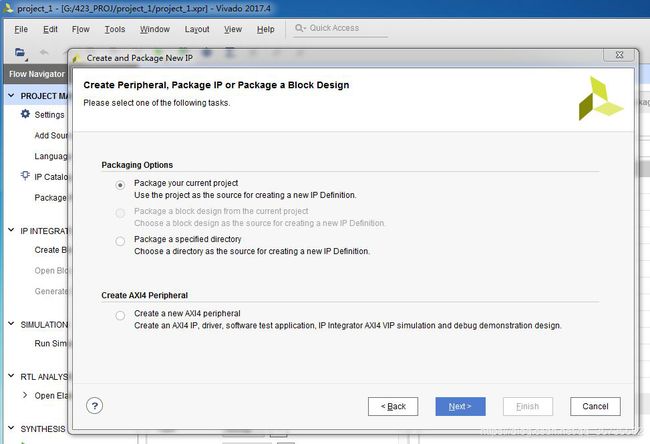

将编辑好的verilog添加至vivado工程中,点击Tools,紧接着点击create and package New IP。如图2.5所示。

点击NEXT,如图2.6所示:

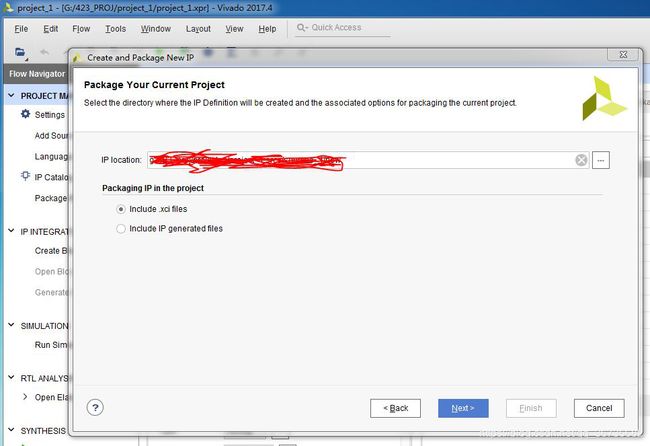

点击NEXT,如图2.7所示,选择下新建IP目录。

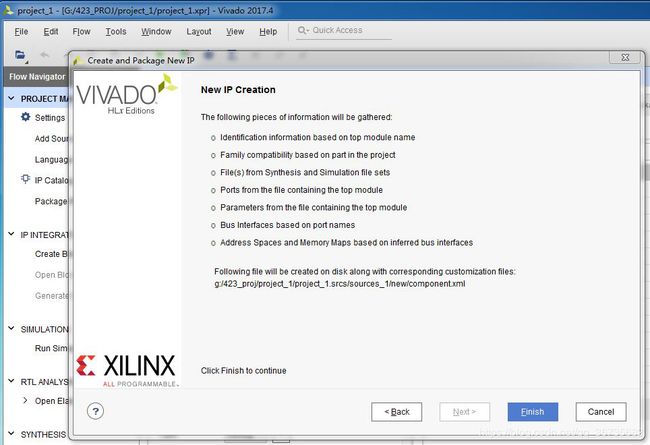

点击NEXT,如图2.8所示,点击Finish,IP创建完成。

创建完成后如何将所创建的IP添加至VIVADO 软件的IP库?

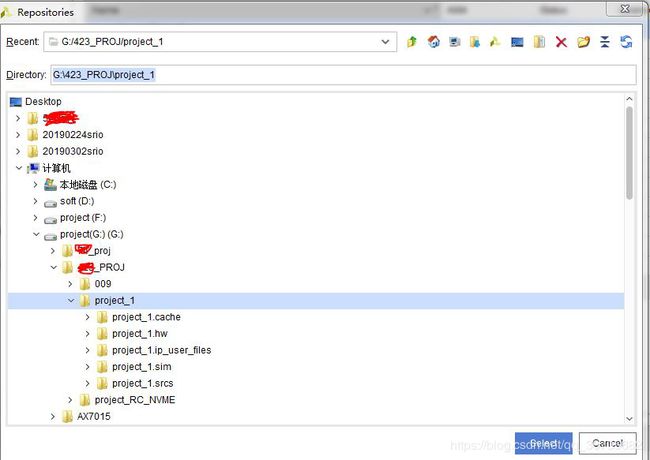

如图2.9所示,点击IP Catalog,右击 vivado repository.紧接着点击add repository.如图2.10,选择我们所创建的IP文件目录,选择好后,点击select后如图2.11所示。点击OK完成IP的添加。

图2.11

最终将所有模块添加进去后,所建工程如图2.12所示:

图2.12

3.工程仿真

建立好仿真工程文件,进行仿真。仿真代码如下:

`timescale 1ns / 1ps

module lvds_tb( );

reg clk_in ;

reg reset;

wire[7:0] data_in_to_device_0;

wire bitslip_done;

wire reset_out;

initial begin

clk_in = 0;

forever # 5 clk_in = ~clk_in;

end

initial begin

reset = 1;

# 10 reset = ~reset;

end

lvds_wrapper U1 (

.bitslip_done(bitslip_done),

.clk_in(clk_in),

.data_in_to_device_0(data_in_to_device_0),

.reset(reset),

.reset_out(reset_out)

);

endmodule

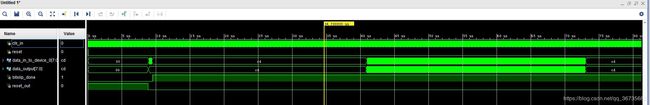

仿真结果如下所示:

先更新这么多吧,后续再继续更新。