AXI4协议学习(三) Transaction属性(ARCACHE和AWCACHE信号)

Modifiable和Non-modifiable transaction

注:用AxCACHE[3:0]表示ARCACHE[3:0]信号或者AWCACHE[3:0]信号

Non-modifiable transaction

★Non-modifiable:当AxCACHE[1] = Low,则是Non-modifiable

★Non-modifiabletransaction 不能被拆分成多个transactions也不能与其它transactions合并。

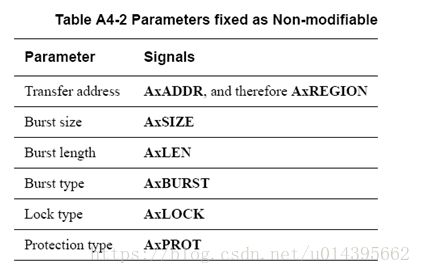

★下图所示的信号在传输过程中不能被改变:

注意:

如果一个Non-modifiable transaction的burst length大于16,或者在AxSIZE比总线宽度大的时候,必须将transaction拆解掉,那么它可以被拆解成多个transactions,那么:

◆每个transaction的burst length会减少

◆各个bursts的地址字段也会相应变化

这些变化都是被允许的

★传输过程中transaction ID和QoS信号可以被改变

Modifiable transaction

★一个transaction可以被分解成多个transactions

★多个transactions可以合并成一个transaction

★读transaction可以fetch比所需更多的data

★写transaction可以access比所需更大的地址范围,但是要用WSTRB信号标出有效地址

★AxADDR、AxSIZE、AxLEN、AxBURST可以被改变

★AxLOCK、AxPROT不能被改变

AXI4存储类型

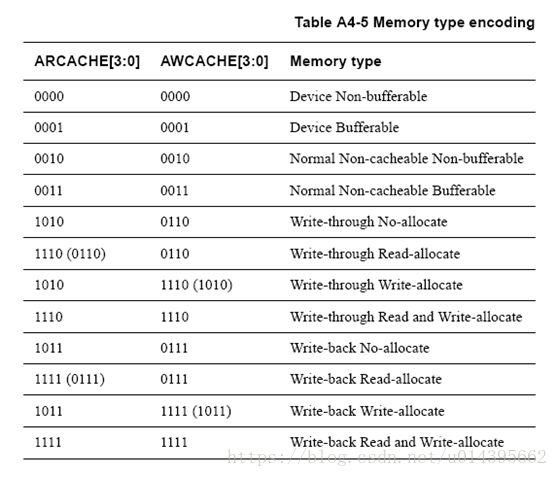

★AXI4里面的存储类型如下图所示:

注:表中没有出现的AxCACHE的值被保留

★各存储类型的要求:

▼DeviceNon-bufferable:

◆write response必须从final destination得到

◆Read data 必须从final destination得到

◆Transactions are non-modifiable(cacheable)

◆读不能被prefetched,写不能被merged.

◆来自于同一ID并到同一个Slave的所有Non-modifiable 读写 transactions必须保持顺序。

▼Device Bufferable:

◆write response可以从一个中间节点得到

◆Write transaction必须对final destination及时可见(也就是说,Write transaction 必须到达final destination, 而不能被永远存在buffer里)

◆Read data必须从final destination得到

◆Transactions are non-modifiable

◆读不能被prefetched,写不能被merged.

◆来自于同一ID并到同一个Slave的所有Non-modifiable 读写 transactions必须保持顺序。

!对于读transactions,Device Non-bufferable 与 Device Bufferable的Memory type requirements 相同

▼Normal Non-Cacheable Non-bufferable

◆write response必须从finaldestination 得到

◆Read data 必须从final destination得到

◆Transactions are modifiable

◆写可以merge

◆到有重叠目的地址的来自于同一ID的读写transactions必须保持顺序

▼Normal non-cacheable bufferable

◆write response可以从一个中间节点得到

◆Write transaction必须对finaldestination及时可见

◆Read data 要么从final destination 得到,要么从一个正在到它的final destination 的write transaction得到(“它”指write transaction)

◆如果read data从一个write transaction得到,它必须是该write的最近版本,并且,这个data不能被缓存下来。

◆到有重叠目的地址的来自于同一ID的读写transactions必须保持顺序

▼write-through No-allocate

◆write response可以从一个中间节点得到

◆Write transaction必须对finaldestination及时可见

◆Read data可以从中间的cache得到

◆Transactions are modifiable

◆Reads可以被prefetched

◆Writes可以被merged

◆Cache lookup is required

◆到有重叠目的地址的来自于同一ID的读写transactions必须保持顺序

◆建议不要对read and write transactions 进行 allocation操作

▼Write-through Read-allocate/ Write-through Write-allocate/Write-throughRead and Write-allocate

◆同Write-through no allocate

▼Write back No-allocate

◆write response可以从一个中间节点得到

◆Write transaction可以对finaldestination不及时可见

◆Read data可以从中间的cache得到

◆Transactions are modifiable

◆Reads可以被prefetched

◆Writes可以被merged

◆Cache lookup is required

◆到有重叠目的地址的来自于同一ID的读写transactions必须保持顺序

◆建议不要对read and write transactions 进行 allocation操作

▼Write-back Read-allocate/ Write-back Write-allocate/Write-back Read and Write-allocate

◆同Write-back no allocate

Mismatched AXI4 存储属性

▼多个Masters在尝试access同一个memory area的时候,会出现mismatched memory attributes.

▼所有的Masters必须在Cacheability上达成共识:

◆AxCACHE[3:2]=00则是not cacheable

◆AxCACHE[3:2]!=00则是cacheable

▼对于Bufferable的region,所有Master可以通过non-bufferable的transaction去access它

▼对于Normal Non-cacheable的region,所有Master可以通过Device memory transaction(Device Bufferable和Device Non-bufferable)去access它