ZYNQ DDS产生载波FFT变换

vivado2017.4

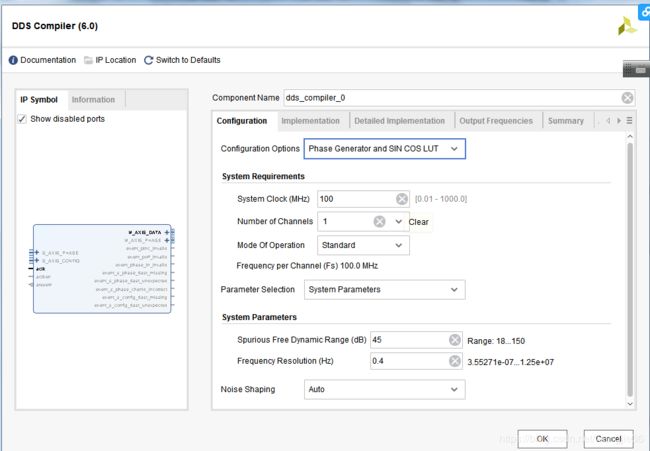

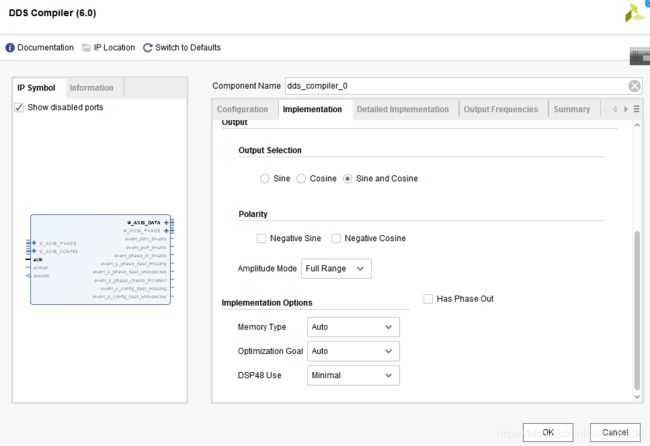

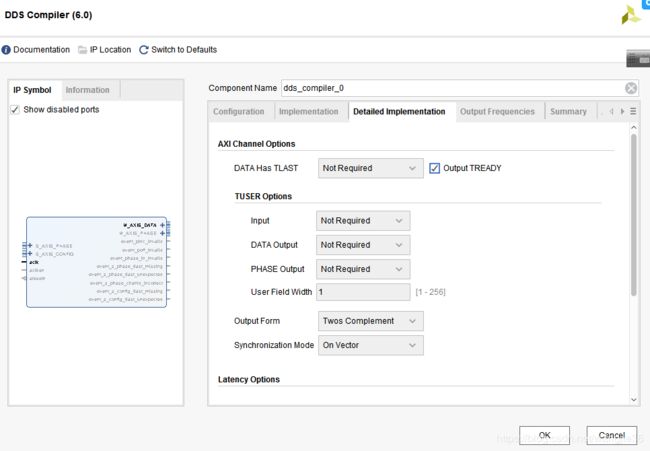

1,DDS的配置

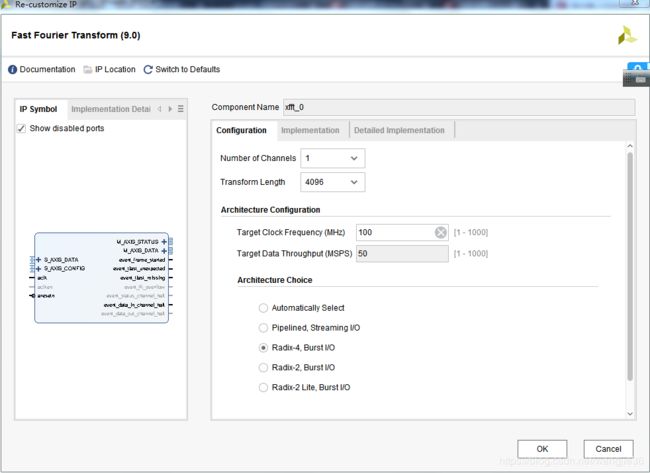

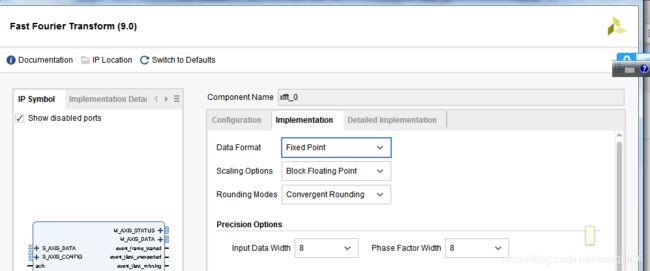

2,FFT ip核配置

3,代码

`timescale 1ns / 1ps

module fft(

input aclk,

input aresetn,

output [7:0] fft_real,

output [7:0] fft_imag,

output [17:0]data,

output [15:0]dds_m_data_tdata,

output [11:0]xk_index

);

wire [15:0] dds_m_data_tdata;

wire dds_m_data_tvalid;

wire dds_m_data_tlast;//未使用

dds_compiler_0 dds_MHz (

.aclk(aclk),

.aresetn(aresetn),

.m_axis_data_tdata(dds_m_data_tdata),

// .m_axis_data_tready(fft_s_data_tready),

.m_axis_data_tvalid(dds_m_data_tvalid)

);

//----------------------FFT core-------------------

wire [7:0] fft_s_config_tdata;//[0:0]FWD_INV_0

wire fft_s_config_tready;

wire fft_s_config_tvalid;

wire [7:0] fft_m_status_tdata;

wire fft_m_status_tvalid;

wire [15:0] fft_m_data_tdata;

wire fft_m_data_tlast;

wire [23:0] fft_m_data_tuser;//[11:0]XK_INDEX

wire fft_m_data_tvalid;

wire fft_event_frame_started;

wire fft_event_tlast_unexpected;

wire fft_event_tlast_missing;

wire fft_event_data_in_channel_halt;

wire [11:0] xk_index;

assign xk_index = fft_m_data_tuser[11:0];

assign fft_s_config_tdata = 8'd1;//定义FFT模块配置信息(第0位为1表示用FFT,为0表示用IFFT)

assign fft_s_config_tvalid = 1'd1;//FFT模块配置使能,从一开始就拉高,表示已经准备好要传入的配置数据了

xfft_0 usr_fft(

.aclk(aclk),//Rising-edge clock

.aresetn(aresetn),//(低有效)Active-Low synchronous clear (optional, always take priority over aclken); A minimum aresetn active pulse of two cycles is required

//S_AXIS_DATA

.s_axis_data_tdata(dds_m_data_tdata),//IN Carries the unprocessed sample data: XN_RE and XN_IM

.s_axis_data_tlast(dds_m_data_tlast),//IN Asserted by the external master on the last sample of the frame

// .s_axis_data_tready(fft_s_data_tready),//OUT Used by the core to signal that it is ready to accept data

.s_axis_data_tvalid(dds_m_data_tvalid),//IN Used by the external master to signal that it is able to provide data

//S_AXIS_CONFIG

.s_axis_config_tdata(fft_s_config_tdata),//IN Carries the configuration information

.s_axis_config_tready(fft_s_config_tready),//OUT Asserted by the core to signal that it is ready to accept data

.s_axis_config_tvalid(fft_s_config_tvalid),//IN Asserted by the external master to signal that it is able to provide data

//M_AXIS_STATUS

.m_axis_status_tdata(fft_m_status_tdata),

.m_axis_status_tvalid(fft_m_status_tvalid),

//M_AXIS_DATA

.m_axis_data_tdata(fft_m_data_tdata),//OUT Carries the processed sample data XK_RE and XK_IM

.m_axis_data_tlast(fft_m_data_tlast),//OUT Asserted by the core on the last sample of the frame

.m_axis_data_tuser(fft_m_data_tuser),//OUT Carries additional per-sample information: XK_INDEX, OVFLO and BLK_EXP

.m_axis_data_tvalid(fft_m_data_tvalid),//OUT Asserted by the core to signal that it is able to provide status data

//EVENTS

.event_frame_started(fft_event_frame_started),//Asserted when the core starts to process a new frame

.event_tlast_unexpected(fft_event_tlast_unexpected),//Asserted when the core sees s_axis_data_tlast High on a data sample that is not the last one in a frame

.event_tlast_missing(fft_event_tlast_missing),//Asserted when s_axis_data_tlast is Low on the last data sample of a frame

.event_data_in_channel_halt(fft_event_data_in_channel_halt)//Asserted when the core requests data from the Data Input channel and none is available

);

//----------------将FFT/IFFT处理完的信号传出(虚部/实部分别传出)-------

assign fft_real = fft_m_data_tdata[7:0];

assign fft_imag = fft_m_data_tdata[15:8];

assign data=fft_real*fft_real+fft_imag*fft_imag;

endmodule

testbench测试代码:

`timescale 1ns / 1ps

module fft_testbench( );

reg aclk,aresetn;

wire [7:0] fft_real,fft_imag;

wire [15:0]dds_m_data_tdata;

wire [11:0]xk_index;

wire [17:0]data;

fft fft_test(

.aclk(aclk),

.aresetn(aresetn),

.fft_real(fft_real),

.fft_imag(fft_imag),

.dds_m_data_tdata(dds_m_data_tdata),

.xk_index(xk_index),

.data(data)

);

initial begin

aclk = 0;

aresetn = 0;//低有效

#10 aresetn = 1;

end

always #5 aclk=~aclk;//时钟频率100MHz

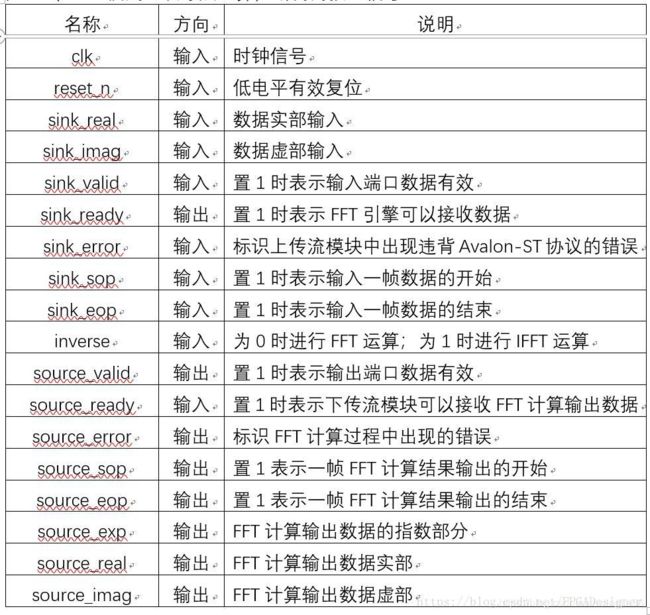

4,FFT IP核

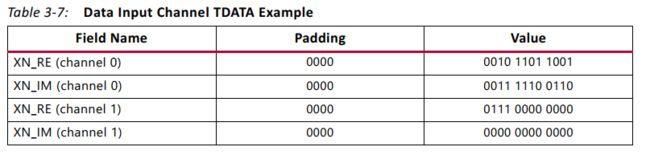

(1)FFT ip数据输入方式:

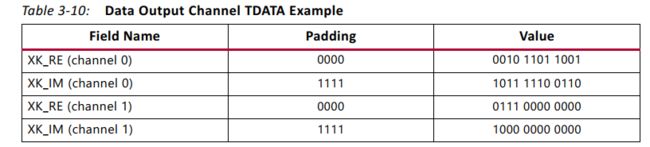

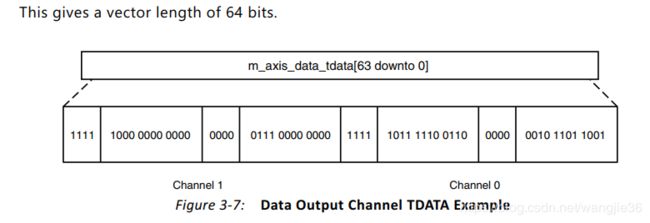

(2)FFT ip数据输出方式:

(3)长度定义

5,仿真效果