ZYNQ--从入门到起飞--AXI总线接口分析(LITE)

在ZYNQ中有支持三种AXI总线,拥有三种AXI接口,当然用的都是AXI协议。其中三种AXI总线分别为:

AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输;

AXI4-Lite:(For simple, low-throughput memory-mapped communication )是 一个轻量级的地址映射单次传输接口,占用很少的逻辑单元。

AXI4-Stream:(For high-speed streaming data.)面向高速流数据传输;去掉了地址项,允许无限制的数据突发传输规模。

其中有很多相似的接口,我们以AX14-Lite为例,分析接口的作用与含义。

当我们(设计)customize一个AX14总线用户IP核时,会有两个模块,顶层模块与逻辑模块,下面我们以(slave)从机为例,分析逻辑模块的接口含义。

C_S_AXI_DATA_WIDTH表示数据总线的位宽

C_S_AXI_ADDR_WIDTH表示数据地址的位宽

input wire S_AXI_ACLK :表示总线时钟

input wire S_AXI_ARESETN:系统复位信号,低电平有效

input wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_AWADDR:写地址

input wire [2 : 0] S_AXI_AWPROT: 表明传输中数据和命令传输的安全级别和权限

input wire S_AXI_AWVALID:表明写地址和控制数据是否有效

output wire S_AXI_AWREADY:指示从设备准备好接收数据和控制信号

input wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_WDATA:写数据

input wire [(C_S_AXI_DATA_WIDTH/8)-1 : 0] S_AXI_WSTRB:写选通用于指示哪些字节通道传输有效数据几个字节对应几个选通信号bit

input wire S_AXI_WVALID:写有效,该信号写数据和写选通信号是有效的

output wire S_AXI_WREADY:写准备,该信号用于表示从机已经准备好,可以接受写入数据

output wire [1 : 0] S_AXI_BRESP:主机接口中的写入响应通道端口

output wire S_AXI_BVALID: 写入响应有效,用来指示写入响应通道正在传输有效数据input wire S_AXI_BREADY: 响应准备,用于表示主机已经准备好接收写入响应信号

input wire [C_S_AXI_ADDR_WIDTH-1 : 0] S_AXI_ARADDR: 主机接口读地址通道端口,由主机确定并发起读地址

input wire [2 : 0] S_AXI_ARPROT:无论是传输数据还是传输指令都将使用该管脚表明传输的权限和安全级别。

input wire S_AXI_ARVALID: 读地址有效,该信号用于表明通道正在发送有些的读地址数据和控制信息

output wire S_AXI_ARREADY: 读地址准备,该信号表明从机设备已经准备好,可以接收地址和相关控制信号

output wire [C_S_AXI_DATA_WIDTH-1 : 0] S_AXI_RDATA:主机接口读数据通道端口

output wire [1 : 0] S_AXI_RRESP: 读取响应,该信号用于指示读取操作的状态output wire S_AXI_RVALID: 读有效,该信号用于指示通道上正在传输需要的数据

input wire S_AXI_RREADY: 读取准备,该信号用来表示主机已经准备好接收从机响应的读取数据

);

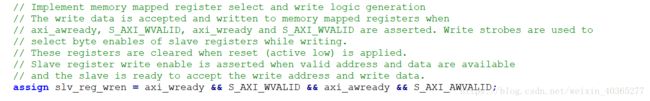

下面是逻辑模块中几个常用信号的意义:slv_reg_wren、slv_reg_rden、

一、

分析上述模块:可知:slv_reg_wren是写使能信号:表明在axi_ready与S_AXI_WVALID、axi_awready、S_AXI_AWVALID有效的时候、表明从机已经准备好接收写地址与写数据。

axi_awaddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB]:选择寄存器

slv_reg_rden是读使能信号:表明此时从机已经准备好接收读地址了

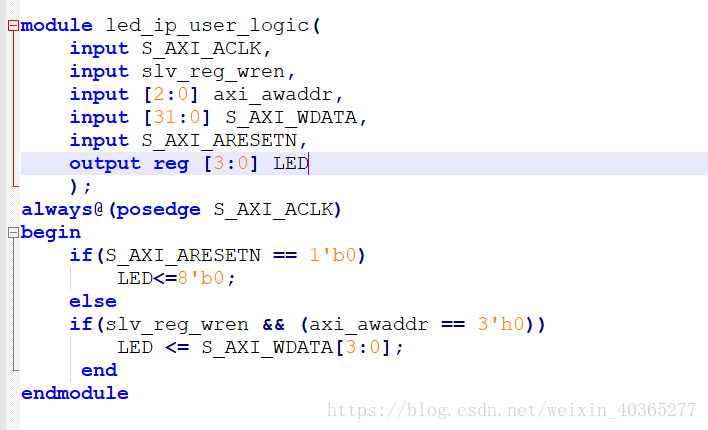

我们以定制LED流水灯AXI IP核为例,讲解一下几个接口的具体作用:

一、在逻辑模块的第399行用户逻辑下面例化一个led流水灯模块

二、我们单独写一个LED流水灯逻辑模块:

然后我们只需在SDK中写一个简单的控制LED流水灯模块就可以了