FPGA的基本组成结构

目前主流的FPGA芯片仍是基于查找表。FPGA芯片主要由以下6部分组成:

(1)可编程输入输出单元(IOB)

(2)基本可编程逻辑单元(CLB)

(3)完整的时钟管理模块

(4)丰富的布线资源

(5)嵌入式块RAM

(6)内嵌的底层功能单元和嵌入式专用硬核

通过配置以上6个不同的部分,基本可以让FPGA实现任何你想要实现的功能。

一、FPGA的结构解析

对于一款芯片,我们肉眼看到的如图1.1所示,看不出它有任何特点。

当我们对其内部放大时,看到如图1.2所示结构,密密麻麻小方格,仍然完全看不出有什么特点:

当我们再对其内部进行放大时,看到如图1.3所示结构,这时可以看到芯片内部的最基本组成单元:可编程逻辑单元、布线资源、可编程IO。对于复杂的芯片,内部还应包括时钟管理模块、嵌入式块RAM、内嵌的底层功能单元和嵌入式专用硬核,各基本单元在芯片内部的分布如图1.4所示。

考虑到芯片内部的连接情况,对于图1.4所示的芯片内部结构,可以简化为图1.5所示内部结构相互连接的情况,不同部分通过丰富的布线资源相连接,最终实现我们想要的功能。接下来我们来讨论每个基本组成部分。

二、基本组成部分内部结构及功能

2.1、可编程输入输出单元(IOB)

I/O模块包含两个IOB、两个ILOGIC、两个OLOGIC和两个IODELAY。图2.1所示为Virtex-5 I/O模块。

基本IOB图如图2.2所示,每个IOB包含输入、输出和三态SelectIO驱动器。差分I/O使用在一个模块中的两个IOB。图2.2中,红色线代表设置IO为output型时走线,绿色线代表设置IO为input型时走线,蓝色线代表设置IO为inout型时走线,T用来控制三态门,当其为0时,三态门导通,表示IO为输出类型,当为1时,三态门关闭,表示IO为输入类型。如inout data_o;

assign data_o = !T?data_o_2:'bZ;当T为0时,data_o被定义为输出类型;T为1时,data_o被定义为输入类型。

由图2.1可知,各IOB直接连接ILOGIC/OLOGIC对,该逻辑对包含输入和输出逻辑资源,可用于数据和IOB的三态控制。下面我们分别讨论ILOGIC和OLOGIC资源。

2.1.1 ILOGIC/OLOGIC资源

ILOGIC逻辑资源的模块图如图2.3所示:

ILOGIC资源可支持以下操作(这些资源之间的所有连接均由所编写代码控制):

- 边沿触发D型触发器

- 电平敏感性锁存器

- 异步/组合

- IDDR模式

OLOGIC由两个主要的模块组成,一个用于配置输出数据通路,另一个用于配置三态控制通路。二者共用时钟(CLK)。

OLOGIC逻辑资源的模块图如图2.4所示:

OLOGIC资源可支持以下操作(这些资源之间的所有连接均由所编写代码控制):

- 边沿触发D型触发器

- 电平敏感性锁存器

- 异步/组合

- ODDR模式

2.1.2 ILOGIC/OLOGIC中的寄存器资源

这里重点讨论一下在实际工程中如何使用ILOGIC/OLOGIC中的寄存器。在实际工程中,进行高速数据传输时,对于高速信号要通过连接ILOGIC/OLOGIC中的寄存器进行传输。即在设计中将要传输的信号输入或者输出都用寄存器同步一下,然后对该寄存器进行约束,使其使用ILOGIC/OLOGIC内部的寄存器,由于ILOGIC/OLOGIC距离引脚的路径固定,这样就可以保证数据从输入引脚进第一级寄存器的布线延迟相同/输出数据出最后一级寄存器到达引脚的布线延迟相同。

某博客上的解释如下:

如何使用ILOGIC/OLOGIC中的寄存器资源:

module beipin(input clk,

input data_in,

output data_o,

output clk_o

);

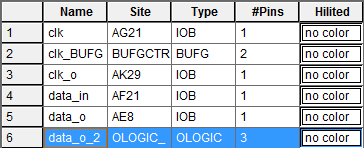

(*IOB = "TRUE"*)reg data_o_2; ///////使用IOB中的寄存器

always @(posedge clk)

data_o_2 <= data_in;

assign data_o =data_o_2;

endmodule对于上述代码,如果不对寄存器进行(*IOB=“TRUE”*)约束的话,编译后使用FPGA Editor查看,会发现寄存器使用的是Slice中的寄存器(当软件优化全关闭的情况下:在XST中打开属性,设置xilinxspecific options 的 -iob (Pack I/O registers into IOB) 属性为No,在ISE的implementation的MAP属性中设置 -pr(Pack I/O registers into IOB) 属性为“OFF”)。而如果进行约束的话,就会发现使用的是OLOGIC中的寄存器。

2.1.3 ILOGIC/OLOGIC中的IDDR/ODDR

对于ILOGIC/OLOGIC逻辑资源可以使用原语实现IDDR/ODDR

使用原语实现IDDR:

IDDR有以下三种工作方式:

- OPPOSITE_EDGE模式

- SAME_EDGE模式

- SAME_EDGE_PIPELINED模式

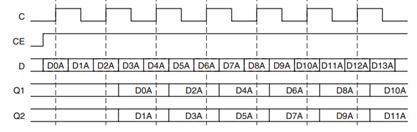

OPPOSITE_EDGE模式下的输入DDR时序:

我对IDDR的工作过程理解(OPPOSITE_EDGE模式下):数据Q1在时钟C的上升沿输出,数据Q2在时钟C的下降沿输出,即使用时钟C的上升沿和下降沿进行数据的接收。这样FPGA就可以以较小时钟进行数据的接收。如图2.6所示,C_2X为数据发送的时钟,C为通过IDDR进行接收的时钟。

SAME_EDGE模式下输入DDR时序:

在SAME_EDGE模式下:数据在时钟C的同一上升沿送至FPGA内部资源。一对数据之间有一个时钟周期的间隔。

SAME_EDGE_PIPELINED模式下输入DDR时序:

在SAME_EDGE_PIPELINED模式下:数据在时钟C的同一上升沿送至FPGA内部资源。与SAME_EDGE模式不同的是,一对数据之间没有一个时钟周期的间隔,但是需要增加一个时钟周期的延迟。

对于IDDR的功能:我的理解是它可以降低FPGA内部的工作时钟频率,且可以实现数据的串并转换(将串行的数据D转成并行的数据Q1、Q2)。

ODDR有以下两种工作方式:

- OPPOSITE_EDGE模式

- SAME_EDGE模式

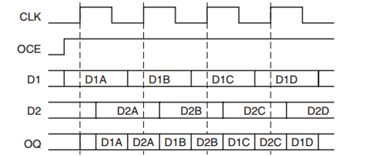

OPPOSITE_EDGE模式下的输出DDR时序:

对ODDR工作过程理解(OPPOSITE_EDGE模式下):数据D1和D2分别在时钟CLK的上升沿和下降沿送进ODDR,ODDR以两倍CLk的时钟速率将数据发送出去。如图2.10所示,在CLK的上升沿和下降沿分别将D1和D2加载进ODDR,在CLK_2X的上升沿将数据送出。CLK是采集数据时钟,CLK_2X是数据发送时钟。使用ODDR也实现了FPGA内部以较小的时钟实现了较快的数据传输。

SAME_EDGE模式下的输出DDR时序:

SAME_EDGE模式下,数据在CLk的同一上升沿送进ODDR,然后在CLK_2X的上升沿将数据送出。

对于ODDR的功能:我的理解是它的作用也是降低FPGA内部工作时钟的频率,并且可以实现数据的串并转换(将并行数据D1、D2转为串行OQ)。

2.1.4 ILOGIC/OLOGIC中的ISERDES/OSERDES资源

ISERDES输入串并转换器

ISERDES是专用的串并转换器,其功能包括:

- 专用解串器/串并转换器

- Bitslip子模块(使能后就是一个桶装移位寄存器)

- 对选通存储器接口的专门支持

- 对网络接口的专门支持

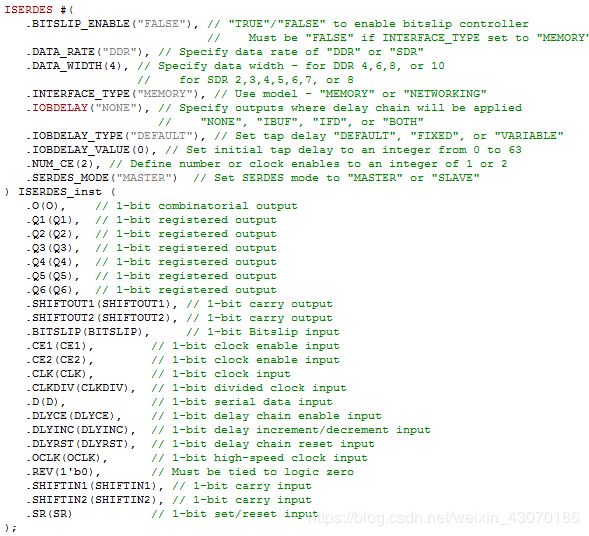

ISERDES实现是通过原语实现(这里仅讨论串并转换功能):

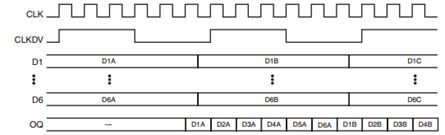

图2.12所示为8:1SDR ISERDES的ISERDES时序图。由于ISERDES的性质,数据需要多个CLKDIV周期才能出现。(先进去的在低位)

由图可知,串行数据D在CLK的上升沿送进ISERDES,在CLKDIV时钟的上升沿(SDR)将数据转换为并行的送出。CLK与CLKDIV的关系取决于串并转换比。如:要实现8:1(8个串行数据转换为1个并行数据)的串并数据转换,CLKDIV就是CLK的8分频。其关系如下表所示:

表1 数据串并转换器的CLK/CLKDIV关系

OSERDES输出并串转换器:

输出并串转换器的实现也是通过原语实现,

一个OSERDES模块中的数据并串转换器接收来自内部资源的二到六位并行数据,将数据串行化,然后通过OQ输出将数据送至IOB。并行数据串行化是按照从数据输入引脚的最低位到最高位的顺序进行的(即低位先输出)。

SDR6:1 OSERDES时序:

在SDR模式下,并行数据D1…D6在时钟CLKDV的上升沿送入并串转换器,在CLK的上升沿将数据送出,CLKDIV与CLK的关系取决于并串转换比。

DDR6:1 OSERDES时序:

在DDR模式下,并行数据D1…D6在CLK的上升沿将数据送进并串转换器,在CLKDIV的上升沿和下降沿将数据送出,CLKDIV与CLK的关系取决于并串转换比/2。

数据并串准换器的CLK/CLKDIV关系如下表所示:

表2 数据并串转换器CLK/CLKDIV关系

3.1基本可编程单元(CLB)

可配置逻辑块(CLB)是实现时序电路和组合电路的主要逻辑资源。每个CLB元件连接到一个可访问通用布线矩阵的开关矩阵(如图2.15所示)。每个CLB元件包含一对Slice。这两个Slice之间没有直接连接,各Slice组成一个列。列中的Slice具有独立的进位链。

Xilinx工具用以下定义表示Slice。“X”后跟一个数字表示各Slice在对中的位置以及该Slice的列位置。“Y”后跟一个数字表示CLB的行。在一个CLB内此数字保持不变,从底部起向上一次计数CLB行。如图2.16所示。

3.11 Slice描述

每个Slice包含四个逻辑函数发生器(即查找表)、四个存储元件、多功能多路复用器和进位逻辑。所有Slice都通过这些元件进行逻辑、算术和ROM函数运算。除此之外,有些Slice还支持两个附加功能:用分布式RAM存储数据和用32位寄存器进行数据移位。支持这些附加功能的Slice称为SLICEM;其它称为SLICEL。

由图2.17和图2.18可知,SLICEL和SLICEM的区别是SLICEL中的逻辑函数发生器只能配置成LUT和ROM;而SLICEM中的逻辑函数发生器不仅可以配置成LUT和ROM,还可以配置成RAM(其中Distribute RAM就是由SLICEM中的逻辑函数发生器配置而成)。

每个CLB可以包含0个或1个SLICEM。每隔一个CLB列包含一个SLICEM。另外,DSP48E左边的两个CLB列各包含一个SLICEL和一个SLICEM。

一个CLB中的逻辑资源:

| Slice |

LUT |

触发器 |

算术和进位链 |

分布式RAM(SLICEM) |

移位寄存器(SLICEM) |

| 2 |

8 |

8 |

2 |

256位 |

128位 |

分布式RAM和存储器(只能在SLICEM中使用)

可以使用各种方法将SLICEM中的多个LUT组合起来,以存储较大量数据。

4.1 时钟资源

为时钟控制之目的,每个V5器件分成若干个时钟区域(8—24个区域),区域数因器件大小而异。xc5vlx50-1ff1153被分成12个时钟区域。

4.1.1全局时钟

每个V5器件有32条全局时钟线,它们可以对整个器件上的所有顺序资源(CLB、BRAM、CMT和IO)进行时钟控制,并且还可以驱动逻辑信号。可以将这32条时钟线中的任何10条用于任意区域。一条全局时钟线仅由一个全局时钟缓冲器驱动,该全局时钟缓冲器还可以用作时钟使能电路或无毛刺信号的多路复用器。它可以在两个时钟源之间进行选择,还可以切离其中一个失效的时钟源。

全局时钟是一种专用互联网络,是专为覆盖对FPGA中各种资源的所有时钟输入设计的。这些时钟网络的设计旨在降低歪斜、占空比失真和功耗。其设计的目的还在于支持甚高频信号。

全局时钟控制资源和网络通常由以下通路和组件构成:

- 全局时钟输入

- 全局时钟缓冲器

- 时钟树和时钟网络-GCLK

- 时钟区域

全局时钟输入(IBUFG、IBUFGDS)

通过使用IBUFG(单端IO的输入时钟缓冲器)、IBUFGDS(差分IO的输入时钟缓冲器)将输入时钟接入全局时钟网络。

全局时钟缓冲器(BUFGCTRL)

每个V5器件有32个全局时钟缓冲器(与全局时钟线个数一致)。一个全局时钟的输入可以从差分输入引脚对的P端直接连接到器件中任意全局时钟缓冲器的输入。每个差分全局时钟引脚可以连接到PCB上的一个差分或单端时钟。如果使用单端时钟,则必须使用引脚的P端,因为只有这一引脚上存在直接连接。如果单端时钟连接到差分引脚对的P端,则不能用其N端作为另一个单端时钟引脚。不过可以作为普通IO。

全局时钟缓冲器允许各种时钟源/信号源接入全局时钟树和网络。可以输入全局时钟缓冲器的源包括:

- 全局时钟输入

- 时钟管理模块输出(DCM、PLL)

- 其它全局时钟缓冲器输入

- 通用互连

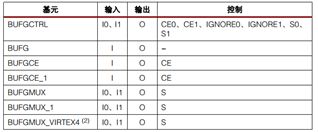

全局时钟缓冲器基元如下表所示:

这些基元均可以通过原语实现。

FPGA内部最基本的基元是BUFGCTRL,其它基元都是由BUFGCTRL配置而成。BUFGCTRL如图2.20所示:

4.1.2 区域时钟

区域时钟每区域有2个区域时钟缓冲器BUFR和4个区域时钟树。区域时钟网络是一组独立于全局时钟网络的时钟网络。与全局时钟不同,区域时钟信号(BUFR)的跨度限于三个时钟区域,而IO时钟信号只驱动一个区域。

4.13 IO时钟

第三种时钟资源是IO时钟,可以达到非常高的速度,可用于局部的IO串行器/解串器。

对于IO时钟实现是通过BUFIO的原语实现,目前没有用过IO时钟,对此不是很了解。

5.1对于FPGA内部的其它资源(布线资源、嵌入式BRAM、嵌入式专用硬核DSP)等使用其它比较直观,这里不在讨论。