计算机系统结构实验-模型机的组成

前言:

这次的模型机实验和上学期做的CPU本质上可以说是一样的,但是这一学期做的更加精致、完美,并且在实验板上的验证结果也完全正确。也学到了许多的新的东西,算是收获不小了。

今年的模型机是以小组为单位做的,在此也感谢我们组各组员的付出。(多些人力量还是大些哈哈),此文也是在实验报告的基础上半修半该而成的。

总线数据传输

一、实验题目

总线数据传输

二、基本知识点

1) 总线数据传输原理。

2) 芯片74374和74244的逻辑功能。

3) 寄存器之间数据交换的方法。

三、目的要求

1) 了解课程安排(实验项目设置、计组实验特点、分模块要求、总要求、测试等)。

2) 复习 实验教材 “第3章 数字逻辑”中FPGA设计开发的实验方法。

3) 了解总线数据的传输原理。

4) 了解芯片74374和74244的逻辑功能。

5) 理解寄存器之间数据交换的方法。

四、实验设备

1) PC一台

2) DDA系列数字系统实验平台

3) Quartus Ⅱ 配套软件。

五、实验内容

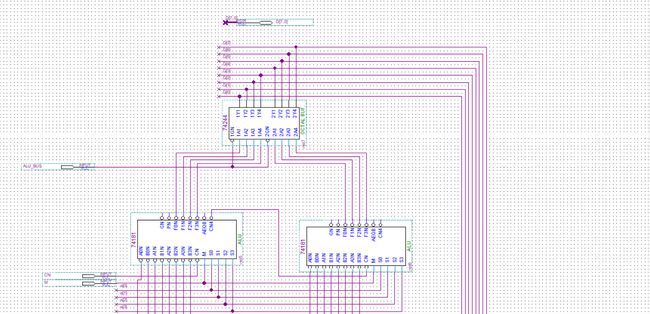

1) 根据实验原理图完成电路图设计(代码或者绘制电路图)。

![]()

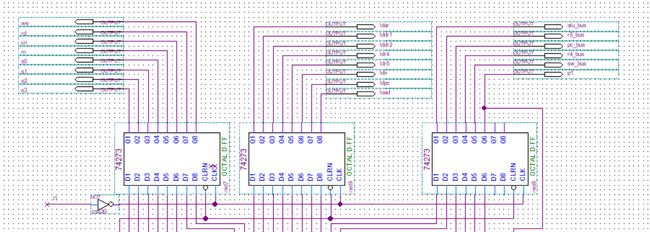

BUS是宽度为8位的总线,可经[7..0]二进制数据开关输入数据,通过L[7..0]双向数据端口显示总线数据;R1~R3是3片8位寄存器,但是实际的结构图中这里没有 使用 LE显示R3的数据,而是通过将R3的数据输出到总线上来查看R3的数据。

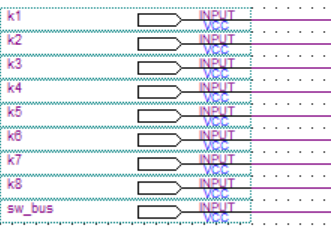

a) 输入输出元件:用于数据的输入与输出。

b) 1个74244元件:输入数据的寄存器。

c) 3个74374元件作为寄存器:各个数据的寄存器。

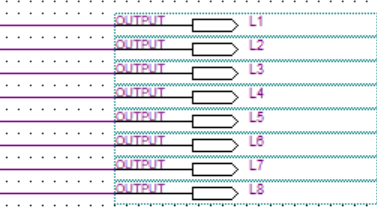

d) 总图

2) 波形仿真验证。

a) 将数据E1H写入R1。

b) 将R1中数据写入R3,并查看R3中的数据。

c) 将数据D2H写入R2,再将R2的数据写入R1。

d) 将R3的数据写入R2。

e) 分别查看R1与R2的内容,验证是否交换成功。

根据实验框图,设计总线电路,记录实验数据并完成功能仿真(R1与R2互换,即4.1.4 (3)③即可)。完成下载,体会计组的实验方法和总线特性(总线特性贯穿 整个实验)。

六、实验数据及分析

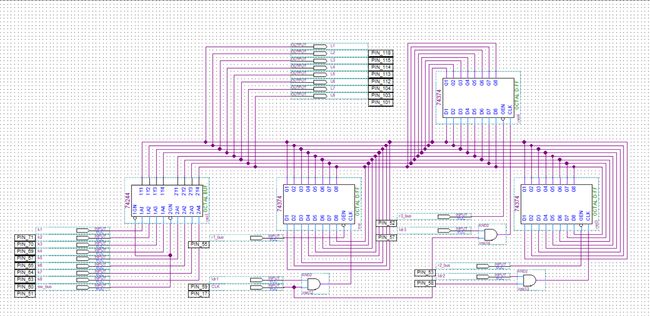

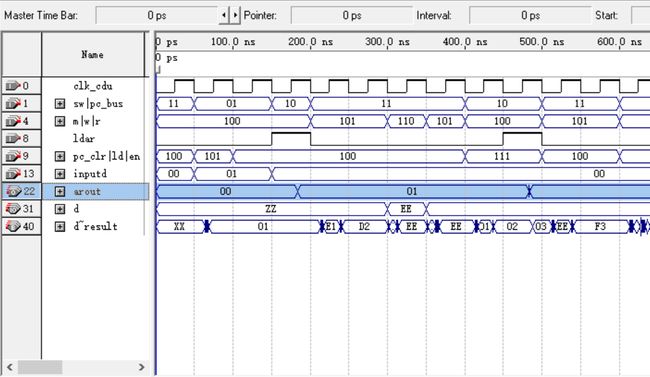

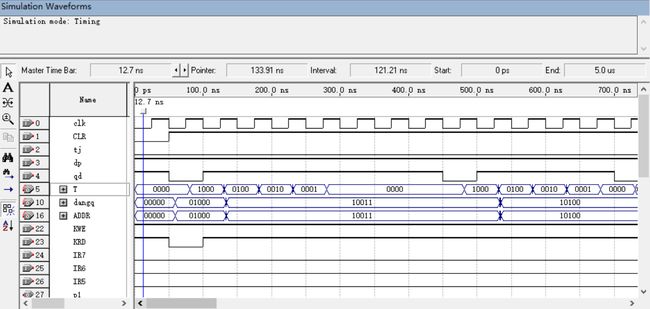

1) 时序仿真结果

2) 数据分析

a) 第一个时钟周期:bus_123_sw=1111,LD123=000,数据初始值K为00,总线输出为高阻态;

b) 第二个时钟周期:设置K=E1,bus_123_sw=1110,LD123=100,将数据E1传至总线,通过L[7..0]显示总线数据,数据E1存入R1;

c) 第三个时钟周期:bus_123_sw =0111,LD123=001,R1中的数据写入总线并存入R3,总线输出数据E1;

d) 第四个时钟周期:bus_123_sw =1101,LD123=000,R3中的数据写入总线,此时R3输出E1;

e) 第五个时钟周期:设置数据k[7..0]=D2,bus_123_sw =1110,LD123=010,将数据D1传至总线并存入R2;

f) 第六个时钟周期:bus_123_sw =1011,LD123=100,R2中的数据写入总线并存入R1,总线输出数据D1 ;

g) 第七个时钟周期:bus_123_sw =1101,LD123=010,R3中的数据写入R2,此时R3输出E1,总线输出E1。

h) 第八个时钟周期:bus_123_sw =0111,LD123=000,查看R1的内容,总线输出为D1。

i) 第八个时钟周期:bus_123_sw=1011,LD123=000,查看R2的内容,总线输出为E1。

j) 至此R1与R2的数据交换完毕。

运算器

一、 实验题目

运算器设计

二、 基本知识点

1) 运算器的组成结构及工作原理。

2) 简单运算器的数据通路与控制信号的关系。

3) 数据算术运算及逻辑运算方法。

三、目的要求

1) 了解:运算器实验概述。

2) 掌握简单ALU的exp_s_alu.vhd代码及运算结果(A=05H、B=0AH、式子见4.2.4 )。

3) 完成复合运算的仿真验证 A 加 B 减((notA)and B)加B。

四、实验设备

1) PC一台

2) DDA系列数字系统实验平台

3) Quartus Ⅱ 配套软件。

五、实验内容及步骤

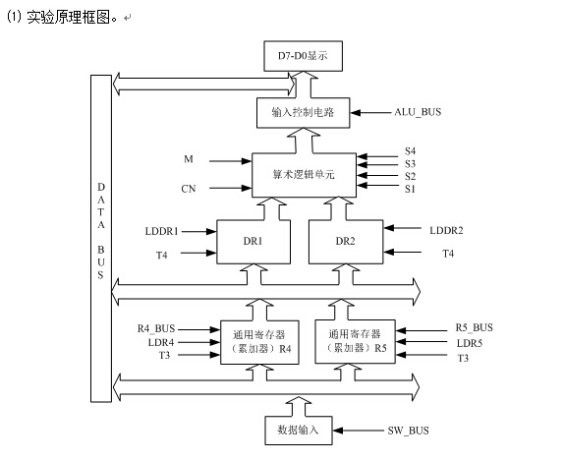

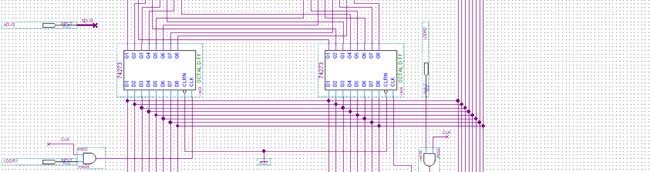

1) 实验原理框图

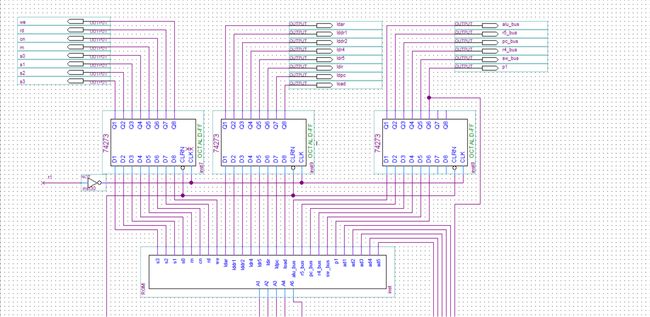

基本部分为算术逻辑运算单元、通用寄存器组、输入数据选择电路、输出数据控制电路。

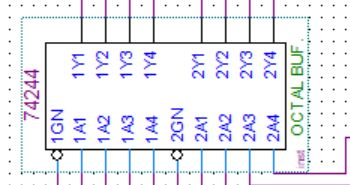

2) 元器件的使用:

a)1个74244元件:输入数据的寄存器。

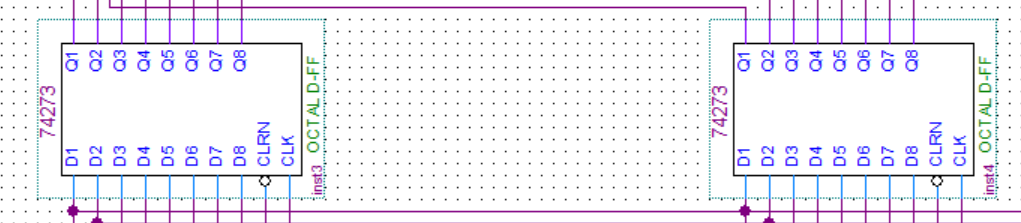

b)两个74374:两个数据的寄存器:

c)两个74274:两个操作数的暂存器:

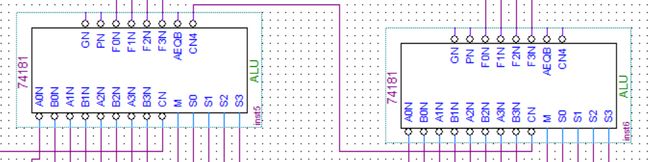

d)两个74181级联得到一个8位的运算器:

e)ALU的三态缓冲输出避免总线数据冲突:

f)总图:

六、实验数据及分析

1)时序仿真结果

2) 数据分析

a) 第一个时钟周期:SW|R4|R5|ALU_BUS=1111,LD_R1|R2|R4|R5=0000,数据初始值K为00,总线没有数据,输出为高阻态;

b) 第二个时钟周期:设置k=05,SW|R4|R5|ALU_BUS =0111,LD_R1|R2|R4|R5=1000,此时SW_BUS打开,将数据05传至总线,同时LDR1打开,将总线上的 数据传至DR1,此时总线上数据为05;

c) 第三个时钟周期:设置k=0A,SW|R4|R5|ALU_BUS =0111,LD_R1|R2|R4|R5=0100,此时SW_BUS打开,将数据0A传至总线,同时LDR2打开,将总线上的 数据传至DR2,此时总线上数据为0A;

d) 第四个时钟周期:设置k=00,SW|R4|R5|ALU_BUS =1110,LD_R1|R2|R4|R5=0010,M|CN=01,S=1001,此时运算器进行(dr1加dr2)操作,处理结果为 0F,并且ALU_BUS打开,将数据0F传至总线,同时LDR4打开,将总线上的数据传至R4,此时总线上数据为0F;

e) 第五个时钟周期:保持k=00,SW|R4|R5|ALU_BUS =1110,LD_R1|R2|R4|R5=0001,M|CN=10,s=0010,此时运算器进行(/DR1·DR2)操作,处理结果为 0A,并且ALU_BUS打开,将数据0A传至总线,同时LDR5打开,将总线上的数据传至R5,此时总线上数据为0A;

f) 第六个时钟周期:保持k=00,SW|R4|R5|ALU_BUS =1011,LD_R1|R2|R4|R5=0010,M|CN=00,s=0000,此时R4_BUS打开,将R4的数据0F传至总线,并 且LDR1打开,将总线数据0F传至DR1,此时总线上数据为0F;

g) 第七个时钟周期:保持k=00,SW|R4|R5|ALU_BUS =1110,LD_R1|R2|R4|R5=0010,M|CN=01,s=1001,此时运算器进行(DR1加DR2)操作,处理结果 为19,并且ALU_BUS打开,将数据19传至总线,同时ld_r4打开,将总线上的数据传至R4,此时总线上数据为19;

h) 第八个时钟周期:保持k=00,SW|R4|R5|ALU_BUS =1011,LD_R1|R2|R4|R5=1000,M|CN=00,s=0000,此时R4_BUS打开,将R4的数据19传至总线,并 且LDR1打开,将总线数据19传至DR1,此时总线上数据为19;

i) 第九个时钟周期:保持k=00,SW|R4|R5|ALU_BUS =1101,LD_R1|R2|R4|R5=0100,M|CN=00,s=0000,此时R5_BUS打开,将R5的数据0A传至总线,并 且LDR2打开,将总线数据0A传至DR2,此时总线上数据为0A;

j) 第十个时钟周期:保持k=00,SW|R4|R5|ALU_BUS =1110,LD_R1|R2|R4|R5=0000,M|CN=00,s=0110,此时运算器进行(DR1减DR2)操作,处理结果为 0F,并且ALU_BUS打开,将数据0F传至总线,此时总线上数据为0F;

存储器

一、实验题目

存储器设计

二、基本知识点

1) 随机存储器RAM的工作特性及使用方法。

2) RAM数据存储和读取的工作原理。

3) LPM存储类元件定制。

三、目的要求

1) 了解存储器实验概述。

2) 了解4.3.4 1.RAM的exp_ram.vhd代码及读写操作。

3) LPM_RAM_IO定制存储器实验。参考图4-3-12用电路图完成设计,或通路部分用语言描述,存储部分用定制,再用图形完成最后设计,如图4-3-13,完成以下仿 真:置数法产生一个地址,存数,读数;计数法产生地址、存数、读数。

4) 完成课后思考题。

四、实验设备

1) PC一台

2) DDA系列数字系统实验平台

3) Quartus Ⅱ 配套软件。

五、实验内容及步骤

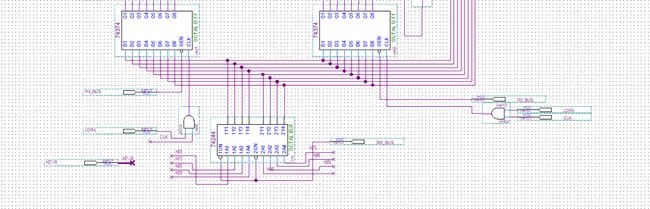

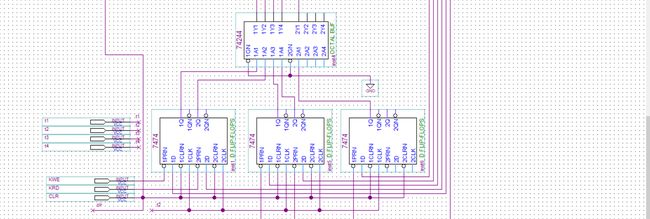

1) 存储器实验原理框图

地址寄存器AR,存放即将访问的存储单元地址。两组单光二极管显示灯中一组显示存储单元地址;另一组显示写入存储单元的数据或从存储单元读出的数据。写 入存 储器的数据是由二进制开关设置并发送至总线上的。

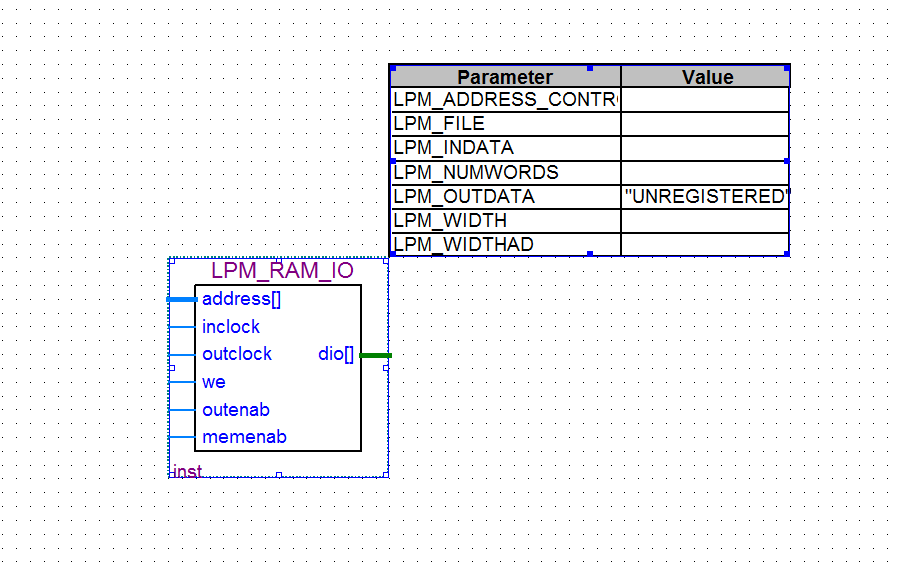

2) LPM_RAM_IO定制实验

利用LPM_RAM_IO设置参数定制一片256*8位RAM。

a) 在图形编辑界面调用元件,选择路Libraries→megafanctions→storage→lpm_ram_io。

b) 进行相关参数设置。

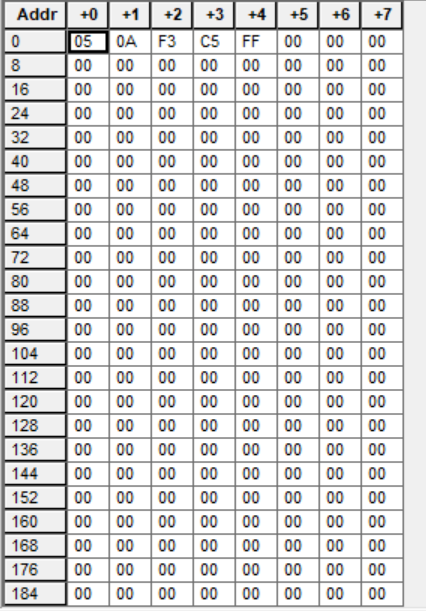

c) 新建.mif文件并进行初始值设置。

d) 完成芯片设置及引脚设置。

e) 完成RAM数据读写波形仿真验证。

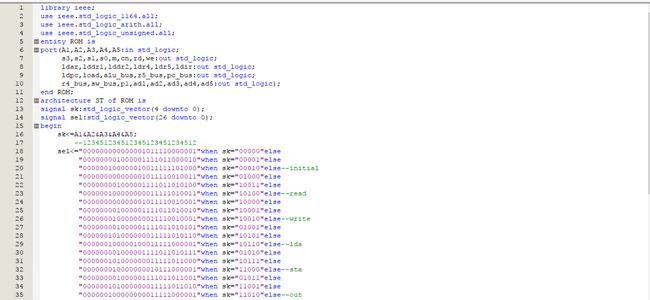

3) 存储器实验

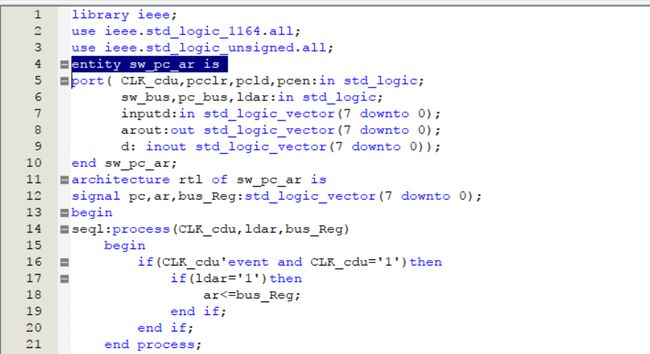

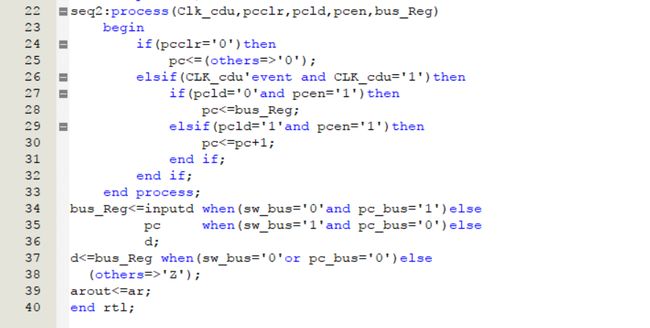

a) 8位存储器的数据通路部分sw_pc_ar.vhd代码。

生成打包得到图形文件:

![]()

b) 利用Lpm_ram_io设计8位存储器,连接电路图。

六、实验数据及分析

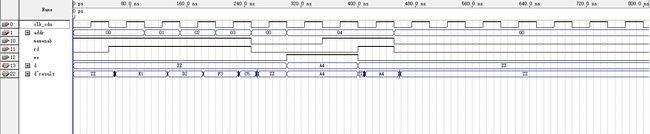

1) 时序仿真结果

2) 数据分析

a) 第一个时钟周期:sw|pc_bus =11,m|w|r=100,ldar=0,pc_clr|ld|en=100,input=00,此时为初始状态,总线输出为高阻态;

b) 第二个时钟周期:sw|pc_bus =01,m|w|r=100,ldar=0,pc_clr|ld|en=101,input=01,此时sw_bus打开,input值01写进总线,并且通过总线传进pc,总线输 出为 01;

c) 第三个时钟周期:sw|pc_bus =01,m|w|r=100,ldar=0,pc_clr|ld|en=100,input=01,此时等待pc稳定,总线输出为01;

d) 第四个时钟周期:sw|pc_bus =10,m|w|r=100,ldar=1,pc_clr|ld|en=100,input=00,此时pc_bus、ldar打开,pc中地址01传至总线,并通过总线传至地址 寄存器ar,总线输出为01;

e) 第五个时钟周期:sw|pc_bus =11,m|w|r=101,ldar=0,pc_clr|ld|en=100,input=00,此时rd打开,由于延时效应,总线先输出E1后输出地址01对应的D2;

f) 此后周期同上述分析。

数据通路

一、实验题目

数据通路

二、基本知识点

1) 数据通路中运算器与存储器协调工作的原理。

2) 数据及地址在数据通路上传输方法。

三、目的要求

1) 了解:数据通路概述。

2) 【实验】*4.4.4数据通路实验:参考图4-4-2完成运算器与存储器的整合(RAM初始为零)如图4-4-3,完成实验内容:设计实验步骤,记录波形仿真图,完成仿真 说明(4点,功能说明用表格形式完成)。

3) mif内存初始化实现A=05H→【00】, B=0AH→【02】

计算 (A加B)减【(/ A)and B )】加B

A 加B → 【03】置

(/ A)and B )→ R4

【03】加B → R5

R5减R4

四、实验设备

1) PC一台

2) DDA系列数字系统实验平台

3) Quartus Ⅱ 配套软件。

五、实验内容及步骤

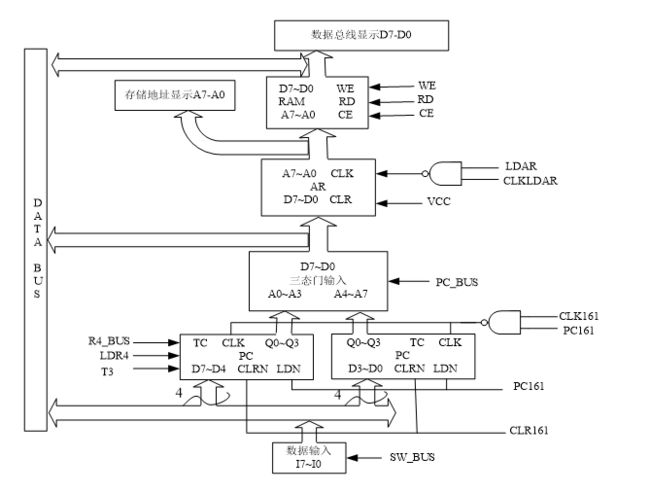

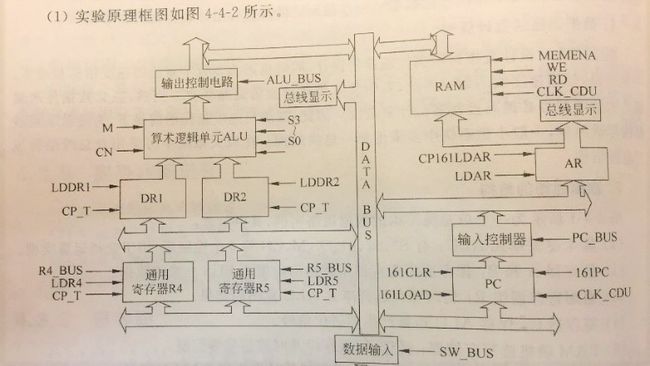

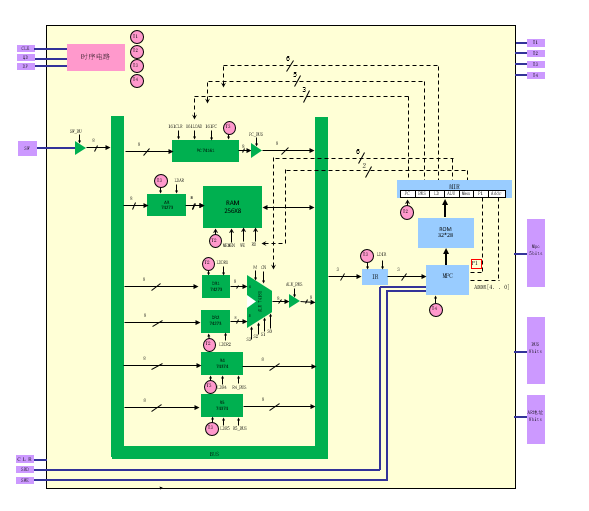

1) 实验原理框图

写入RAM的数据由运算器提供。RAM读出的数据可以到达运算器的暂存工作寄存器保存。

教材版:

自画版:

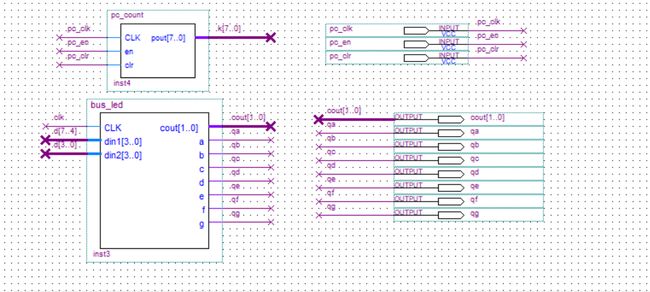

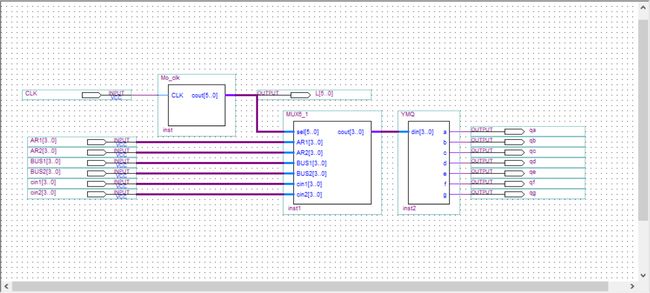

2) 根据实验原理图,利用运算器exp_r_alu与存储器RAM源设计文件连接成数据通路。

由于电路板子的输入按键不够,我们加入了计数器用于K的数入。

3) 设置LPM_RAM_IO的内存初始文件initial_file.mif。

4) 实验步骤记录

六、实验数据及分析

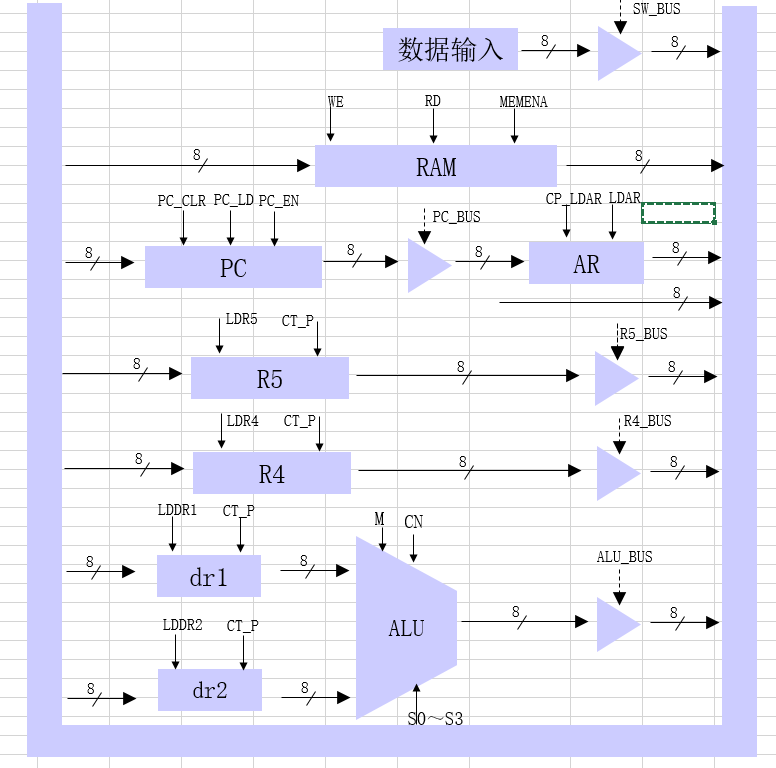

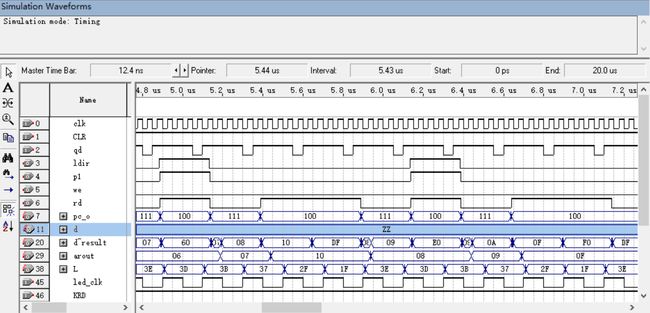

1) 时序仿真结果(部分)

2) 数据分析(部分)

a) 第一个时钟周期:bus_sel=11111,ld_reg=00000,pc_sel=100,we_rd=00,这时为初始状态,总线上没有数据,输出为高阻态;

b) 第二个时钟周期:bus_sel=11110,ld_reg=00001,pc_sel=100,we_rd=00,这时pc_bus打开,总线上输出数据为pc地址00,并通过总线传至地址寄存器 ar;

c) 第三个时钟周期:bus_sel=11111,ld_reg=00001,pc_sel=100,we_rd=01,这时rd打开,RAM通过ar地址00读出【00】的数据05;

d) 第四个时钟周期:bus_sel=11111,ld_reg=10000,pc_sel=100,we_rd=01,这时daar1打开,05通过总线传至dar1;

e) 第五、六个时钟周期:bus_sel=11110,ld_reg=00001,pc_sel=111,we_rd=00,这时pc自增加到02,pc_bus打开,地址传至总线;

f) 第七个时钟周期:bus_sel=11110,ld_reg=00001,pc_sel=100,we_rd=00,这时ldar打开,地址通过总线传至地址寄存器ar;

g) 第八个时钟周期:bus_sel=11111,ld_reg=00001,pc_sel=100,we_rd=01,这时rd打开,RAM通过ar地址02读出【02】的数据0A;

h) 第九个时钟周期:bus_sel=11111,ld_reg=01000,pc_sel=100,we_rd=01,这时daar2打开,05通过总线传至dar2;

由于后面的情况十分复杂,就不以仿真验证了,直接下载到电路板上进行验证

时序电路:

一、实验问题:

时序电路设计

二、基本知识点:

时序电路即时序信号产生器,最基本组成部分包括时钟脉冲源、环形脉冲发生器、节拍脉冲和读写时序译码逻辑、启停控制逻辑。

三、目的要求:

设计合理的时序电路,使模型机的各个模块能流程地配合运作。

四、实验设备:

1) PC一台;

2) DDA系统数字系统实验平台;

3) QuartusII 配套软件。

五、实验内容及步骤:

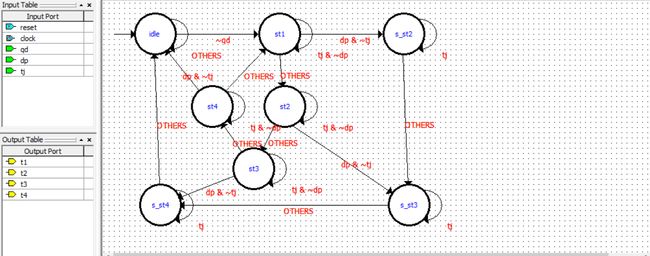

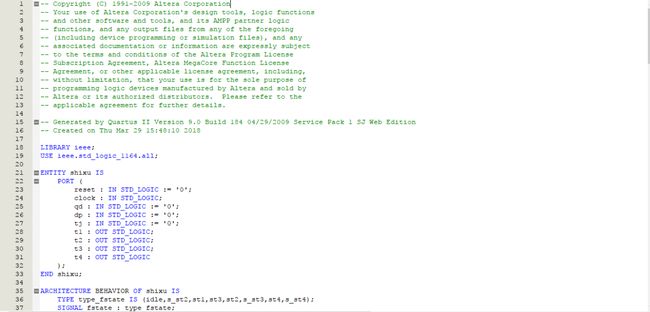

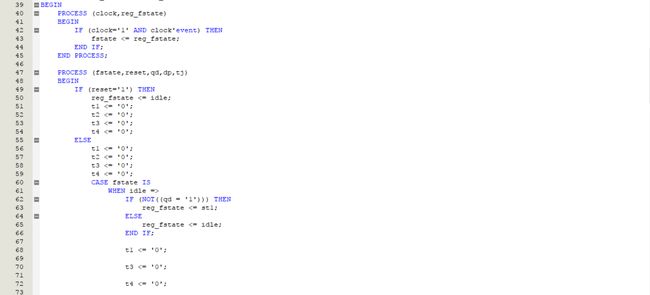

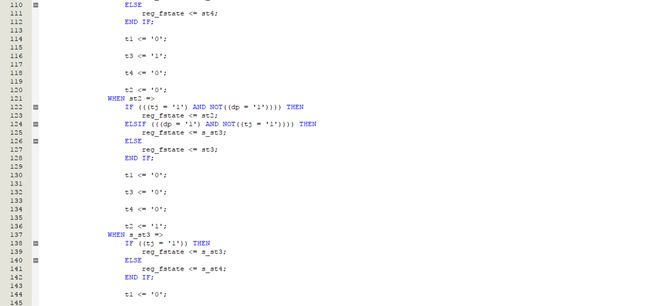

1)根据实验原理图完成电路图设计(这里设计状态图,如下):

2)通过工具Generate HDLFile 生成VHDL文件并设置成顶层。

六、实验数据及分析:

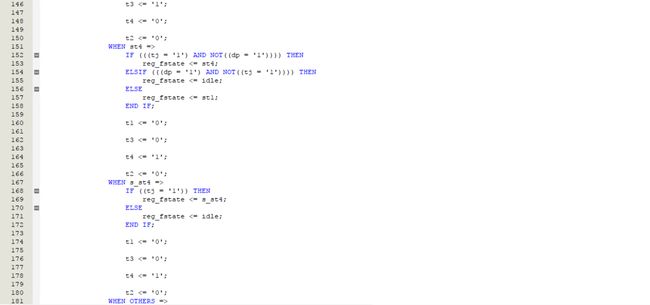

1)波形仿真验证

2)数据分析:

A. 当QD由1→0→1脉冲,节拍器启动,开始进行t1→t2→t3→t4。

B. 当TJ=1时,节拍器停机,保持当前状态不变。

C. 当DP=1,TJ=0,将QD由1→0→1脉冲,机器处于单步运行状态。

微程序控制器

一、实验题目:

微程序控制器

二、基本知识点:

1)微程序控制器的组成和工作原理。

2)微程序、微指令、微命令之间的关系。

3)微指令,微程序的设计及调试。

三、目的要求:

1)了解控制器的运作机制及其作用。

2)合理设计rom使其能正确地发出各条指令中数据通路需要的控制信号。

四、实验设备:

1)PC一台。

2)DDA系列数字系统实验平台

3)Quartus II 配套软件及简单CPU模拟器。

五、实验内容及步骤:

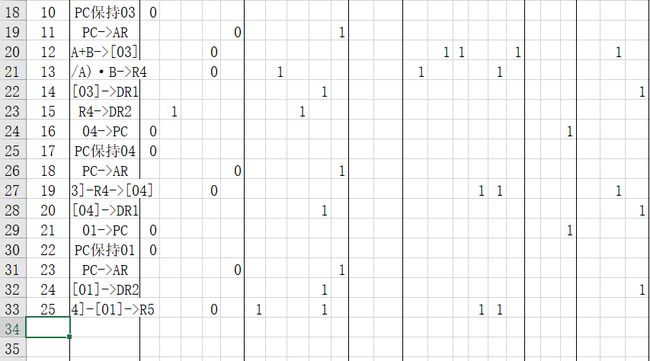

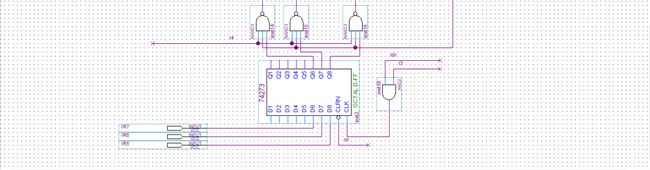

1)需要实现的各条指令框图:

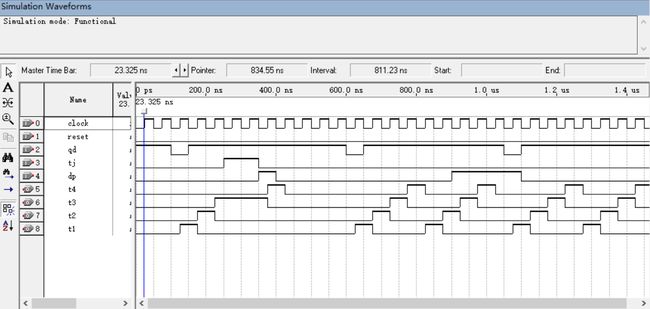

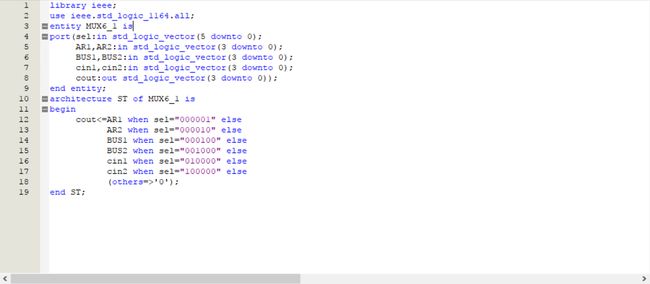

2)所有指令均写在rom中,VHDL代码如下:

3)控制器的下址产生逻辑:

4)控制信号的寄存器:

5)配合上述的时序电路综合可以得到总的控制器总图:

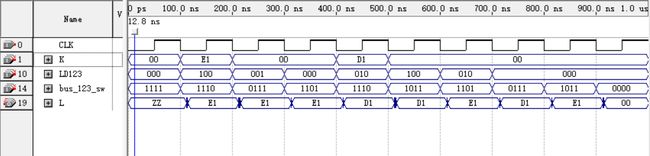

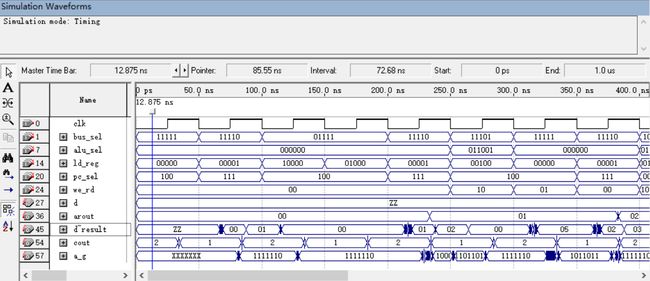

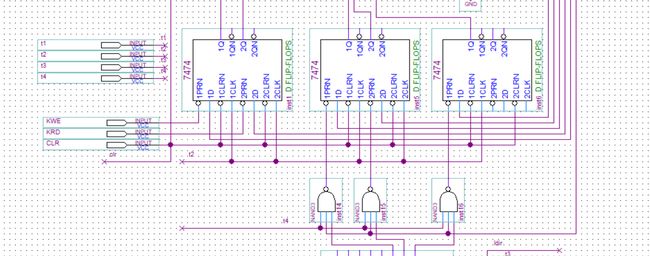

6)波形仿真验证:

(这里主要验证下址的产生是否正确)

![]()

由仿真结果可知:下址的变化与要求的框图中的变化一致,其余的控制信号在模型机整合的时候再予以分析。

模型机组成与程序运行

一、实验题目

模型机组成与程序运行

二、基本知识点

1)计算机的组成和工作原理。

2)计算机执行机器指令的工作过程。

3)微指令、微程序的设计及调试

三、目的要求

1)了解:实验概述4.7.3。

2)#讲解:模型机实验_Newbook.ppt。

3)实验】* 4.7.4实验内容(1),(2)或(3):完成模型机电路,用模拟器学会编写测试程序,仿真及下载验证流程图4-6-4。详见,模型机实验_Newbook.ppt。

四、实验设备

1)PC一台

2)DDA系列数字系统实验平台

3)Quartus Ⅱ 配套软件。

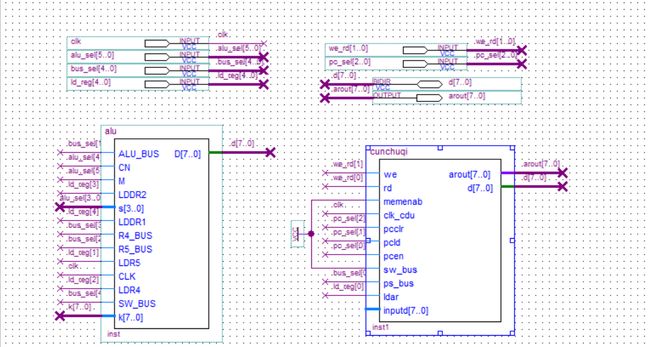

五、实验内容及步骤:

1)实验概述

依据微体系结构图通过各个子模块整合设计模型机,由模型机主体、时序电路、显示模块组成。

2)微体系结构图

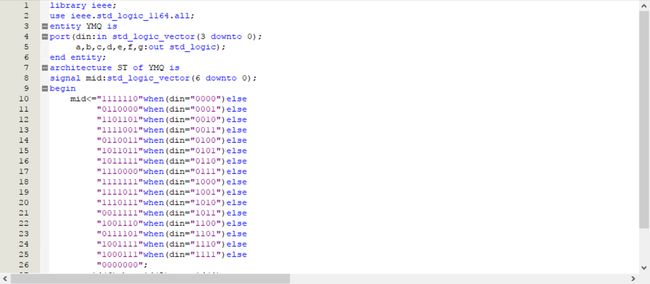

3)设计数码管显示电路

Ⅰ)段选信号:

Ⅱ)数据选择输出:

Ⅲ)7段译码器:

Ⅳ)总图:

4)由上述各个子模块以及显示模块综合连接整合位最终地模型机模块:

总图如下:

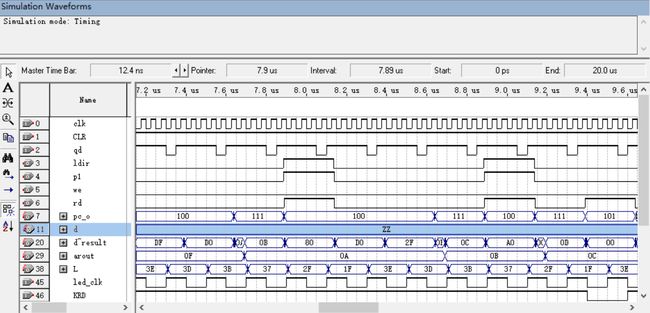

5)进行波形仿真验证:

6)数据分析:

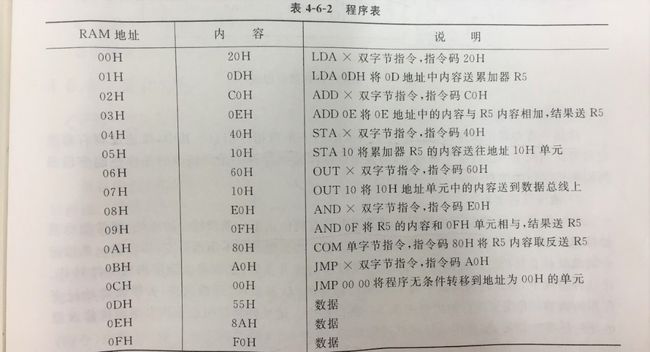

(1)程序表:

(2)LDA指令的数据分析:

| mpcout (2进制) |

bus_data (16进制) |

arout (16进制) |

操作 |

结果 |

| 00000 |

00 |

00 |

sw_in→pc sw_in→bus_reg |

pc=0 bus_reg=00 |

| 00001 |

00 |

00 |

pc→ar pc→pc+1 pc→bus_reg |

ar=00 pc=01 bus_reg=00 |

| 00010 |

00 |

00 |

ram【00】→ir 通过【00】取出20 20→bus-reg |

ir=001 mpc_t4=01001 bus_reg=20 |

| 01001 |

20 |

00→01 |

pc→ar pc→pc+1 pc→bus_reg |

ar=01 pc=02 bus_reg=01 |

| 10101 |

01 |

01 →0D |

ram【01】→ar 通过【01】取出0D 0D→bus_rag |

ar=0D bus_reg=0D |

| 10110 |

OD |

0D |

ram→r5 通过ar取出数据55 |

ar=0D pc=02 bus_reg=55 |

(2)ADD指令的数据分析:

| mpcout (2进制) |

bus_data (16进制) |

arout (16进制) |

操作 |

结果 |

| 00001 |

55 |

0D→02 |

pc→ar pc→pc+1 pc→bus_reg |

ar=02 pc=03 bus_reg=02 |

| 00010 |

02 |

02 |

ram【02】→ir ram中取出C0 C0→bus-reg |

ir=001 mpc_t4=01001 bus_reg=C0 |

| 01110 |

C0 |

02→03 |

pc→ar pc→pc+1 pc→bus_reg |

ar=03 pc=04 bus_reg=03 |

| 00011 |

03 |

03→0E |

ram【03】→ar 通过【03】取出 0E→bus_rag |

ar=0E pc=04 bus_reg=0E |

| 00100 |

0E |

0E |

ram【0E】→dr2 通过【0E】取出 8A→bus_rag |

ar=0E bus_reg=8A |

| 00101 |

8A |

0E |

r5→dr1 r5→bus_reg |

dr1=55 bus_reg=55 |

| 00110 |

55 |

0E |

dr1+dr2→r5 dr1+dr2→bus_reg |

r5=DF bus_reg=DF ar=0E |

(3)STA指令的数据分析:

| mpcout (2进制) |

bus_data (16进制) |

arout (16进制) |

操作 |

结果 |

| 00001 |

DF |

0E→04 |

pc→ar pc→pc+1 pc→bus_reg |

ar=04 pc=05 bus_reg=04 |

| 00010 |

04 |

04 |

ram【04】→ir ram中取出40 40→bus-reg |

ir=010 mpc_t4=01010 bus_reg=40 |

| 01010 |

40 |

04→05 |

pc→ar pc→pc+1 pc→bus_reg |

ar=05 pc=06 bus_reg=05 |

| 10111 |

05 |

05→10 |

ram【05】→ar 通过【05】取出 10→bus_rag |

ar=10 pc=06 bus_reg=10 |

| 11000 |

10 |

10 |

r5→ram【10】 r5→bus_reg |

ram【10】=DF bus_reg=DF pc=06 |

(4)OUT指令的数据分析:

| mpcout (2进制) |

bus_data (16进制) |

arout (16进制) |

操作 |

结果 |

| 00001 |

DF |

10→06 |

pc→ar pc→pc+1 pc→bus_reg |

ar=06 pc=07 bus_reg=06 |

| 00010 |

06 |

06 |

ram【06】→ir ram中取出60 60→bus-reg |

ir=011 mpc_t4=01011 bus_reg=60 |

| 01011 |

60 |

06→07 |

pc→ar pc→pc+1 pc→bus_reg |

ar=07 pc=08 bus_reg=07 |

| 11001 |

07 |

07→10 |

ram【07】→ar 通过【07】取出 10→bus_rag |

ar=10 pc=08 bus_reg=10 |

| 11010 |

10 |

10 |

ram【10】→dr2 通过【10】取出 DF→bus_reg |

ar=10 bus_reg=DF |

(5)AND指令的数据分析:

| mpcout (2进制) |

bus_data (16进制) |

arout (16进制) |

操作 |

结果 |

| 00001 |

DF |

10→08 |

pc→ar pc→pc+1 pc→bus_reg |

ar=08 pc=09 bus_reg=08 |

| 00010 |

08 |

08 |

ram【08】→ir ram中取出E0 E0→bus-reg |

ir=111 mpc_t4=01111 bus_reg=E0 |

| 01111 |

E0 |

08→09 |

pc→ar pc→pc+1 pc→bus_reg |

ar=09 pc=0A bus_reg=09 |

| 11101 |

09 |

09→0F |

ram【09】→ar 通过【09】取出 0F→bus_rag |

ar=0F pc=0A bus_reg=0F |

| 11110 |

0F |

0F |

ram【0F】→dr2 通过【0F】取出 F0→bus_rag |

ar=0F bus_reg=F0 dr2=F0 |

| 11111 |

F0 |

0F |

r5→dr1 r5→bus_reg |

dr1=DF bus_reg=DF |

| 00111 |

DF |

0F |

dr1 and dr2→r5 dr1 and dr2→bus_reg |

r5=D0 bus_reg=D0 ar=0F |

(6)COM指令的数据分析:

| mpcout (2进制) |

bus_data (16进制) |

arout (16进制) |

操作 |

结果 |

| 00001 |

D0 |

0F→0A |

pc→ar pc→pc+1 pc→bus_reg |

ar=0A pc=0B bus_reg=0A |

| 00010 |

0A |

0A |

ram【0A】→ir ram中取出80 80→bus-reg |

ir=100 mpc_t4=01100 bus_reg=80 |

| 01100 |

80 |

0A |

r5→dr1 r5→bus_reg |

dr1=D0 bus_reg=D0 |

| 11011 |

D0 |

0A |

not dr1→r5 not dr1→bus_reg |

r5=2F bus_reg=2F ar=0A |

(7)JMP指令的数据分析:

| mpcout (2进制) |

bus_data (16进制) |

arout (16进制) |

操作 |

结果 |

| 00001 |

2F |

0A→0B |

pc→ar pc→pc+1 pc→bus_reg |

ar=0B pc=0C bus_reg=0B |

| 00010 |

0B |

0B |

ram【0B】→ir ram中取出A0 A0→bus-reg |

ir=101 mpc_t4=01101 bus_reg=A0 |

| 01101 |

A0 |

0B→0C |

pc→ar pc→pc+1 pc→bus_reg |

ar=0C pc=0D bus_reg=0C |

| 11100 |

0C |

0C |

ram【0C】→pc ram中取出00 00→bus-reg |

mpc_t4=00001 bus_reg=00 ar=0C pc=00 |

模型机运行至9.6us时,PC的地址跳回00,书中给定的运算表达式已运算结束。

7)下载到电路板进行试验

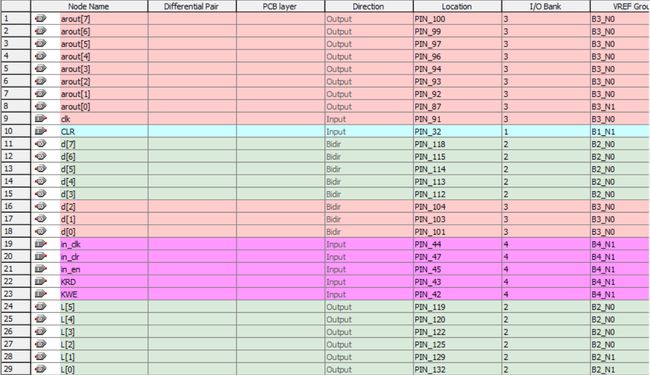

(1)引脚分配图:

(2)本来还想给出实验板上验证的结果图的,考虑到上述部分完成后,在实验板上操作就水到渠成了,这里贴图的实际意义也不大,没有再放实验板的图了。

额外说明:

该模型机的mif中储存的只是一条课本中特点表达式的程序,如要执行其他的逻辑或者算术运算,应该根据每一步需要的操作来重写mif文件中的数据。

最后依旧给出整个模型机文件,留作纪念。