Xilinx ISE中DDR3 IP核的使用(1)

ISE 中mig IP的调用与仿真环境的搭建

- 项目简介简述

- MIG IP建立的步骤

- MIG自带示例工程的搭建

- MIG 仿真环境的搭建

- 仿真结果

- 结束语

项目简介简述

Xilinx的MIG IP核是官方给出的DDR驱动,是一个FPGA工程师由入门更近一步必学的一个IP,因为FPGA本身的优势就是吞吐量特别大,而这一定伴随着内存的操作。Xlinx的软件版本主要有ISE与vivado两个软件,两个软件MIG的使用方法又不一样,接下来,我们将分别介绍两种软件MIG IP的使用。本篇文章,我们主要讲解以下内容:

1、使用ISE软件建立一个MIG IP核

2、建立一个MIG IP完整的仿真环境,以便于我们接下来的调试

MIG IP建立的步骤

熟悉我博客的同学应该知道,我对一些软件的使用都没有过多的介绍,只是给出了时序图与代码供大家自己理解,但是由于MIG IP比较复杂,这里我们给出详细的MIG调用流程。

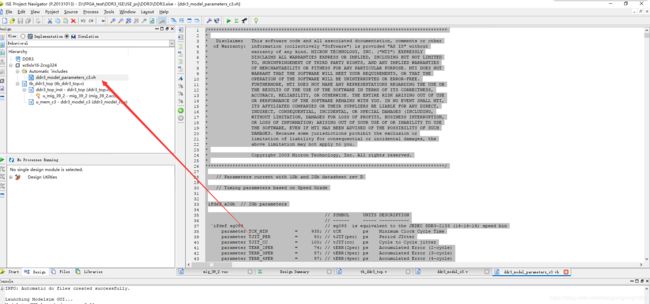

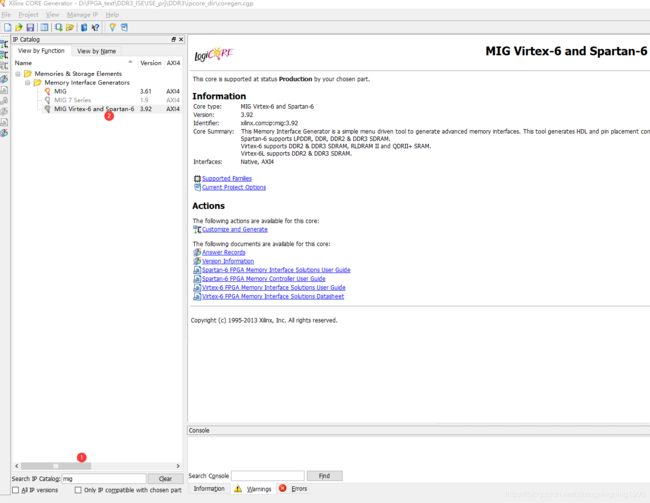

1、首先在1处输入MIG

2、双击标号2的MIG IP核

1、首先对比以下1处的设置信息,防止出错

2、点击2出的Next

1、其中上面1为建立一个新的MIG IP核,2为官方开发板的选择,3为更改一个已存在的MIG IP,在本次实验中我们选择1建立一个新的MIG IP核

2、点击4Next,进行下一步

1、其中1中的选项勾选了代表我们的这个IP不光只对该型号有用,也适用于选中的型号

2、这里我们不勾选1中的选项,直接点击2Next

1、其中1为使能AXI接口,该接口在7系列的非常常见,在这里我们不选择,AXI协议我们之后也会有文章来讲解,2会扩展外设的使用范围,我们这里不需要,也不选择,3是说明该FPGA芯片中两个bank中含有MCB硬件,我们查看具体的FPGA硬件板卡DDR连接在哪个bank,这里我们选择了bank3。

2、在3出下拉选择DDR3 SDRAM,然后点击Next

1、其中1有两个含义,一个是DDR3硬件的时钟频率,另一个是MIG的输入参考频率,2是对应的DDR3硬件的型号

2、在选择对应的型号之后,点击Next

1、这里1、2是与硬件的电阻情况有关,正常情况下默认即可

2、3为使能自动刷新操作,不需要我们再个MIG相应的刷新命令,这里选择使能该操作,点击Next

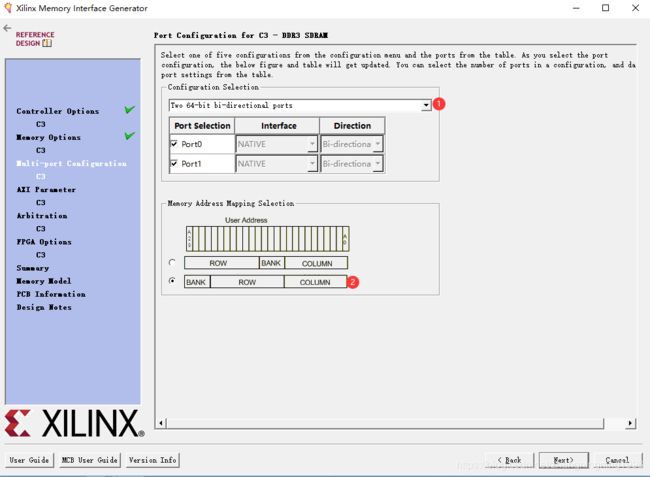

1、这里1是ISE比vivado中好的地方,就是说可以选择多通道模式,但是vivado中不可以,需要自己编写相应的程序,这里我们选择双通道可读可写64位模式,并且打上对号

2、2是MIG地址对应到DDR硬件地址中的顺序,这里选择第二个,然后点击Next

1、这里是两个通道同时有读写指令的情况下的先执行哪一个通道的顺序问题,这里我们使用默认的Round策略即可,然后点击Next。

1、其中1位硬件电路中的DDR与FPGA相连的电阻管脚,与2、3对应,然后查看开发板硬件手册找到RZQ、ZTQ两个引脚与FPGA连接的管脚,并且写在对应的2、3上面

2、4使能代表给添加了一些测试文件供我们调试,我们这里不使能,想调试我们自己添加ila进行调试

3、5是时钟的形式,这里选择单端即可

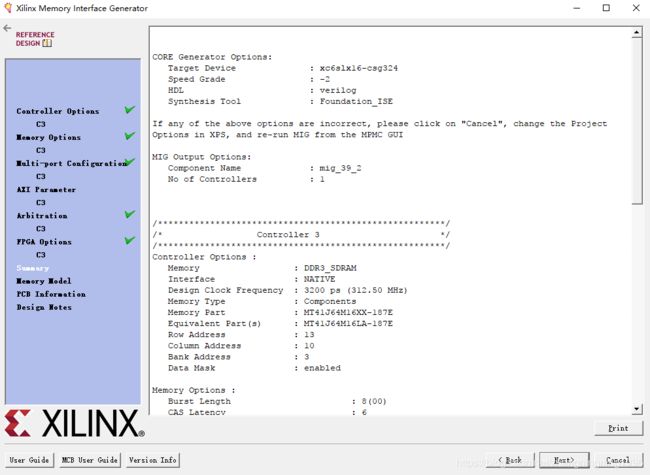

1、上面是选中的总结,点击Next

1、选择接受该协议,然后点击Next

然后一路Next,最后生成MIG IP核即可。到此为止,我们建立了一个完整新的MIG IP,并且知道了MIG IP核调用过程中每个选项所代表的意义。

MIG自带示例工程的搭建

我们班接下来要对该我们的MIG IP核搭建仿真环境,为了掌握仿真环境的搭建,我们先对MIG生成的示例工程进行搭建,然后再搭建我们的MIG仿真环境,因为其中的代码都是借鉴的示例工程中的代码,这里我们也给出了学习一个新的IP的完整流程。

首先找到相应的示例工程所存储的文件,如下:

1、这里ISE与VIVADO不同,这个示例工程需要我们自己建立,这里新建一个工程,将上述的文件添加进去。

2、注意要添加的文件都在sim与rtl(里面的文件全部加入)中,如下图:

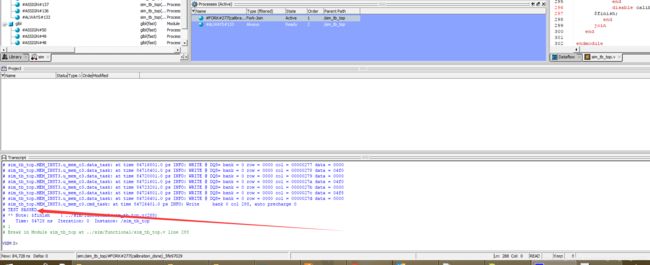

然后进行Modelsim仿真,这里既然做到了DDR应该就都熟悉了,不再多说。仿真的结果如下:

仿真出现上面两种界面,说明了我们示例工程的仿真环境搭建成功,接下来我们将利用这个示例工程搭建我们的MIG IP核的工程,里面具体很多代码都是参考的该示例工程。

MIG 仿真环境的搭建

这里我们将给出代码,大家可以对比一下代码与上面示例工程的代码,在仿真模型的处理上几乎一样。

这里注意一点为了加快仿真速度,将上面的C3_SIMULATION改成TURE,

ddr3_top模块:

`timescale 1ns / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : ddr3_top.v

// Create Time : 2020-02-21 22:56:59

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module ddr3_top(

// DDR3 Interfaces

inout [15:0] mcb3_dram_dq ,

output wire [12:0] mcb3_dram_a ,

output wire [02:0] mcb3_dram_ba ,

output wire mcb3_dram_ras_n ,

output wire mcb3_dram_cas_n ,

output wire mcb3_dram_we_n ,

output wire mcb3_dram_odt ,

output wire mcb3_dram_reset_n ,

output wire mcb3_dram_cke ,

output wire mcb3_dram_dm ,

inout mcb3_dram_udqs ,

inout mcb3_dram_udqs_n ,

inout mcb3_rzq ,

inout mcb3_zio ,

output wire mcb3_dram_udm ,

input c3_sys_clk ,

input c3_sys_rst_i ,

inout mcb3_dram_dqs ,

inout mcb3_dram_dqs_n ,

output wire mcb3_dram_ck ,

output wire mcb3_dram_ck_n

);

//========================================================================================\

//**************Define Parameter and Internal Signals**********************************

//========================================================================================/

//========================================================================================\

//************** Main Code **********************************

//========================================================================================/

mig_39_2 # (

.C3_P0_MASK_SIZE (8 ),

.C3_P0_DATA_PORT_SIZE (64 ),

.C3_P1_MASK_SIZE (8 ),

.C3_P1_DATA_PORT_SIZE (64 ),

.DEBUG_EN (0 ),

.C3_MEMCLK_PERIOD (3200 ),

.C3_CALIB_SOFT_IP ("TRUE" ),

.C3_SIMULATION ("TURE" ),

.C3_RST_ACT_LOW (0 ),

.C3_INPUT_CLK_TYPE ("SINGLE_ENDED" ),

.C3_MEM_ADDR_ORDER ("BANK_ROW_COLUMN" ),

.C3_NUM_DQ_PINS (16 ),

.C3_MEM_ADDR_WIDTH (13 ),

.C3_MEM_BANKADDR_WIDTH (3 )

)

u_mig_39_2 (

.c3_sys_clk (c3_sys_clk ),

.c3_sys_rst_i (c3_sys_rst_i ),

.mcb3_dram_dq (mcb3_dram_dq ),

.mcb3_dram_a (mcb3_dram_a ),

.mcb3_dram_ba (mcb3_dram_ba ),

.mcb3_dram_ras_n (mcb3_dram_ras_n ),

.mcb3_dram_cas_n (mcb3_dram_cas_n ),

.mcb3_dram_we_n (mcb3_dram_we_n ),

.mcb3_dram_odt (mcb3_dram_odt ),

.mcb3_dram_cke (mcb3_dram_cke ),

.mcb3_dram_ck (mcb3_dram_ck ),

.mcb3_dram_ck_n (mcb3_dram_ck_n ),

.mcb3_dram_dqs (mcb3_dram_dqs ),

.mcb3_dram_dqs_n (mcb3_dram_dqs_n ),

.mcb3_dram_udqs (mcb3_dram_udqs ), // for X16 parts

.mcb3_dram_udqs_n (mcb3_dram_udqs_n ), // for X16 parts

.mcb3_dram_udm (mcb3_dram_udm ), // for X16 parts

.mcb3_dram_dm (mcb3_dram_dm ),

.mcb3_dram_reset_n (mcb3_dram_reset_n ),

.mcb3_rzq (mcb3_rzq ),

.mcb3_zio (mcb3_zio ),

.c3_clk0 (c3_clk0 ),

.c3_rst0 (c3_rst0 ),

.c3_calib_done (c3_calib_done ),

.c3_p0_cmd_clk (c3_p0_cmd_clk ),

.c3_p0_cmd_en (c3_p0_cmd_en ),

.c3_p0_cmd_instr (c3_p0_cmd_instr ),

.c3_p0_cmd_bl (c3_p0_cmd_bl ),

.c3_p0_cmd_byte_addr (c3_p0_cmd_byte_addr ),

.c3_p0_cmd_empty (c3_p0_cmd_empty ),

.c3_p0_cmd_full (c3_p0_cmd_full ),

.c3_p0_wr_clk (c3_p0_wr_clk ),

.c3_p0_wr_en (c3_p0_wr_en ),

.c3_p0_wr_mask (c3_p0_wr_mask ),

.c3_p0_wr_data (c3_p0_wr_data ),

.c3_p0_wr_full (c3_p0_wr_full ),

.c3_p0_wr_empty (c3_p0_wr_empty ),

.c3_p0_wr_count (c3_p0_wr_count ),

.c3_p0_wr_underrun (c3_p0_wr_underrun ),

.c3_p0_wr_error (c3_p0_wr_error ),

.c3_p0_rd_clk (c3_p0_rd_clk ),

.c3_p0_rd_en (c3_p0_rd_en ),

.c3_p0_rd_data (c3_p0_rd_data ),

.c3_p0_rd_full (c3_p0_rd_full ),

.c3_p0_rd_empty (c3_p0_rd_empty ),

.c3_p0_rd_count (c3_p0_rd_count ),

.c3_p0_rd_overflow (c3_p0_rd_overflow ),

.c3_p0_rd_error (c3_p0_rd_error ),

.c3_p1_cmd_clk (c3_p1_cmd_clk ),

.c3_p1_cmd_en (c3_p1_cmd_en ),

.c3_p1_cmd_instr (c3_p1_cmd_instr ),

.c3_p1_cmd_bl (c3_p1_cmd_bl ),

.c3_p1_cmd_byte_addr (c3_p1_cmd_byte_addr ),

.c3_p1_cmd_empty (c3_p1_cmd_empty ),

.c3_p1_cmd_full (c3_p1_cmd_full ),

.c3_p1_wr_clk (c3_p1_wr_clk ),

.c3_p1_wr_en (c3_p1_wr_en ),

.c3_p1_wr_mask (c3_p1_wr_mask ),

.c3_p1_wr_data (c3_p1_wr_data ),

.c3_p1_wr_full (c3_p1_wr_full ),

.c3_p1_wr_empty (c3_p1_wr_empty ),

.c3_p1_wr_count (c3_p1_wr_count ),

.c3_p1_wr_underrun (c3_p1_wr_underrun ),

.c3_p1_wr_error (c3_p1_wr_error ),

.c3_p1_rd_clk (c3_p1_rd_clk ),

.c3_p1_rd_en (c3_p1_rd_en ),

.c3_p1_rd_data (c3_p1_rd_data ),

.c3_p1_rd_full (c3_p1_rd_full ),

.c3_p1_rd_empty (c3_p1_rd_empty ),

.c3_p1_rd_count (c3_p1_rd_count ),

.c3_p1_rd_overflow (c3_p1_rd_overflow ),

.c3_p1_rd_error (c3_p1_rd_error )

);

endmodule

tb_ddr3_top模块:

`timescale 1ps / 1ps

// *********************************************************************************

// Project Name : OSXXXX

// Author : zhangningning

// Email : [email protected]

// Website :

// Module Name : tb_ddr3_top.v

// Create Time : 2020-02-21 23:21:37

// Editor : sublime text3, tab size (4)

// CopyRight(c) : All Rights Reserved

//

// *********************************************************************************

// Modification History:

// Date By Version Change Description

// -----------------------------------------------------------------------

// XXXX zhangningning 1.0 Original

//

// *********************************************************************************

module tb_ddr3_top;

parameter C3_MEMCLK_PERIOD = 3200 ;

wire [12:0] mcb3_dram_a ;

wire [02:0] mcb3_dram_ba ;

wire mcb3_dram_ck ;

wire mcb3_dram_ck_n ;

wire [15:0] mcb3_dram_dq ;

wire mcb3_dram_dqs ;

wire mcb3_dram_dqs_n ;

wire mcb3_dram_dm ;

wire mcb3_dram_ras_n ;

wire mcb3_dram_cas_n ;

wire mcb3_dram_we_n ;

wire mcb3_dram_cke ;

wire mcb3_dram_odt ;

wire mcb3_dram_reset_n ;

wire mcb3_dram_udqs ; // for X16 parts

wire mcb3_dram_udqs_n ; // for X16 parts

wire mcb3_dram_udm ; // for X16 parts

wire mcb3_rzq ;

wire mcb3_zio ;

reg c3_sys_clk ;

reg c3_sys_rst_i ;

initial c3_sys_clk = 1'b0;

always #(C3_MEMCLK_PERIOD/2) c3_sys_clk = ~c3_sys_clk;

initial begin

c3_sys_rst_i <= 1'b1;

#(100*C3_MEMCLK_PERIOD);

c3_sys_rst_i <= 1'b0;

end

PULLDOWN zio_pulldown3 (.O(mcb3_zio) );

PULLDOWN rzq_pulldown3 (.O(mcb3_rzq) );

ddr3_top ddr3_top_inst(

// DDR3 Interfaces

.mcb3_dram_dq (mcb3_dram_dq ),

.mcb3_dram_a (mcb3_dram_a ),

.mcb3_dram_ba (mcb3_dram_ba ),

.mcb3_dram_ras_n (mcb3_dram_ras_n ),

.mcb3_dram_cas_n (mcb3_dram_cas_n ),

.mcb3_dram_we_n (mcb3_dram_we_n ),

.mcb3_dram_odt (mcb3_dram_odt ),

.mcb3_dram_reset_n (mcb3_dram_reset_n ),

.mcb3_dram_cke (mcb3_dram_cke ),

.mcb3_dram_dm (mcb3_dram_dm ),

.mcb3_dram_udqs (mcb3_dram_udqs ),

.mcb3_dram_udqs_n (mcb3_dram_udqs_n ),

.mcb3_rzq (mcb3_rzq ),

.mcb3_zio (mcb3_zio ),

.mcb3_dram_udm (mcb3_dram_udm ),

.c3_sys_clk (c3_sys_clk ),

.c3_sys_rst_i (c3_sys_rst_i ),

.mcb3_dram_dqs (mcb3_dram_dqs ),

.mcb3_dram_dqs_n (mcb3_dram_dqs_n ),

.mcb3_dram_ck (mcb3_dram_ck ),

.mcb3_dram_ck_n (mcb3_dram_ck_n )

);

ddr3_model_c3 u_mem_c3(

.ck (mcb3_dram_ck ),

.ck_n (mcb3_dram_ck_n ),

.cke (mcb3_dram_cke ),

.cs_n (1'b0 ),

.ras_n (mcb3_dram_ras_n ),

.cas_n (mcb3_dram_cas_n ),

.we_n (mcb3_dram_we_n ),

.dm_tdqs ({mcb3_dram_udm,mcb3_dram_dm}),

.ba (mcb3_dram_ba ),

.addr (mcb3_dram_a ),

.dq (mcb3_dram_dq ),

.dqs ({mcb3_dram_udqs,mcb3_dram_dqs}),

.dqs_n ({mcb3_dram_udqs_n,mcb3_dram_dqs_n}),

.tdqs_n ( ),

.odt (mcb3_dram_odt ),

.rst_n (mcb3_dram_reset_n )

);

endmodule

仿真模型文件:

/****************************************************************************************

*

* File Name: ddr3.v

* Version: 1.61

* Model: BUS Functional

*

* Dependencies: ddr3_model_parameters_c3.vh

*

* Description: Micron SDRAM DDR3 (Double Data Rate 3)

*

* Limitation: - doesn't check for average refresh timings

* - positive ck and ck_n edges are used to form internal clock

* - positive dqs and dqs_n edges are used to latch data

* - test mode is not modeled

* - Duty Cycle Corrector is not modeled

* - Temperature Compensated Self Refresh is not modeled

* - DLL off mode is not modeled.

*

* Note: - Set simulator resolution to "ps" accuracy

* - Set DEBUG = 0 to disable $display messages

*

* Disclaimer This software code and all associated documentation, comments or other

* of Warranty: information (collectively "Software") is provided "AS IS" without

* warranty of any kind. MICRON TECHNOLOGY, INC. ("MTI") EXPRESSLY

* DISCLAIMS ALL WARRANTIES EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED

* TO, NONINFRINGEMENT OF THIRD PARTY RIGHTS, AND ANY IMPLIED WARRANTIES

* OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. MTI DOES NOT

* WARRANT THAT THE SOFTWARE WILL MEET YOUR REQUIREMENTS, OR THAT THE

* OPERATION OF THE SOFTWARE WILL BE UNINTERRUPTED OR ERROR-FREE.

* FURTHERMORE, MTI DOES NOT MAKE ANY REPRESENTATIONS REGARDING THE USE OR

* THE RESULTS OF THE USE OF THE SOFTWARE IN TERMS OF ITS CORRECTNESS,

* ACCURACY, RELIABILITY, OR OTHERWISE. THE ENTIRE RISK ARISING OUT OF USE

* OR PERFORMANCE OF THE SOFTWARE REMAINS WITH YOU. IN NO EVENT SHALL MTI,

* ITS AFFILIATED COMPANIES OR THEIR SUPPLIERS BE LIABLE FOR ANY DIRECT,

* INDIRECT, CONSEQUENTIAL, INCIDENTAL, OR SPECIAL DAMAGES (INCLUDING,

* WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION,

* OR LOSS OF INFORMATION) ARISING OUT OF YOUR USE OF OR INABILITY TO USE

* THE SOFTWARE, EVEN IF MTI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH

* DAMAGES. Because some jurisdictions prohibit the exclusion or

* limitation of liability for consequential or incidental damages, the

* above limitation may not apply to you.

*

* Copyright 2003 Micron Technology, Inc. All rights reserved.

*

* Rev Author Date Changes

* ---------------------------------------------------------------------------------------

* 0.41 JMK 05/12/06 Removed auto-precharge to power down error check.

* 0.42 JMK 08/25/06 Created internal clock using ck and ck_n.

* TDQS can only be enabled in EMR for x8 configurations.

* CAS latency is checked vs frequency when DLL locks.

* Improved checking of DQS during writes.

* Added true BL4 operation.

* 0.43 JMK 08/14/06 Added checking for setting reserved bits in Mode Registers.

* Added ODTS Readout.

* Replaced tZQCL with tZQinit and tZQoper

* Fixed tWRPDEN and tWRAPDEN during BC4MRS and BL4MRS.

* Added tRFC checking for Refresh to Power-Down Re-Entry.

* Added tXPDLL checking for Power-Down Exit to Refresh to Power-Down Entry

* Added Clock Frequency Change during Precharge Power-Down.

* Added -125x speed grades.

* Fixed tRCD checking during Write.

* 1.00 JMK 05/11/07 Initial release

* 1.10 JMK 06/26/07 Fixed ODTH8 check during BLOTF

* Removed temp sensor readout from MPR

* Updated initialization sequence

* Updated timing parameters

* 1.20 JMK 09/05/07 Updated clock frequency change

* Added ddr3_dimm module

* 1.30 JMK 01/23/08 Updated timing parameters

* 1.40 JMK 12/02/08 Added support for DDR3-1866 and DDR3-2133

* renamed ddr3_dimm.v to ddr3_module.v and added SODIMM support.

* Added multi-chip package model support in ddr3_mcp.v

* 1.50 JMK 05/04/08 Added 1866 and 2133 speed grades.

* 1.60 MYY 07/10/09 Merging of 1.50 version and pre-1.0 version changes

* 1.61 SPH 12/10/09 Only check tIH for cmd_addr if CS# LOW

*****************************************************************************************/

// DO NOT CHANGE THE TIMESCALE

// MAKE SURE YOUR SIMULATOR USES "PS" RESOLUTION

`timescale 1ps / 1ps

// model flags

// `define MODEL_PASR

module ddr3_model_c3(

rst_n,

ck,

ck_n,

cke,

cs_n,

ras_n,

cas_n,

we_n,

dm_tdqs,

ba,

addr,

dq,

dqs,

dqs_n,

tdqs_n,

odt

);

`include "ddr3_model_parameters_c3.vh"

parameter check_strict_mrbits = 1;

parameter check_strict_timing = 1;

parameter feature_pasr = 1;

parameter feature_truebl4 = 0;

// text macros

`define DQ_PER_DQS DQ_BITS/DQS_BITS

`define BANKS (1<<BA_BITS)

`define MAX_BITS (BA_BITS+ROW_BITS+COL_BITS-BL_BITS)

`define MAX_SIZE (1<<(BA_BITS+ROW_BITS+COL_BITS-BL_BITS))

`define MEM_SIZE (1<<MEM_BITS)

`define MAX_PIPE 4*CL_MAX

// Declare Ports

input rst_n;

input ck;

input ck_n;

input cke;

input cs_n;

input ras_n;

input cas_n;

input we_n;

inout [DM_BITS-1:0] dm_tdqs;

input [BA_BITS-1:0] ba;

input [ADDR_BITS-1:0] addr;

inout [DQ_BITS-1:0] dq;

inout [DQS_BITS-1:0] dqs;

inout [DQS_BITS-1:0] dqs_n;

output [DQS_BITS-1:0] tdqs_n;

input odt;

// clock jitter

real tck_avg;

time tck_sample [TDLLK-1:0];

time tch_sample [TDLLK-1:0];

time tcl_sample [TDLLK-1:0];

time tck_i;

time tch_i;

time tcl_i;

real tch_avg;

real tcl_avg;

time tm_ck_pos;

time tm_ck_neg;

real tjit_per_rtime;

integer tjit_cc_time;

real terr_nper_rtime;

//DDR3 clock jitter variables

real tjit_ch_rtime;

real duty_cycle;

// clock skew

real out_delay;

integer dqsck [DQS_BITS-1:0];

integer dqsck_min;

integer dqsck_max;

integer dqsq_min;

integer dqsq_max;

integer seed;

// Mode Registers

reg [ADDR_BITS-1:0] mode_reg [`BANKS-1:0];

reg burst_order;

reg [BL_BITS:0] burst_length;

reg blotf;

reg truebl4;

integer cas_latency;

reg dll_reset;

reg dll_locked;

integer write_recovery;

reg low_power;

reg dll_en;

reg [2:0] odt_rtt_nom;

reg [1:0] odt_rtt_wr;

reg odt_en;

reg dyn_odt_en;

reg [1:0] al;

integer additive_latency;

reg write_levelization;

reg duty_cycle_corrector;

reg tdqs_en;

reg out_en;

reg [2:0] pasr;

integer cas_write_latency;

reg asr; // auto self refresh

reg srt; // self refresh temperature range

reg [1:0] mpr_select;

reg mpr_en;

reg odts_readout;

integer read_latency;

integer write_latency;

// cmd encoding

parameter // {cs, ras, cas, we}

LOAD_MODE = 4'b0000,

REFRESH = 4'b0001,

PRECHARGE = 4'b0010,

ACTIVATE = 4'b0011,

WRITE = 4'b0100,

READ = 4'b0101,

ZQ = 4'b0110,

NOP = 4'b0111,

// DESEL = 4'b1xxx,

PWR_DOWN = 4'b1000,

SELF_REF = 4'b1001

;

reg [8*9-1:0] cmd_string [9:0];

initial begin

cmd_string[LOAD_MODE] = "Load Mode";

cmd_string[REFRESH ] = "Refresh ";

cmd_string[PRECHARGE] = "Precharge";

cmd_string[ACTIVATE ] = "Activate ";

cmd_string[WRITE ] = "Write ";

cmd_string[READ ] = "Read ";

cmd_string[ZQ ] = "ZQ ";

cmd_string[NOP ] = "No Op ";

cmd_string[PWR_DOWN ] = "Pwr Down ";

cmd_string[SELF_REF ] = "Self Ref ";

end

// command state

reg [`BANKS-1:0] active_bank;

reg [`BANKS-1:0] auto_precharge_bank;

reg [`BANKS-1:0] write_precharge_bank;

reg [`BANKS-1:0] read_precharge_bank;

reg [ROW_BITS-1:0] active_row [`BANKS-1:0];

reg in_power_down;

reg in_self_refresh;

reg [3:0] init_mode_reg;

reg init_dll_reset;

reg init_done;

integer init_step;

reg zq_set;

reg er_trfc_max;

reg odt_state;

reg odt_state_dly;

reg dyn_odt_state;

reg dyn_odt_state_dly;

reg prev_odt;

wire [7:0] calibration_pattern = 8'b10101010; // value returned during mpr pre-defined pattern readout

wire [7:0] temp_sensor = 8'h01; // value returned during mpr temp sensor readout

reg [1:0] mr_chk;

reg rd_bc;

integer banki;

// cmd timers/counters

integer ref_cntr;

integer odt_cntr;

integer ck_cntr;

integer ck_txpr;

integer ck_load_mode;

integer ck_refresh;

integer ck_precharge;

integer ck_activate;

integer ck_write;

integer ck_read;

integer ck_zqinit;

integer ck_zqoper;

integer ck_zqcs;

integer ck_power_down;

integer ck_slow_exit_pd;

integer ck_self_refresh;

integer ck_freq_change;

integer ck_odt;

integer ck_odth8;

integer ck_dll_reset;

integer ck_cke_cmd;

integer ck_bank_write [`BANKS-1:0];

integer ck_bank_read [`BANKS-1:0];

integer ck_group_activate [1:0];

integer ck_group_write [1:0];

integer ck_group_read [1:0];

time tm_txpr;

time tm_load_mode;

time tm_refresh;

time tm_precharge;

time tm_activate;

time tm_write_end;

time tm_power_down;

time tm_slow_exit_pd;

time tm_self_refresh;

time tm_freq_change;

time tm_cke_cmd;

time tm_ttsinit;

time tm_bank_precharge [`BANKS-1:0];

time tm_bank_activate [`BANKS-1:0];

time tm_bank_write_end [`BANKS-1:0];

time tm_bank_read_end [`BANKS-1:0];

time tm_group_activate [1:0];

time tm_group_write_end [1:0];

// pipelines

reg [`MAX_PIPE:0] al_pipeline;

reg [`MAX_PIPE:0] wr_pipeline;

reg [`MAX_PIPE:0] rd_pipeline;

reg [`MAX_PIPE:0] odt_pipeline;

reg [`MAX_PIPE:0] dyn_odt_pipeline;

reg [BL_BITS:0] bl_pipeline [`MAX_PIPE:0];

reg [BA_BITS-1:0] ba_pipeline [`MAX_PIPE:0];

reg [ROW_BITS-1:0] row_pipeline [`MAX_PIPE:0];

reg [COL_BITS-1:0] col_pipeline [`MAX_PIPE:0];

reg prev_cke;

// data state

reg [BL_MAX*DQ_BITS-1:0] memory_data;

reg [BL_MAX*DQ_BITS-1:0] bit_mask;

reg [BL_BITS-1:0] burst_position;

reg [BL_BITS:0] burst_cntr;

reg [DQ_BITS-1:0] dq_temp;

reg [31:0] check_write_postamble;

reg [31:0] check_write_preamble;

reg [31:0] check_write_dqs_high;

reg [31:0] check_write_dqs_low;

reg [15:0] check_dm_tdipw;

reg [63:0] check_dq_tdipw;

// data timers/counters

time tm_rst_n;

time tm_cke;

time tm_odt;

time tm_tdqss;

time tm_dm [15:0];

time tm_dqs [15:0];

time tm_dqs_pos [31:0];

time tm_dqss_pos [31:0];

time tm_dqs_neg [31:0];

time tm_dq [63:0];

time tm_cmd_addr [22:0];

reg [8*7-1:0] cmd_addr_string [22:0];

initial begin

cmd_addr_string[ 0] = "CS_N ";

cmd_addr_string[ 1] = "RAS_N ";

cmd_addr_string[ 2] = "CAS_N ";

cmd_addr_string[ 3] = "WE_N ";

cmd_addr_string[ 4] = "BA 0 ";

cmd_addr_string[ 5] = "BA 1 ";

cmd_addr_string[ 6] = "BA 2 ";

cmd_addr_string[ 7] = "ADDR 0";

cmd_addr_string[ 8] = "ADDR 1";

cmd_addr_string[ 9] = "ADDR 2";

cmd_addr_string[10] = "ADDR 3";

cmd_addr_string[11] = "ADDR 4";

cmd_addr_string[12] = "ADDR 5";

cmd_addr_string[13] = "ADDR 6";

cmd_addr_string[14] = "ADDR 7";

cmd_addr_string[15] = "ADDR 8";

cmd_addr_string[16] = "ADDR 9";

cmd_addr_string[17] = "ADDR 10";

cmd_addr_string[18] = "ADDR 11";

cmd_addr_string[19] = "ADDR 12";

cmd_addr_string[20] = "ADDR 13";

cmd_addr_string[21] = "ADDR 14";

cmd_addr_string[22] = "ADDR 15";

end

reg [8*5-1:0] dqs_string [1:0];

initial begin

dqs_string[0] = "DQS ";

dqs_string[1] = "DQS_N";

end

// Memory Storage

`ifdef MAX_MEM

parameter RFF_BITS = DQ_BITS*BL_MAX;

// %z format uses 8 bytes for every 32 bits or less.

parameter RFF_CHUNK = 8 * (RFF_BITS/32 + (RFF_BITS%32 ? 1 : 0));

reg [1024:1] tmp_model_dir;

integer memfd[`BANKS-1:0];

initial

begin : file_io_open

integer bank;

if (!$value$plusargs("model_data+%s", tmp_model_dir))

begin

tmp_model_dir = "/tmp";

$display(

"%m: at time %t WARNING: no +model_data option specified, using /tmp.",

$time

);

end

for (bank = 0; bank < `BANKS; bank = bank + 1)

memfd[bank] = open_bank_file(bank);

end

`else

reg [BL_MAX*DQ_BITS-1:0] memory [0:`MEM_SIZE-1];

reg [`MAX_BITS-1:0] address [0:`MEM_SIZE-1];

reg [MEM_BITS:0] memory_index;

reg [MEM_BITS:0] memory_used = 0;

`endif

// receive

reg rst_n_in;

reg ck_in;

reg ck_n_in;

reg cke_in;

reg cs_n_in;

reg ras_n_in;

reg cas_n_in;

reg we_n_in;

reg [15:0] dm_in;

reg [2:0] ba_in;

reg [15:0] addr_in;

reg [63:0] dq_in;

reg [31:0] dqs_in;

reg odt_in;

reg [15:0] dm_in_pos;

reg [15:0] dm_in_neg;

reg [63:0] dq_in_pos;

reg [63:0] dq_in_neg;

reg dq_in_valid;

reg dqs_in_valid;

integer wdqs_cntr;

integer wdq_cntr;

integer wdqs_pos_cntr [31:0];

reg b2b_write;

reg [BL_BITS:0] wr_burst_length;

reg [31:0] prev_dqs_in;

reg diff_ck;

always @(rst_n ) rst_n_in <= #BUS_DELAY rst_n;

always @(ck ) ck_in <= #BUS_DELAY ck;

always @(ck_n ) ck_n_in <= #BUS_DELAY ck_n;

always @(cke ) cke_in <= #BUS_DELAY cke;

always @(cs_n ) cs_n_in <= #BUS_DELAY cs_n;

always @(ras_n ) ras_n_in <= #BUS_DELAY ras_n;

always @(cas_n ) cas_n_in <= #BUS_DELAY cas_n;

always @(we_n ) we_n_in <= #BUS_DELAY we_n;

always @(dm_tdqs) dm_in <= #BUS_DELAY dm_tdqs;

always @(ba ) ba_in <= #BUS_DELAY ba;

always @(addr ) addr_in <= #BUS_DELAY addr;

always @(dq ) dq_in <= #BUS_DELAY dq;

always @(dqs or dqs_n) dqs_in <= #BUS_DELAY (dqs_n<<16) | dqs;

always @(odt ) odt_in <= #BUS_DELAY odt;

// create internal clock

always @(posedge ck_in) diff_ck <= ck_in;

always @(posedge ck_n_in) diff_ck <= ~ck_n_in;

wire [15:0] dqs_even = dqs_in[15:0];

wire [15:0] dqs_odd = dqs_in[31:16];

wire [3:0] cmd_n_in = !cs_n_in ? {ras_n_in, cas_n_in, we_n_in} : NOP; //deselect = nop

// transmit

reg dqs_out_en;

reg [DQS_BITS-1:0] dqs_out_en_dly;

reg dqs_out;

reg [DQS_BITS-1:0] dqs_out_dly;

reg dq_out_en;

reg [DQ_BITS-1:0] dq_out_en_dly;

reg [DQ_BITS-1:0] dq_out;

reg [DQ_BITS-1:0] dq_out_dly;

integer rdqsen_cntr;

integer rdqs_cntr;

integer rdqen_cntr;

integer rdq_cntr;

bufif1 buf_dqs [DQS_BITS-1:0] (dqs, dqs_out_dly, dqs_out_en_dly & {DQS_BITS{out_en}});

bufif1 buf_dqs_n [DQS_BITS-1:0] (dqs_n, ~dqs_out_dly, dqs_out_en_dly & {DQS_BITS{out_en}});

bufif1 buf_dq [DQ_BITS-1:0] (dq, dq_out_dly, dq_out_en_dly & {DQ_BITS {out_en}});

assign tdqs_n = {DQS_BITS{1'bz}};

initial begin

if (BL_MAX < 2)

$display("%m ERROR: BL_MAX parameter must be >= 2. \nBL_MAX = %d", BL_MAX);

if ((1<<BO_BITS) > BL_MAX)

$display("%m ERROR: 2^BO_BITS cannot be greater than BL_MAX parameter.");

$timeformat (-12, 1, " ps", 1);

seed = RANDOM_SEED;

ck_cntr = 0;

end

function integer get_rtt_wr;

input [1:0] rtt;

begin

get_rtt_wr = RZQ/{rtt[0], rtt[1], 1'b0};

end

endfunction

function integer get_rtt_nom;

input [2:0] rtt;

begin

case (rtt)

1: get_rtt_nom = RZQ/4;

2: get_rtt_nom = RZQ/2;

3: get_rtt_nom = RZQ/6;

4: get_rtt_nom = RZQ/12;

5: get_rtt_nom = RZQ/8;

default : get_rtt_nom = 0;

endcase

end

endfunction

// calculate the absolute value of a real number

function real abs_value;

input arg;

real arg;

begin

if (arg < 0.0)

abs_value = -1.0 * arg;

else

abs_value = arg;

end

endfunction

function integer ceil;

input number;

real number;

// LMR 4.1.7

// When either operand of a relational expression is a real operand then the other operand shall be converted

// to an equivalent real value, and the expression shall be interpreted as a comparison between two real values.

if (number > $rtoi(number))

ceil = $rtoi(number) + 1;

else

ceil = number;

endfunction

function integer floor;

input number;

real number;

// LMR 4.1.7

// When either operand of a relational expression is a real operand then the other operand shall be converted

// to an equivalent real value, and the expression shall be interpreted as a comparison between two real values.

if (number < $rtoi(number))

floor = $rtoi(number) - 1;

else

floor = number;

endfunction

`ifdef MAX_MEM

function integer open_bank_file( input integer bank );

integer fd;

reg [2048:1] filename;

begin

$sformat( filename, "%0s/%m.%0d", tmp_model_dir, bank );

fd = $fopen(filename, "w+");

if (fd == 0)

begin

$display("%m: at time %0t ERROR: failed to open %0s.", $time, filename);

$finish;

end

else

begin

if (DEBUG) $display("%m: at time %0t INFO: opening %0s.", $time, filename);

open_bank_file = fd;

end

end

endfunction

function [RFF_BITS:1] read_from_file(

input integer fd,

input integer index

);

integer code;

integer offset;

reg [1024:1] msg;

reg [RFF_BITS:1] read_value;

begin

offset = index * RFF_CHUNK;

code = $fseek( fd, offset, 0 );

// $fseek returns 0 on success, -1 on failure

if (code != 0)

begin

$display("%m: at time %t ERROR: fseek to %d failed", $time, offset);

$finish;

end

code = $fscanf(fd, "%z", read_value);

// $fscanf returns number of items read

if (code != 1)

begin

if ($ferror(fd,msg) != 0)

begin

$display("%m: at time %t ERROR: fscanf failed at %d", $time, index);

$display(msg);

$finish;

end

else

read_value = 'hx;

end

/* when reading from unwritten portions of the file, 0 will be returned.

* Use 0 in bit 1 as indicator that invalid data has been read.

* A true 0 is encoded as Z.

*/

if (read_value[1] === 1'bz)

// true 0 encoded as Z, data is valid

read_value[1] = 1'b0;

else if (read_value[1] === 1'b0)

// read from file section that has not been written

read_value = 'hx;

read_from_file = read_value;

end

endfunction

task write_to_file(

input integer fd,

input integer index,

input [RFF_BITS:1] data

);

integer code;

integer offset;

begin

offset = index * RFF_CHUNK;

code = $fseek( fd, offset, 0 );

if (code != 0)

begin

$display("%m: at time %t ERROR: fseek to %d failed", $time, offset);

$finish;

end

// encode a valid data

if (data[1] === 1'bz)

data[1] = 1'bx;

else if (data[1] === 1'b0)

data[1] = 1'bz;

$fwrite( fd, "%z", data );

end

endtask

`else

function get_index;

input [`MAX_BITS-1:0] addr;

begin : index

get_index = 0;

for (memory_index=0; memory_index<memory_used; memory_index=memory_index+1) begin

if (address[memory_index] == addr) begin

get_index = 1;

disable index;

end

end

end

endfunction

`endif

task memory_write;

input [BA_BITS-1:0] bank;

input [ROW_BITS-1:0] row;

input [COL_BITS-1:0] col;

input [BL_MAX*DQ_BITS-1:0] data;

reg [`MAX_BITS-1:0] addr;

begin

`ifdef MAX_MEM

addr = {row, col}/BL_MAX;

write_to_file( memfd[bank], addr, data );

`else

// chop off the lowest address bits

addr = {bank, row, col}/BL_MAX;

if (get_index(addr)) begin

address[memory_index] = addr;

memory[memory_index] = data;

end else if (memory_used == `MEM_SIZE) begin

$display ("%m: at time %t ERROR: Memory overflow. Write to Address %h with Data %h will be lost.\nYou must increase the MEM_BITS parameter or define MAX_MEM.", $time, addr, data);

if (STOP_ON_ERROR) $stop(0);

end else begin

address[memory_used] = addr;

memory[memory_used] = data;

memory_used = memory_used + 1;

end

`endif

end

endtask

task memory_read;

input [BA_BITS-1:0] bank;

input [ROW_BITS-1:0] row;

input [COL_BITS-1:0] col;

output [BL_MAX*DQ_BITS-1:0] data;

reg [`MAX_BITS-1:0] addr;

begin

`ifdef MAX_MEM

addr = {row, col}/BL_MAX;

data = read_from_file( memfd[bank], addr );

`else

// chop off the lowest address bits

addr = {bank, row, col}/BL_MAX;

if (get_index(addr)) begin

data = memory[memory_index];

end else begin

data = {BL_MAX*DQ_BITS{1'bx}};

end

`endif

end

endtask

task set_latency;

begin

if (al == 0) begin

additive_latency = 0;

end else begin

additive_latency = cas_latency - al;

end

read_latency = cas_latency + additive_latency;

write_latency = cas_write_latency + additive_latency;

end

endtask

// this task will erase the contents of 0 or more banks

task erase_banks;

input [`BANKS-1:0] banks; //one select bit per bank

reg [BA_BITS-1:0] ba;

reg [`MAX_BITS-1:0] i;

integer bank;

begin

`ifdef MAX_MEM

for (bank = 0; bank < `BANKS; bank = bank + 1)

if (banks[bank] === 1'b1) begin

$fclose(memfd[bank]);

memfd[bank] = open_bank_file(bank);

end

`else

memory_index = 0;

i = 0;

// remove the selected banks

for (memory_index=0; memory_index<memory_used; memory_index=memory_index+1) begin

ba = (address[memory_index]>>(ROW_BITS+COL_BITS-BL_BITS));

if (!banks[ba]) begin //bank is selected to keep

address[i] = address[memory_index];

memory[i] = memory[memory_index];

i = i + 1;

end

end

// clean up the unused banks

for (memory_index=i; memory_index<memory_used; memory_index=memory_index+1) begin

address[memory_index] = 'bx;

memory[memory_index] = {8*DQ_BITS{1'bx}};

end

memory_used = i;

`endif

end

endtask

// Before this task runs, the model must be in a valid state for precharge power down and out of reset.

// After this task runs, NOP commands must be issued until TZQINIT has been met

task initialize;

input [ADDR_BITS-1:0] mode_reg0;

input [ADDR_BITS-1:0] mode_reg1;

input [ADDR_BITS-1:0] mode_reg2;

input [ADDR_BITS-1:0] mode_reg3;

begin

if (DEBUG) $display ("%m: at time %t INFO: Performing Initialization Sequence", $time);

cmd_task(1, NOP, 'bx, 'bx);

cmd_task(1, ZQ, 'bx, 'h400); //ZQCL

cmd_task(1, LOAD_MODE, 3, mode_reg3);

cmd_task(1, LOAD_MODE, 2, mode_reg2);

cmd_task(1, LOAD_MODE, 1, mode_reg1);

cmd_task(1, LOAD_MODE, 0, mode_reg0 | 'h100); // DLL Reset

cmd_task(0, NOP, 'bx, 'bx);

end

endtask

task reset_task;

integer i;

begin

// disable inputs

dq_in_valid = 0;

dqs_in_valid <= 0;

wdqs_cntr = 0;

wdq_cntr = 0;

for (i=0; i<31; i=i+1) begin

wdqs_pos_cntr[i] <= 0;

end

b2b_write <= 0;

// disable outputs

out_en = 0;

dq_out_en = 0;

rdq_cntr = 0;

dqs_out_en = 0;

rdqs_cntr = 0;

// disable ODT

odt_en = 0;

dyn_odt_en = 0;

odt_state = 0;

dyn_odt_state = 0;

// reset bank state

active_bank = 0;

auto_precharge_bank = 0;

read_precharge_bank = 0;

write_precharge_bank = 0;

// require initialization sequence

init_done = 0;

mpr_en = 0;

init_step = 0;

init_mode_reg = 0;

init_dll_reset = 0;

zq_set = 0;

// reset DLL

dll_en = 0;

dll_reset = 0;

dll_locked = 0;

// exit power down and self refresh

prev_cke = 1'bx;

in_power_down = 0;

in_self_refresh = 0;

// clear pipelines

al_pipeline = 0;

wr_pipeline = 0;

rd_pipeline = 0;

odt_pipeline = 0;

dyn_odt_pipeline = 0;

end

endtask

parameter SAME_BANK = 2'd0; // same bank, same group

parameter DIFF_BANK = 2'd1; // different bank, same group

parameter DIFF_GROUP = 2'd2; // different bank, different group

task chk_err;

input [1:0] relationship;

input [BA_BITS-1:0] bank;

input [3:0] fromcmd;

input [3:0] cmd;

reg err;

begin

// $display ("truebl4 = %d, relationship = %d, fromcmd = %h, cmd = %h", truebl4, relationship, fromcmd, cmd);

casex ({truebl4, relationship, fromcmd, cmd})

// load mode

{1'bx, DIFF_BANK , LOAD_MODE, LOAD_MODE} : begin if (ck_cntr - ck_load_mode < TMRD) $display ("%m: at time %t ERROR: tMRD violation during %s", $time, cmd_string[cmd]); end

{1'bx, DIFF_BANK , LOAD_MODE, READ } : begin if (($time - tm_load_mode < TMOD) || (ck_cntr - ck_load_mode < TMOD_TCK)) $display ("%m: at time %t ERROR: tMOD violation during %s", $time, cmd_string[cmd]); end

{1'bx, DIFF_BANK , LOAD_MODE, REFRESH } ,

{1'bx, DIFF_BANK , LOAD_MODE, PRECHARGE} ,

{1'bx, DIFF_BANK , LOAD_MODE, ACTIVATE } ,

{1'bx, DIFF_BANK , LOAD_MODE, ZQ } ,

{1'bx, DIFF_BANK , LOAD_MODE, PWR_DOWN } ,

{1'bx, DIFF_BANK , LOAD_MODE, SELF_REF } : begin if (($time - tm_load_mode < TMOD) || (ck_cntr - ck_load_mode < TMOD_TCK)) $display ("%m: at time %t ERROR: tMOD violation during %s", $time, cmd_string[cmd]); end

// refresh

{1'bx, DIFF_BANK , REFRESH , LOAD_MODE} ,

{1'bx, DIFF_BANK , REFRESH , REFRESH } ,

{1'bx, DIFF_BANK , REFRESH , PRECHARGE} ,

{1'bx, DIFF_BANK , REFRESH , ACTIVATE } ,

{1'bx, DIFF_BANK , REFRESH , ZQ } ,

{1'bx, DIFF_BANK , REFRESH , SELF_REF } : begin if ($time - tm_refresh < TRFC_MIN) $display ("%m: at time %t ERROR: tRFC violation during %s", $time, cmd_string[cmd]); end

{1'bx, DIFF_BANK , REFRESH , PWR_DOWN } : begin if (ck_cntr - ck_refresh < TREFPDEN) $display ("%m: at time %t ERROR: tREFPDEN violation during %s", $time, cmd_string[cmd]); end

// precharge

{1'bx, SAME_BANK , PRECHARGE, ACTIVATE } : begin if ($time - tm_bank_precharge[bank] < TRP) $display ("%m: at time %t ERROR: tRP violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'bx, DIFF_BANK , PRECHARGE, LOAD_MODE} ,

{1'bx, DIFF_BANK , PRECHARGE, REFRESH } ,

{1'bx, DIFF_BANK , PRECHARGE, ZQ } ,

{1'bx, DIFF_BANK , PRECHARGE, SELF_REF } : begin if ($time - tm_precharge < TRP) $display ("%m: at time %t ERROR: tRP violation during %s", $time, cmd_string[cmd]); end

{1'bx, DIFF_BANK , PRECHARGE, PWR_DOWN } : ; //tPREPDEN = 1 tCK, can be concurrent with auto precharge

// activate

{1'bx, SAME_BANK , ACTIVATE , PRECHARGE} : begin if ($time - tm_bank_activate[bank] > TRAS_MAX) $display ("%m: at time %t ERROR: tRAS maximum violation during %s to bank %d", $time, cmd_string[cmd], bank);

if ($time - tm_bank_activate[bank] < TRAS_MIN) $display ("%m: at time %t ERROR: tRAS minimum violation during %s to bank %d", $time, cmd_string[cmd], bank);end

{1'bx, SAME_BANK , ACTIVATE , ACTIVATE } : begin if ($time - tm_bank_activate[bank] < TRC) $display ("%m: at time %t ERROR: tRC violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'bx, SAME_BANK , ACTIVATE , WRITE } ,

{1'bx, SAME_BANK , ACTIVATE , READ } : ; // tRCD is checked outside this task

{1'b0, DIFF_BANK , ACTIVATE , ACTIVATE } : begin if (($time - tm_activate < TRRD) || (ck_cntr - ck_activate < TRRD_TCK)) $display ("%m: at time %t ERROR: tRRD violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b1, DIFF_BANK , ACTIVATE , ACTIVATE } : begin if (($time - tm_group_activate[bank[1]] < TRRD) || (ck_cntr - ck_group_activate[bank[1]] < TRRD_TCK)) $display ("%m: at time %t ERROR: tRRD violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b1, DIFF_GROUP, ACTIVATE , ACTIVATE } : begin if (($time - tm_activate < TRRD_DG) || (ck_cntr - ck_activate < TRRD_DG_TCK)) $display ("%m: at time %t ERROR: tRRD_DG violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'bx, DIFF_BANK , ACTIVATE , REFRESH } : begin if ($time - tm_activate < TRC) $display ("%m: at time %t ERROR: tRC violation during %s", $time, cmd_string[cmd]); end

{1'bx, DIFF_BANK , ACTIVATE , PWR_DOWN } : begin if (ck_cntr - ck_activate < TACTPDEN) $display ("%m: at time %t ERROR: tACTPDEN violation during %s", $time, cmd_string[cmd]); end

// write

{1'bx, SAME_BANK , WRITE , PRECHARGE} : begin if (($time - tm_bank_write_end[bank] < TWR) || (ck_cntr - ck_bank_write[bank] <= write_latency + burst_length/2)) $display ("%m: at time %t ERROR: tWR violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b0, DIFF_BANK , WRITE , WRITE } : begin if (ck_cntr - ck_write < TCCD) $display ("%m: at time %t ERROR: tCCD violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b1, DIFF_BANK , WRITE , WRITE } : begin if (ck_cntr - ck_group_write[bank[1]] < TCCD) $display ("%m: at time %t ERROR: tCCD violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b0, DIFF_BANK , WRITE , READ } : begin if (ck_cntr - ck_write < write_latency + burst_length/2 + TWTR_TCK - additive_latency) $display ("%m: at time %t ERROR: tWTR violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b1, DIFF_BANK , WRITE , READ } : begin if (ck_cntr - ck_group_write[bank[1]] < write_latency + burst_length/2 + TWTR_TCK - additive_latency) $display ("%m: at time %t ERROR: tWTR violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b1, DIFF_GROUP, WRITE , WRITE } : begin if (ck_cntr - ck_write < TCCD_DG) $display ("%m: at time %t ERROR: tCCD_DG violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b1, DIFF_GROUP, WRITE , READ } : begin if (ck_cntr - ck_write < write_latency + burst_length/2 + TWTR_DG_TCK - additive_latency) $display ("%m: at time %t ERROR: tWTR_DG violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'bx, DIFF_BANK , WRITE , PWR_DOWN } : begin if (($time - tm_write_end < TWR) || (ck_cntr - ck_write < write_latency + burst_length/2)) $display ("%m: at time %t ERROR: tWRPDEN violation during %s", $time, cmd_string[cmd]); end

// read

{1'bx, SAME_BANK , READ , PRECHARGE} : begin if (($time - tm_bank_read_end[bank] < TRTP) || (ck_cntr - ck_bank_read[bank] < additive_latency + TRTP_TCK)) $display ("%m: at time %t ERROR: tRTP violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b0, DIFF_BANK , READ , WRITE } : ; // tRTW is checked outside this task

{1'b1, DIFF_BANK , READ , WRITE } : ; // tRTW is checked outside this task

{1'b0, DIFF_BANK , READ , READ } : begin if (ck_cntr - ck_read < TCCD) $display ("%m: at time %t ERROR: tCCD violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b1, DIFF_BANK , READ , READ } : begin if (ck_cntr - ck_group_read[bank[1]] < TCCD) $display ("%m: at time %t ERROR: tCCD violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'b1, DIFF_GROUP, READ , WRITE } : ; // tRTW is checked outside this task

{1'b1, DIFF_GROUP, READ , READ } : begin if (ck_cntr - ck_read < TCCD_DG) $display ("%m: at time %t ERROR: tCCD_DG violation during %s to bank %d", $time, cmd_string[cmd], bank); end

{1'bx, DIFF_BANK , READ , PWR_DOWN } : begin if (ck_cntr - ck_read < read_latency + 5) $display ("%m: at time %t ERROR: tRDPDEN violation during %s", $time, cmd_string[cmd]); end

// zq

{1'bx, DIFF_BANK , ZQ , LOAD_MODE} : ; // 1 tCK

{1'bx, DIFF_BANK , ZQ , REFRESH } ,

{1'bx, DIFF_BANK , ZQ , PRECHARGE} ,

{1'bx, DIFF_BANK , ZQ , ACTIVATE } ,

{1'bx, DIFF_BANK , ZQ , ZQ } ,

{1'bx, DIFF_BANK , ZQ , PWR_DOWN } ,

{1'bx, DIFF_BANK , ZQ , SELF_REF } : begin if (ck_cntr - ck_zqinit < TZQINIT) $display ("%m: at time %t ERROR: tZQinit violation during %s", $time, cmd_string[cmd]);

if (ck_cntr - ck_zqoper < TZQOPER) $display ("%m: at time %t ERROR: tZQoper violation during %s", $time, cmd_string[cmd]);

if (ck_cntr - ck_zqcs < TZQCS) $display ("%m: at time %t ERROR: tZQCS violation during %s", $time, cmd_string[cmd]); end

// power down

{1'bx, DIFF_BANK , PWR_DOWN , LOAD_MODE} ,

{1'bx, DIFF_BANK , PWR_DOWN , REFRESH } ,

{1'bx, DIFF_BANK , PWR_DOWN , PRECHARGE} ,

{1'bx, DIFF_BANK , PWR_DOWN , ACTIVATE } ,

{1'bx, DIFF_BANK , PWR_DOWN , WRITE } ,

{1'bx, DIFF_BANK , PWR_DOWN , ZQ } : begin if (($time - tm_power_down < TXP) || (ck_cntr - ck_power_down < TXP_TCK)) $display ("%m: at time %t ERROR: tXP violation during %s", $time, cmd_string[cmd]); end

{1'bx, DIFF_BANK , PWR_DOWN , READ } : begin if (($time - tm_power_down < TXP) || (ck_cntr - ck_power_down < TXP_TCK)) $display ("%m: at time %t ERROR: tXP violation during %s", $time, cmd_string[cmd]);

else if (($time - tm_slow_exit_pd < TXPDLL) || (ck_cntr - ck_slow_exit_pd < TXPDLL_TCK)) $display ("%m: at time %t ERROR: tXPDLL violation during %s", $time, cmd_string[cmd]); end

{1'bx, DIFF_BANK , PWR_DOWN , PWR_DOWN } ,

{1'bx, DIFF_BANK , PWR_DOWN , SELF_REF } : begin if (($time - tm_power_down < TXP) || (ck_cntr - ck_power_down < TXP_TCK)) $display ("%m: at time %t ERROR: tXP violation during %s", $time, cmd_string[cmd]);

if ((tm_power_down > tm_refresh) && ($time - tm_refresh < TRFC_MIN)) $display ("%m: at time %t ERROR: tRFC violation during %s", $time, cmd_string[cmd]);

if ((tm_refresh > tm_power_down) && (($time - tm_power_down < TXPDLL) || (ck_cntr - ck_power_down < TXPDLL_TCK))) $display ("%m: at time %t ERROR: tXPDLL violation during %s", $time, cmd_string[cmd]);

if (($time - tm_cke_cmd < TCKE) || (ck_cntr - ck_cke_cmd < TCKE_TCK)) $display ("%m: at time %t ERROR: tCKE violation on CKE", $time); end

// self refresh

{1'bx, DIFF_BANK , SELF_REF , LOAD_MODE} ,

{1'bx, DIFF_BANK , SELF_REF , REFRESH } ,

{1'bx, DIFF_BANK , SELF_REF , PRECHARGE} ,

{1'bx, DIFF_BANK , SELF_REF , ACTIVATE } ,

{1'bx, DIFF_BANK , SELF_REF , WRITE } ,

{1'bx, DIFF_BANK , SELF_REF , ZQ } : begin if (($time - tm_self_refresh < TXS) || (ck_cntr - ck_self_refresh < TXS_TCK)) $display ("%m: at time %t ERROR: tXS violation during %s", $time, cmd_string[cmd]); end

{1'bx, DIFF_BANK , SELF_REF , READ } : begin if (ck_cntr - ck_self_refresh < TXSDLL) $display ("%m: at time %t ERROR: tXSDLL violation during %s", $time, cmd_string[cmd]); end

{1'bx, DIFF_BANK , SELF_REF , PWR_DOWN } ,

{1'bx, DIFF_BANK , SELF_REF , SELF_REF } : begin if (($time - tm_self_refresh < TXS) || (ck_cntr - ck_self_refresh < TXS_TCK)) $display ("%m: at time %t ERROR: tXS violation during %s", $time, cmd_string[cmd]);

if (($time - tm_cke_cmd < TCKE) || (ck_cntr - ck_cke_cmd < TCKE_TCK)) $display ("%m: at time %t ERROR: tCKE violation on CKE", $time); end

endcase

end

endtask

task cmd_task;

input cke;

input [2:0] cmd;

input [BA_BITS-1:0] bank;

input [ADDR_BITS-1:0] addr;

reg [`BANKS:0] i;

integer j;

reg [`BANKS:0] tfaw_cntr;

reg [COL_BITS-1:0] col;

reg group;

begin

// tRFC max check

if (!er_trfc_max && !in_self_refresh) begin

if ($time - tm_refresh > TRFC_MAX && check_strict_timing) begin

$display ("%m: at time %t ERROR: tRFC maximum violation during %s", $time, cmd_string[cmd]);

er_trfc_max = 1;

end

end

if (cke) begin

if ((cmd < NOP) && (cmd != PRECHARGE)) begin

if (($time - tm_txpr < TXPR) || (ck_cntr - ck_txpr < TXPR_TCK))

$display ("%m: at time %t ERROR: tXPR violation during %s", $time, cmd_string[cmd]);

for (j=0; j<=SELF_REF; j=j+1) begin

chk_err(SAME_BANK , bank, j, cmd);

chk_err(DIFF_BANK , bank, j, cmd);

chk_err(DIFF_GROUP, bank, j, cmd);

end

end

case (cmd)

LOAD_MODE : begin

if (|odt_pipeline)

$display ("%m: at time %t ERROR: ODTL violation during %s", $time, cmd_string[cmd]);

if (odt_state)

$display ("%m: at time %t ERROR: ODT must be off prior to %s", $time, cmd_string[cmd]);

if (|active_bank) begin

$display ("%m: at time %t ERROR: %s Failure. All banks must be Precharged.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d", $time, cmd_string[cmd], bank);

if (bank>>2) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved bank bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

case (bank)

0 : begin

// Burst Length

if (addr[1:0] == 2'b00) begin

burst_length = 8;

blotf = 0;

truebl4 = 0;

if (DEBUG) $display ("%m: at time %t INFO: %s %d Burst Length = %d", $time, cmd_string[cmd], bank, burst_length);

end else if (addr[1:0] == 2'b01) begin

burst_length = 8;

blotf = 1;

truebl4 = 0;

if (DEBUG) $display ("%m: at time %t INFO: %s %d Burst Length = Select via A12", $time, cmd_string[cmd], bank);

end else if (addr[1:0] == 2'b10) begin

burst_length = 4;

blotf = 0;

truebl4 = 0;

if (DEBUG) $display ("%m: at time %t INFO: %s %d Burst Length = Fixed %d (chop)", $time, cmd_string[cmd], bank, burst_length);

end else if (feature_truebl4 && (addr[1:0] == 2'b11)) begin

burst_length = 4;

blotf = 0;

truebl4 = 1;

if (DEBUG) $display ("%m: at time %t INFO: %s %d Burst Length = True %d", $time, cmd_string[cmd], bank, burst_length);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Burst Length = %d", $time, cmd_string[cmd], bank, addr[1:0]);

end

// Burst Order

burst_order = addr[3];

if (!burst_order) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Burst Order = Sequential", $time, cmd_string[cmd], bank);

end else if (burst_order) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Burst Order = Interleaved", $time, cmd_string[cmd], bank);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Burst Order = %d", $time, cmd_string[cmd], bank, burst_order);

end

// CAS Latency

cas_latency = {addr[2],addr[6:4]} + 4;

set_latency;

if ((cas_latency >= CL_MIN) && (cas_latency <= CL_MAX)) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d CAS Latency = %d", $time, cmd_string[cmd], bank, cas_latency);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal CAS Latency = %d", $time, cmd_string[cmd], bank, cas_latency);

end

// Reserved

if (addr[7] !== 0 && check_strict_mrbits) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved address bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

// DLL Reset

dll_reset = addr[8];

if (!dll_reset) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d DLL Reset = Normal", $time, cmd_string[cmd], bank);

end else if (dll_reset) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d DLL Reset = Reset DLL", $time, cmd_string[cmd], bank);

dll_locked = 0;

init_dll_reset = 1;

ck_dll_reset <= ck_cntr;

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal DLL Reset = %d", $time, cmd_string[cmd], bank, dll_reset);

end

// Write Recovery

if (addr[11:9] == 0) begin

write_recovery = 16;

end else if (addr[11:9] < 4) begin

write_recovery = addr[11:9] + 4;

end else begin

write_recovery = 2*addr[11:9];

end

if ((write_recovery >= WR_MIN) && (write_recovery <= WR_MAX)) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Write Recovery = %d", $time, cmd_string[cmd], bank, write_recovery);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Write Recovery = %d", $time, cmd_string[cmd], bank, write_recovery);

end

// Power Down Mode

low_power = !addr[12];

if (!low_power) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Power Down Mode = DLL on", $time, cmd_string[cmd], bank);

end else if (low_power) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Power Down Mode = DLL off", $time, cmd_string[cmd], bank);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Power Down Mode = %d", $time, cmd_string[cmd], bank, low_power);

end

// Reserved

if (ADDR_BITS>13 && addr[13] !== 0 && check_strict_mrbits) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved address bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

end

1 : begin

// DLL Enable

dll_en = !addr[0];

if (!dll_en) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d DLL Enable = Disabled", $time, cmd_string[cmd], bank);

if (check_strict_mrbits) $display ("%m: at time %t WARNING: %s %d DLL off mode is not modeled", $time, cmd_string[cmd], bank);

end else if (dll_en) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d DLL Enable = Enabled", $time, cmd_string[cmd], bank);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal DLL Enable = %d", $time, cmd_string[cmd], bank, dll_en);

end

// Output Drive Strength

if ({addr[5], addr[1]} == 2'b00) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Output Drive Strength = %d Ohm", $time, cmd_string[cmd], bank, RZQ/6);

end else if ({addr[5], addr[1]} == 2'b01) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Output Drive Strength = %d Ohm", $time, cmd_string[cmd], bank, RZQ/7);

end else if ({addr[5], addr[1]} == 2'b11) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Output Drive Strength = %d Ohm", $time, cmd_string[cmd], bank, RZQ/5);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Output Drive Strength = %d", $time, cmd_string[cmd], bank, {addr[5], addr[1]});

end

// ODT Rtt (Rtt_NOM)

odt_rtt_nom = {addr[9], addr[6], addr[2]};

if (odt_rtt_nom == 3'b000) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d ODT Rtt = Disabled", $time, cmd_string[cmd], bank);

odt_en = 0;

end else if ((odt_rtt_nom < 4) || ((!addr[7] || (addr[7] && addr[12])) && (odt_rtt_nom < 6))) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d ODT Rtt = %d Ohm", $time, cmd_string[cmd], bank, get_rtt_nom(odt_rtt_nom));

odt_en = 1;

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal ODT Rtt = %d", $time, cmd_string[cmd], bank, odt_rtt_nom);

odt_en = 0;

end

// Report the additive latency value

al = addr[4:3];

set_latency;

if (al == 0) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Additive Latency = %d", $time, cmd_string[cmd], bank, al);

end else if ((al >= AL_MIN) && (al <= AL_MAX)) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Additive Latency = CL - %d", $time, cmd_string[cmd], bank, al);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Additive Latency = %d", $time, cmd_string[cmd], bank, al);

end

// Write Levelization

write_levelization = addr[7];

if (!write_levelization) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Write Levelization = Disabled", $time, cmd_string[cmd], bank);

end else if (write_levelization) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Write Levelization = Enabled", $time, cmd_string[cmd], bank);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Write Levelization = %d", $time, cmd_string[cmd], bank, write_levelization);

end

// Reserved

if (addr[8] !== 0 && check_strict_mrbits) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved address bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

// Reserved

if (addr[10] !== 0 && check_strict_mrbits) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved address bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

// TDQS Enable

tdqs_en = addr[11];

if (!tdqs_en) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d TDQS Enable = Disabled", $time, cmd_string[cmd], bank);

end else if (tdqs_en) begin

if (8 == DQ_BITS) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d TDQS Enable = Enabled", $time, cmd_string[cmd], bank);

end

else begin

$display ("%m: at time %t WARNING: %s %d Illegal TDQS Enable. TDQS only exists on a x8 part", $time, cmd_string[cmd], bank);

tdqs_en = 0;

end

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal TDQS Enable = %d", $time, cmd_string[cmd], bank, tdqs_en);

end

// Output Enable

out_en = !addr[12];

if (!out_en) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Qoff = Disabled", $time, cmd_string[cmd], bank);

end else if (out_en) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Qoff = Enabled", $time, cmd_string[cmd], bank);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Qoff = %d", $time, cmd_string[cmd], bank, out_en);

end

// Reserved

if (ADDR_BITS>13 && addr[13] !== 0 && check_strict_mrbits) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved address bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

end

2 : begin

if (feature_pasr) begin

// Partial Array Self Refresh

pasr = addr[2:0];

case (pasr)

3'b000 : if (DEBUG) $display ("%m: at time %t INFO: %s %d Partial Array Self Refresh = Bank 0-7", $time, cmd_string[cmd], bank);

3'b001 : if (DEBUG) $display ("%m: at time %t INFO: %s %d Partial Array Self Refresh = Bank 0-3", $time, cmd_string[cmd], bank);

3'b010 : if (DEBUG) $display ("%m: at time %t INFO: %s %d Partial Array Self Refresh = Bank 0-1", $time, cmd_string[cmd], bank);

3'b011 : if (DEBUG) $display ("%m: at time %t INFO: %s %d Partial Array Self Refresh = Bank 0", $time, cmd_string[cmd], bank);

3'b100 : if (DEBUG) $display ("%m: at time %t INFO: %s %d Partial Array Self Refresh = Bank 2-7", $time, cmd_string[cmd], bank);

3'b101 : if (DEBUG) $display ("%m: at time %t INFO: %s %d Partial Array Self Refresh = Bank 4-7", $time, cmd_string[cmd], bank);

3'b110 : if (DEBUG) $display ("%m: at time %t INFO: %s %d Partial Array Self Refresh = Bank 6-7", $time, cmd_string[cmd], bank);

3'b111 : if (DEBUG) $display ("%m: at time %t INFO: %s %d Partial Array Self Refresh = Bank 7", $time, cmd_string[cmd], bank);

default : $display ("%m: at time %t ERROR: %s %d Illegal Partial Array Self Refresh = %d", $time, cmd_string[cmd], bank, pasr);

endcase

end

else

if (addr[2:0] !== 0 && check_strict_mrbits) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved address bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

// CAS Write Latency

cas_write_latency = addr[5:3]+5;

set_latency;

if ((cas_write_latency >= CWL_MIN) && (cas_write_latency <= CWL_MAX)) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d CAS Write Latency = %d", $time, cmd_string[cmd], bank, cas_write_latency);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal CAS Write Latency = %d", $time, cmd_string[cmd], bank, cas_write_latency);

end

// Auto Self Refresh Method

asr = addr[6];

if (!asr) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Auto Self Refresh = Disabled", $time, cmd_string[cmd], bank);

end else if (asr) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Auto Self Refresh = Enabled", $time, cmd_string[cmd], bank);

if (check_strict_mrbits) $display ("%m: at time %t WARNING: %s %d Auto Self Refresh is not modeled", $time, cmd_string[cmd], bank);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Auto Self Refresh = %d", $time, cmd_string[cmd], bank, asr);

end

// Self Refresh Temperature

srt = addr[7];

if (!srt) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Self Refresh Temperature = Normal", $time, cmd_string[cmd], bank);

end else if (srt) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Self Refresh Temperature = Extended", $time, cmd_string[cmd], bank);

if (check_strict_mrbits) $display ("%m: at time %t WARNING: %s %d Self Refresh Temperature is not modeled", $time, cmd_string[cmd], bank);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Self Refresh Temperature = %d", $time, cmd_string[cmd], bank, srt);

end

if (asr && srt)

$display ("%m: at time %t ERROR: %s %d SRT must be set to 0 when ASR is enabled.", $time, cmd_string[cmd], bank);

// Reserved

if (addr[8] !== 0 && check_strict_mrbits) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved address bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

// Dynamic ODT (Rtt_WR)

odt_rtt_wr = addr[10:9];

if (odt_rtt_wr == 2'b00) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Dynamic ODT = Disabled", $time, cmd_string[cmd], bank);

dyn_odt_en = 0;

end else if ((odt_rtt_wr > 0) && (odt_rtt_wr < 3)) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d Dynamic ODT Rtt = %d Ohm", $time, cmd_string[cmd], bank, get_rtt_wr(odt_rtt_wr));

dyn_odt_en = 1;

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal Dynamic ODT = %d", $time, cmd_string[cmd], bank, odt_rtt_wr);

dyn_odt_en = 0;

end

// Reserved

if (ADDR_BITS>13 && addr[13:11] !== 0 && check_strict_mrbits) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved address bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

end

3 : begin

mpr_select = addr[1:0];

// MultiPurpose Register Select

if (mpr_select == 2'b00) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d MultiPurpose Register Select = Pre-defined pattern", $time, cmd_string[cmd], bank);

end else begin

if (check_strict_mrbits) $display ("%m: at time %t ERROR: %s %d Illegal MultiPurpose Register Select = %d", $time, cmd_string[cmd], bank, mpr_select);

end

// MultiPurpose Register Enable

mpr_en = addr[2];

if (!mpr_en) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d MultiPurpose Register Enable = Disabled", $time, cmd_string[cmd], bank);

end else if (mpr_en) begin

if (DEBUG) $display ("%m: at time %t INFO: %s %d MultiPurpose Register Enable = Enabled", $time, cmd_string[cmd], bank);

end else begin

$display ("%m: at time %t ERROR: %s %d Illegal MultiPurpose Register Enable = %d", $time, cmd_string[cmd], bank, mpr_en);

end

// Reserved

if (ADDR_BITS>13 && addr[13:3] !== 0 && check_strict_mrbits) begin

$display ("%m: at time %t ERROR: %s %d Illegal value. Reserved address bits must be programmed to zero", $time, cmd_string[cmd], bank);

end

end

endcase

if (dyn_odt_en && write_levelization)

$display ("%m: at time %t ERROR: Dynamic ODT is not available during Write Leveling mode.", $time);

init_mode_reg[bank] = 1;

mode_reg[bank] = addr;

tm_load_mode <= $time;

ck_load_mode <= ck_cntr;

end

end

REFRESH : begin

if (mpr_en) begin

$display ("%m: at time %t ERROR: %s Failure. Multipurpose Register must be disabled.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else if (|active_bank) begin

$display ("%m: at time %t ERROR: %s Failure. All banks must be Precharged.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else begin

if (DEBUG) $display ("%m: at time %t INFO: %s", $time, cmd_string[cmd]);

er_trfc_max = 0;

ref_cntr = ref_cntr + 1;

tm_refresh <= $time;

ck_refresh <= ck_cntr;

end

end

PRECHARGE : begin

if (addr[AP]) begin

if (DEBUG) $display ("%m: at time %t INFO: %s All", $time, cmd_string[cmd]);

end

// PRECHARGE command will be treated as a NOP if there is no open row in that bank (idle state),

// or if the previously open row is already in the process of precharging

if (|active_bank) begin

if (($time - tm_txpr < TXPR) || (ck_cntr - ck_txpr < TXPR_TCK))

$display ("%m: at time %t ERROR: tXPR violation during %s", $time, cmd_string[cmd]);

if (mpr_en) begin

$display ("%m: at time %t ERROR: %s Failure. Multipurpose Register must be disabled.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else begin

for (i=0; i<`BANKS; i=i+1) begin

if (active_bank[i]) begin

if (addr[AP] || (i == bank)) begin

for (j=0; j<=SELF_REF; j=j+1) begin

chk_err(SAME_BANK, i, j, cmd);

chk_err(DIFF_BANK, i, j, cmd);

end

if (auto_precharge_bank[i]) begin

$display ("%m: at time %t ERROR: %s Failure. Auto Precharge is scheduled to bank %d.", $time, cmd_string[cmd], i);

if (STOP_ON_ERROR) $stop(0);

end else begin

if (DEBUG) $display ("%m: at time %t INFO: %s bank %d", $time, cmd_string[cmd], i);

active_bank[i] = 1'b0;

tm_bank_precharge[i] <= $time;

tm_precharge <= $time;

ck_precharge <= ck_cntr;

end

end

end

end

end

end

end

ACTIVATE : begin

tfaw_cntr = 0;

for (i=0; i<`BANKS; i=i+1) begin

if ($time - tm_bank_activate[i] < TFAW) begin

tfaw_cntr = tfaw_cntr + 1;

end

end

if (tfaw_cntr > 3) begin

$display ("%m: at time %t ERROR: tFAW violation during %s to bank %d", $time, cmd_string[cmd], bank);

end

if (mpr_en) begin

$display ("%m: at time %t ERROR: %s Failure. Multipurpose Register must be disabled.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else if (!init_done) begin

$display ("%m: at time %t ERROR: %s Failure. Initialization sequence is not complete.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else if (active_bank[bank]) begin

$display ("%m: at time %t ERROR: %s Failure. Bank %d must be Precharged.", $time, cmd_string[cmd], bank);

if (STOP_ON_ERROR) $stop(0);

end else begin

if (addr >= 1<<ROW_BITS) begin

$display ("%m: at time %t WARNING: row = %h does not exist. Maximum row = %h", $time, addr, (1<<ROW_BITS)-1);

end

if (DEBUG) $display ("%m: at time %t INFO: %s bank %d row %h", $time, cmd_string[cmd], bank, addr);

active_bank[bank] = 1'b1;

active_row[bank] = addr;

tm_group_activate[bank[1]] <= $time;

tm_activate <= $time;

tm_bank_activate[bank] <= $time;

ck_group_activate[bank[1]] <= ck_cntr;

ck_activate <= ck_cntr;

end

end

WRITE : begin

if ((!rd_bc && blotf) || (burst_length == 4)) begin // BL=4

if (truebl4) begin

if (ck_cntr - ck_group_read[bank[1]] < read_latency + TCCD/2 + 2 - write_latency)

$display ("%m: at time %t ERROR: tRTW violation during %s to bank %d", $time, cmd_string[cmd], bank);

if (ck_cntr - ck_read < read_latency + TCCD_DG/2 + 2 - write_latency)

$display ("%m: at time %t ERROR: tRTW_DG violation during %s to bank %d", $time, cmd_string[cmd], bank);

end else begin

if (ck_cntr - ck_read < read_latency + TCCD/2 + 2 - write_latency)

$display ("%m: at time %t ERROR: tRTW violation during %s to bank %d", $time, cmd_string[cmd], bank);

end

end else begin // BL=8

if (ck_cntr - ck_read < read_latency + TCCD + 2 - write_latency)

$display ("%m: at time %t ERROR: tRTW violation during %s to bank %d", $time, cmd_string[cmd], bank);

end

if (mpr_en) begin

$display ("%m: at time %t ERROR: %s Failure. Multipurpose Register must be disabled.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else if (!init_done) begin

$display ("%m: at time %t ERROR: %s Failure. Initialization sequence is not complete.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else if (!active_bank[bank]) begin

if (check_strict_timing) $display ("%m: at time %t ERROR: %s Failure. Bank %d must be Activated.", $time, cmd_string[cmd], bank);

if (STOP_ON_ERROR) $stop(0);

end else if (auto_precharge_bank[bank]) begin

$display ("%m: at time %t ERROR: %s Failure. Auto Precharge is scheduled to bank %d.", $time, cmd_string[cmd], bank);

if (STOP_ON_ERROR) $stop(0);

end else if (ck_cntr - ck_write < burst_length/2) begin

$display ("%m: at time %t ERROR: %s Failure. Illegal burst interruption.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else begin

if (addr[AP]) begin

auto_precharge_bank[bank] = 1'b1;

write_precharge_bank[bank] = 1'b1;

end

col = {addr[BC-1:AP+1], addr[AP-1:0]}; // assume BC > AP

if (col >= 1<<COL_BITS) begin

$display ("%m: at time %t WARNING: col = %h does not exist. Maximum col = %h", $time, col, (1<<COL_BITS)-1);

end

if ((!addr[BC] && blotf) || (burst_length == 4)) begin // BL=4

col = col & -4;

end else begin // BL=8

col = col & -8;

end

if (DEBUG) $display ("%m: at time %t INFO: %s bank %d col %h, auto precharge %d", $time, cmd_string[cmd], bank, col, addr[AP]);

wr_pipeline[2*write_latency + 1] = 1;

ba_pipeline[2*write_latency + 1] = bank;

row_pipeline[2*write_latency + 1] = active_row[bank];

col_pipeline[2*write_latency + 1] = col;

if ((!addr[BC] && blotf) || (burst_length == 4)) begin // BL=4

bl_pipeline[2*write_latency + 1] = 4;

if (mpr_en && col%4) begin

$display ("%m: at time %t WARNING: col[1:0] must be set to 2'b00 during a BL4 Multipurpose Register read", $time);

end

end else begin // BL=8

bl_pipeline[2*write_latency + 1] = 8;

if (odt_in) begin

ck_odth8 <= ck_cntr;

end

end

for (j=0; j<(burst_length + 4); j=j+1) begin

dyn_odt_pipeline[2*(write_latency - 2) + j] = 1'b1; // ODTLcnw = WL - 2, ODTLcwn = BL/2 + 2

end

ck_bank_write[bank] <= ck_cntr;

ck_group_write[bank[1]] <= ck_cntr;

ck_write <= ck_cntr;

end

end

READ : begin

if (!dll_locked)

$display ("%m: at time %t WARNING: tDLLK violation during %s.", $time, cmd_string[cmd]);

if (mpr_en && (addr[1:0] != 2'b00)) begin

$display ("%m: at time %t ERROR: %s Failure. addr[1:0] must be zero during Multipurpose Register Read.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else if (!init_done) begin

$display ("%m: at time %t ERROR: %s Failure. Initialization sequence is not complete.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else if (!active_bank[bank] && !mpr_en) begin

if (check_strict_timing) $display ("%m: at time %t ERROR: %s Failure. Bank %d must be Activated.", $time, cmd_string[cmd], bank);

if (STOP_ON_ERROR) $stop(0);

end else if (auto_precharge_bank[bank]) begin

$display ("%m: at time %t ERROR: %s Failure. Auto Precharge is scheduled to bank %d.", $time, cmd_string[cmd], bank);

if (STOP_ON_ERROR) $stop(0);

end else if (ck_cntr - ck_read < burst_length/2) begin

$display ("%m: at time %t ERROR: %s Failure. Illegal burst interruption.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else begin

if (addr[AP] && !mpr_en) begin

auto_precharge_bank[bank] = 1'b1;

read_precharge_bank[bank] = 1'b1;

end

col = {addr[BC-1:AP+1], addr[AP-1:0]}; // assume BC > AP

if (col >= 1<<COL_BITS) begin

$display ("%m: at time %t WARNING: col = %h does not exist. Maximum col = %h", $time, col, (1<<COL_BITS)-1);

end

if (DEBUG) $display ("%m: at time %t INFO: %s bank %d col %h, auto precharge %d", $time, cmd_string[cmd], bank, col, addr[AP]);

rd_pipeline[2*read_latency - 1] = 1;

ba_pipeline[2*read_latency - 1] = bank;

row_pipeline[2*read_latency - 1] = active_row[bank];

col_pipeline[2*read_latency - 1] = col;

if ((!addr[BC] && blotf) || (burst_length == 4)) begin // BL=4

bl_pipeline[2*read_latency - 1] = 4;

if (mpr_en && col%4) begin

$display ("%m: at time %t WARNING: col[1:0] must be set to 2'b00 during a BL4 Multipurpose Register read", $time);

end

end else begin // BL=8

bl_pipeline[2*read_latency - 1] = 8;

if (mpr_en && col%8) begin

$display ("%m: at time %t WARNING: col[2:0] must be set to 3'b000 during a BL8 Multipurpose Register read", $time);

end

end

rd_bc = addr[BC];

ck_bank_read[bank] <= ck_cntr;

ck_group_read[bank[1]] <= ck_cntr;

ck_read <= ck_cntr;

end

end

ZQ : begin

if (mpr_en) begin

$display ("%m: at time %t ERROR: %s Failure. Multipurpose Register must be disabled.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else if (|active_bank) begin

$display ("%m: at time %t ERROR: %s Failure. All banks must be Precharged.", $time, cmd_string[cmd]);

if (STOP_ON_ERROR) $stop(0);

end else begin

if (DEBUG) $display ("%m: at time %t INFO: %s long = %d", $time, cmd_string[cmd], addr[AP]);

if (addr[AP]) begin

zq_set = 1;

if (init_done) begin

ck_zqoper <= ck_cntr;

end else begin

ck_zqinit <= ck_cntr;

end

end else begin

ck_zqcs <= ck_cntr;

end

end

end

NOP: begin

if (in_power_down) begin

if (($time - tm_freq_change < TCKSRX) || (ck_cntr - ck_freq_change < TCKSRX_TCK))

$display ("%m: at time %t ERROR: tCKSRX violation during Power Down Exit", $time);

if ($time - tm_cke_cmd > TPD_MAX)

$display ("%m: at time %t ERROR: tPD maximum violation during Power Down Exit", $time);

if (DEBUG) $display ("%m: at time %t INFO: Power Down Exit", $time);

in_power_down = 0;

if ((active_bank == 0) && low_power) begin // precharge power down with dll off

if (ck_cntr - ck_odt < write_latency - 1)

$display ("%m: at time %t WARNING: tANPD violation during Power Down Exit. Synchronous or asynchronous change in termination resistance is possible.", $time);

tm_slow_exit_pd <= $time;

ck_slow_exit_pd <= ck_cntr;

end

tm_power_down <= $time;

ck_power_down <= ck_cntr;

end

if (in_self_refresh) begin

if (($time - tm_freq_change < TCKSRX) || (ck_cntr - ck_freq_change < TCKSRX_TCK))

$display ("%m: at time %t ERROR: tCKSRX violation during Self Refresh Exit", $time);

if (ck_cntr - ck_cke_cmd < TCKESR_TCK)

$display ("%m: at time %t ERROR: tCKESR violation during Self Refresh Exit", $time);

if ($time - tm_cke < TISXR)

$display ("%m: at time %t ERROR: tISXR violation during Self Refresh Exit", $time);

if (DEBUG) $display ("%m: at time %t INFO: Self Refresh Exit", $time);

in_self_refresh = 0;

ck_dll_reset <= ck_cntr;

ck_self_refresh <= ck_cntr;

tm_self_refresh <= $time;

tm_refresh <= $time;

end

end

endcase

if ((prev_cke !== 1) && (cmd !== NOP)) begin

$display ("%m: at time %t ERROR: NOP or Deselect is required when CKE goes active.", $time);

end

if (!init_done) begin

case (init_step)

0 : begin

if ($time - tm_rst_n < 500000000 && check_strict_timing)

$display ("%m at time %t WARNING: 500 us is required after RST_N goes inactive before CKE goes active.", $time);

tm_txpr <= $time;

ck_txpr <= ck_cntr;

init_step = init_step + 1;

end

1 : if (dll_en) init_step = init_step + 1;

2 : begin

if (&init_mode_reg && init_dll_reset && zq_set) begin

if (DEBUG) $display ("%m: at time %t INFO: Initialization Sequence is complete", $time);

init_done = 1;

end

end

endcase

end

end else if (prev_cke) begin

if ((!init_done) && (init_step > 1)) begin

$display ("%m: at time %t ERROR: CKE must remain active until the initialization sequence is complete.", $time);

if (STOP_ON_ERROR) $stop(0);

end

case (cmd)

REFRESH : begin

if ($time - tm_txpr < TXPR)

$display ("%m: at time %t ERROR: tXPR violation during %s", $time, cmd_string[SELF_REF]);

for (j=0; j<=SELF_REF; j=j+1) begin

chk_err(DIFF_BANK, bank, j, SELF_REF);

end

if (mpr_en) begin

$display ("%m: at time %t ERROR: Self Refresh Failure. Multipurpose Register must be disabled.", $time);

if (STOP_ON_ERROR) $stop(0);

end else if (|active_bank) begin

$display ("%m: at time %t ERROR: Self Refresh Failure. All banks must be Precharged.", $time);

if (STOP_ON_ERROR) $stop(0);

end else if (odt_state) begin

$display ("%m: at time %t ERROR: Self Refresh Failure. ODT must be off prior to entering Self Refresh", $time);

if (STOP_ON_ERROR) $stop(0);

end else if (!init_done) begin

$display ("%m: at time %t ERROR: Self Refresh Failure. Initialization sequence is not complete.", $time);

if (STOP_ON_ERROR) $stop(0);

end else begin

if (DEBUG) $display ("%m: at time %t INFO: Self Refresh Enter", $time);

if (feature_pasr)

// Partial Array Self Refresh

case (pasr)

3'b000 : ;//keep Bank 0-7

3'b001 : begin if (DEBUG) $display("%m: at time %t INFO: Banks 4-7 will be lost due to Partial Array Self Refresh", $time); erase_banks(8'hF0); end

3'b010 : begin if (DEBUG) $display("%m: at time %t INFO: Banks 2-7 will be lost due to Partial Array Self Refresh", $time); erase_banks(8'hFC); end

3'b011 : begin if (DEBUG) $display("%m: at time %t INFO: Banks 1-7 will be lost due to Partial Array Self Refresh", $time); erase_banks(8'hFE); end

3'b100 : begin if (DEBUG) $display("%m: at time %t INFO: Banks 0-1 will be lost due to Partial Array Self Refresh", $time); erase_banks(8'h03); end

3'b101 : begin if (DEBUG) $display("%m: at time %t INFO: Banks 0-3 will be lost due to Partial Array Self Refresh", $time); erase_banks(8'h0F); end

3'b110 : begin if (DEBUG) $display("%m: at time %t INFO: Banks 0-5 will be lost due to Partial Array Self Refresh", $time); erase_banks(8'h3F); end

3'b111 : begin if (DEBUG) $display("%m: at time %t INFO: Banks 0-6 will be lost due to Partial Array Self Refresh", $time); erase_banks(8'h7F); end

endcase

in_self_refresh = 1;

dll_locked = 0;

end

end

NOP : begin