W5300网口芯片的FPGA控制协议流程

一、

系统硬件构成与设计

1.1 W5300芯片介绍

W5300是一款0.18um CMOS工艺的单芯片器件,内部集成10/100M以太网控制器,MAC和TCP协议栈。W5300主要应用于高性能嵌入式领域,如多媒体数据流服务。通过一个集成有TCP/IP协议的10/100M的以太网MAC和PHY的单芯片可以非常简单快捷的实现Internet连接。W5300的数据通信存储器扩展到128K字节,与MCU的接口支持16位数据总线,用户可以使用8个独立的端口进行高速数据通信。

每一个端口的通信数据存储器可以分配0~64K字节,可以根据端口通信数据吞吐量动态调整期分配。也可以通过配置辅助的寄存器使系统具有更高的性能。TCP/IP内核是完全基于网络协议处理技术进行硬件逻辑化。因此可以更好的通过程序进行控制。

在TCP层实现数据传输协议,它支持TCP客户端模式和TCP服务器模式。

1.2硬件接口设计

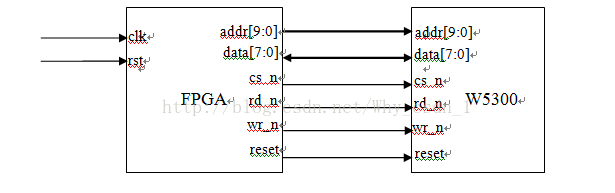

W5300与控制器的接口模式有直接寻址模式和间接寻址模式,数据总线分为16位和8位总线两种方式。在本设计中采用直接寻址与8位数据总线模式。因此BIT16EN引脚拉低,物理层使用W5300内部的PHY模式,并配置为全功能自动握手运行模式,即TEST_MODE[3:0]和OP_MODE[2:0]均配置为低电平。W5300硬件接口方式如图1所

图1 W5300硬件接口连接原理图

由FPGA内部逻辑产生地址线、数据线、片选、读写使能信号,并指向W5300芯片。由于W5300不支持上电复位,所以在上电后由FPGA接口逻辑产生复位信号。

1.2.1 W5300接口逻辑设计

W5300接口逻辑由复位逻辑与时序控制逻辑组成。复位逻辑产生W5300复位信号以及时序控制逻辑的复位信号;时序控制逻辑按照W5300的读写寄存器时序完成对寄存器的读写访问。

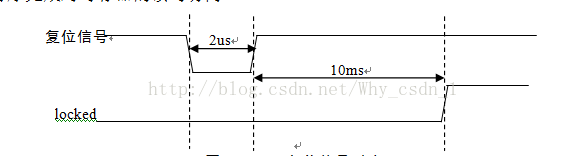

图2 W5300复位信号时序

W5300的复位信号拉低至少持续2us,为了使W5300系统稳定,在复位信号拉高后至少持续10ms。本系统复位信号拉低持续3.2us,再复位后持续了11ms后,W5300开始正常工作。

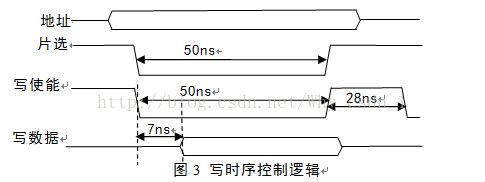

图3 写时序控制逻辑

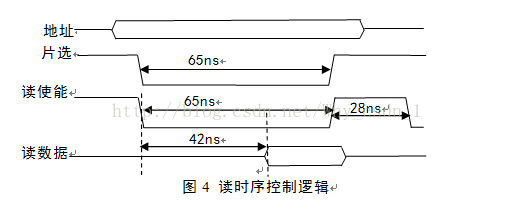

图4 读时序控制逻辑

W5300读写时序如图3、4所示,片选与读写使能均为低电平有效,当写数据时,在给出写使能信号至少7ns后写入到寄存器中,片选拉低至少50ns;读数据时,在读使能信号拉低至少42ns后读数据,在本系统中,采用XILLINX Virtex5的开发板,时钟信号为100Mhz,所以读使能拉低时间为70ns,拉高30ns,在给出读使能50ns后,进行数据读取。写使能信号拉低50ns,拉高30ns,在写使能信号有效20ns后,将数据写入W5300。

二 系统软件设计

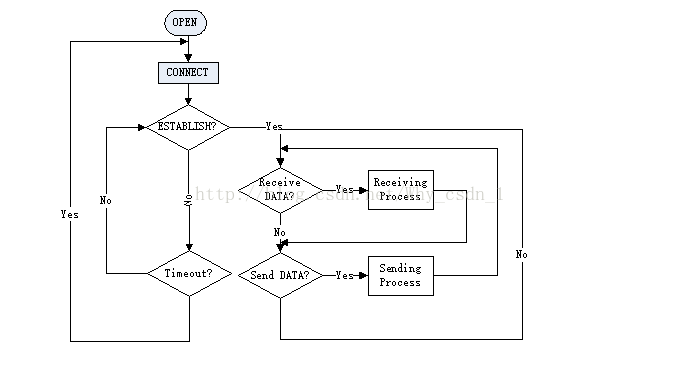

本系统主要采用客户端模式,整体设计流程如下图所示:

图5 整体控制流程

2.1 W5300寄存器介绍及初始化配置

本系统由直接寻址模式,8位数据总线组成,W5300的寄存器由模式寄存器、通用寄存器和端口寄存器组成。按照W5300配置流程,首先进行通用寄存器、端口寄存器配置,然后进行端口的建立连接,完成初始化配置。

W5300初始化通过3步完成:

1. 设置主机接口模式为TCP模式,总线位宽为8bit位宽。

2. 设置基本网络信息,主要设置MAC地址,子网掩码,网关,以及源IP地址。当连接建立成功后,设置重传时间和重复发送次数,用于数据包的发送失败和重复发送。

3. 定义内部RX/TX存储器大小,以及每一个SOCKET的TX/RX存储器大小。W5300包括16个8K字节存储单元,这些存储单元依次映射在128K存储空间,128k存储空间分为发送存储器和接受存储器。内部发送存储器和接受存储器以8K字节为存储单元分布在128K字节空间。内部TX/RX存储器可以再0~64字节空间以1K字节为单元重新分配给每个SOCKET。

初始化设置完成后,W5300可以响应Ping请求。

2.2 数据通信

完成初始化配置后,可以通过每一个套接字设置不同的通信方式,本系统采用TCP通信协议,在TCP模式,首先通过IP地址和端口号与对端建立端口连接,通过连接的端口发送和接收数据。建立端口连接有TCP服务器和TCP客户端之分,区分它们的方法是谁首先发送连接请求,本系统由W5300发送连接请求(SYN)到服务器,服务器响应W5300且同时回复已经打开,W5300在收到服务器的回复后响应服务器,完成三次握手的机制,从而开始进行数据通信。

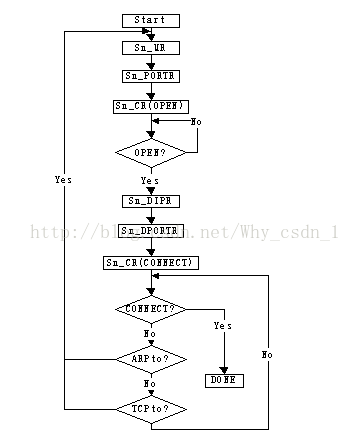

2.2.1 端口初始化

为了实现TCP通信,需要对SOCKET进行初始化并打开SOCKET。通过Sn_MR寄存器和Sn_PORTR寄存器分别设置通信协议与本机端口号,然后执行打开命令(Sn_CR),通过状态寄存(Sn_SSR)判断,如果状态寄存器变为SOCK_INIT,TCP端口打开成功。打开成功后,设置目的IP地址(Sn_DIPR)与目的端口号(Sn_DPORTR),然后执行建立连接指令,如果状态寄存器变为ESTABLISHED状态,则建立连接成功。需要注意的是,在建立连接过程中,可能会出现ARP超时或者TCP超时,如果出现超时,则必须对端口进行重新配置。具体流程配置如图6所示。

端口初始化完成,在端口进行数据通信开始后,当端口没有数据收发时,为了保证端口的稳定连接,在每隔40s发送一次心跳包,通过Sn_KPALVTR寄存器配置心跳包。

图6 端口初始化配置流程

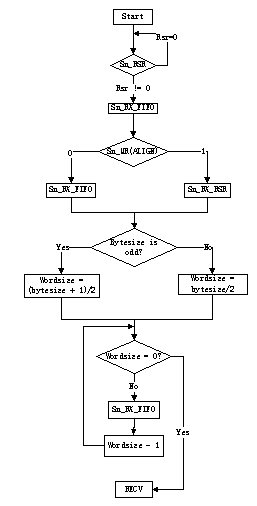

2.2.2 数据接收

在端口成功建立连接后,将进行数据的接收流程,在接收数据流程中,当检测到RX存储器中具有数据后,即接收数据长度寄存器(RX_RSR)不在为0,表示接收到数据。通过读取Sn_MR寄存器的ALIGN位,判断字节长度。当ALIGN位为0时,主机首先通过读取Sn_RX_FIFO确定所接收到字节的长度;当ALIGN位为1时,则直接读取Sn_RX_RSR确定RX缓存区字节长度。然后将数据依次通过Sn_RX_FIFO从RX缓存区读出,当数据全部读取完成后,执行RECV命令,完成数据的接收。数据接收流程如图7所示。

图7 数据接收流程控制

需要注意的是,当端口只进行数据接收而没有发送时,主机不能快速处理数据会导致内部RX缓存区溢出,此时W5300窗口尺寸为0。主机必须将RX缓存区数据进行发送处理后,才能继续进行数据的接收。

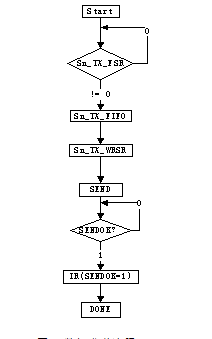

2.2.3 数据发送

数据通过Sn_TX_FIFO写入到内部TX存储器后,W5300试着将数据发送到对端。发送数据的大小不能比分配给高SOCKET的内部TX存储空间大。首先,需要查询端口TX存储器的剩余空间字节数,当TX存储器由足够的缓存区时,方可将要发送的数据通过Sn_TX_FIFO依次写入到TX存储器中,然后将数据长度写入到Sn_TX_WRSR寄存器中。

当执行命令前,如果不是第一次发送数据,需要查询上一次SEND命令是否执行完成,通过中断寄存器IR(SENDOK)来判断,当SENDOK标志位为1时,说明发送完成,向中断寄存器写入1,进行清除中断操作。然后执行SEND命令。

操作流程如图8所示

图8 数据发送流程

当数据发送完成时,会跳向下一个端口进行数据收发,当完成端口7的数据收发后,会继续从端口1重新开始进行数据的收发,采用这样轮询的方式直到数据全部收发完成停止。