{ 第三部分 }

DDR总线的设计、调试和验证

在计算机架构中,DDR作为程序运算的动态存储器,面对如高性能计算、图形计算、移动计算、工业应用等领域的要求,发展出DDR4,以及用于图形计算的GDDR5, HBM2,面向移动计算的低功耗LPDDR4等标准。

处理器的运算速度越来越快,DDR的性能也要求越来越高,明显的趋势是DDR总线工作频率持续提升, DDR4 达到3.2GT/s, 用于智能手机等低功耗场合的LPDDR4速率甚至超越了DDR4,最高达到4.2GT/s,JEDEC在年中的论坛中提出未来的DDR5工作速率将达到6.4GT/s,由于速率的提升,DDR5中将可能考虑在接收端采用多阶DFE均衡器,而在强调性能的图形计算领域,规划中的GDDR6的工作速率可能会达到16GT/s。另一方面由于能耗比的要求,DDR标准在演进中工作电压持续走低,如LPDDR4X的工作电压降低至0.6V。

DDR总线采用源同步的技术,多比特并行通信的机制,总线中会存在同步开关噪声和串扰等问题;由于信号速率持续提升单个比特位宽收窄,导致时序裕度变的很紧张,抖动问题也越发明显;而工作电压的降低,噪声和电源完整性的问题也变得非常显著。DDR4总线既有并行总线存在的问题,也要面临如同高速SERDES设计中存在的挑战,可以说是在数字系统中最为复杂的一环,如果不能保证DDR总线的可靠运行,有可能会导致整个硬件系统的崩溃。

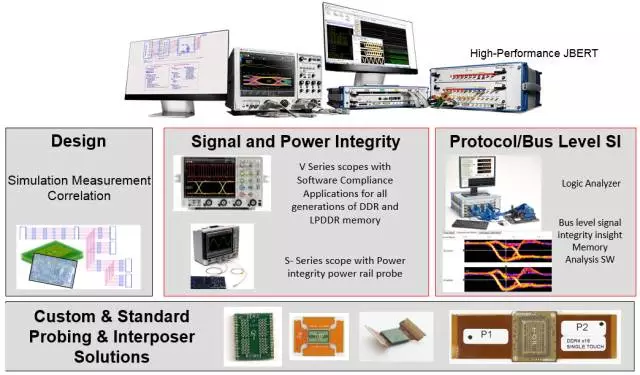

针对这些问题,是德科技提供了从DDR4总线的设计仿真和分析,到系统上电后DDR4信号完整性验证、时序验证、眼图轮廓测试、电源完整性验证,以及总线时序一致性分析,故障定位,性能统计等等完整的解决方案。(如下图所示)

JEDEC协会定义的DDR4信号特性主要包括以下主要内容↘↘↘

Electrical

-

VIH/VIL,VOH/VOL

-

Overshoot/undershoot

-

Crossingpoint

Timing

-

Pre/Postamble timing

-

DQS/DQ/CLKDelta time

Eyediagram

-

RxInput Mask

其中电气特性和时序特性基本与之前DDR3等要求比较类似,眼图这一项是随着信号速率的提升,新增加的一个要求。可能有读者会问,以前DDR3或之前的测试,示波器软件也有眼图测试,到了DDR4对于眼图测试要求有什么区别吗?(篇幅所限,以上问题本文不再做进一步的详细解释,有兴趣的同学可以 点击下载>>>【DDR4眼图测试】全文了解。)

是德科技ADS仿真软件的DDR4总线仿真器,提供了统计眼图分析的功能,能够在短时间内统计计算在极低误码率(1e-16)下的DQ眼图,根据规范判断模板是否违规。另外基于总线的仿真,也很易于仿真基于串扰因素下的眼图质量。

基于示波器的DDR4信号实测,可以利用大家熟悉的InfiniiScan区域触发功能,很容易分离出“写”信号,再通过Gating功能对Burst写信号做时钟恢复和眼图重建,再进行Eye Contour测量,并验证1e-16误码率下的眼图模板是否违规。如果是使用一致性测试软件,就不用手动操作,软件会自动跟踪和分离波形并实现眼图测试(如下图所示)

DDR4做测试时,由于BGA信号难以探测,是德科技提供了N2114A/N2115A等DDR4 Interposer,将BGA下方的信号引到Interposer外围,方便探头焊接。

最后,对于物理层无论是仿真还是一致性测试软件得到的数据,都可以通过数据分析工具N8844A导入到云端,通过可视化工具,生成统计分析表格,对比性分析高低温、高低电压等极端情况下不同的测试结果,比较不同被测件异同。为开发测试部门提供灵活和有效的大数据分析平台。

以上,我们介绍了DDR4总线物理层仿真测试和协议层的测试方案,借助仿真软件、示波器和逻辑分析仪对DDR4总线分析调试的主要方法。

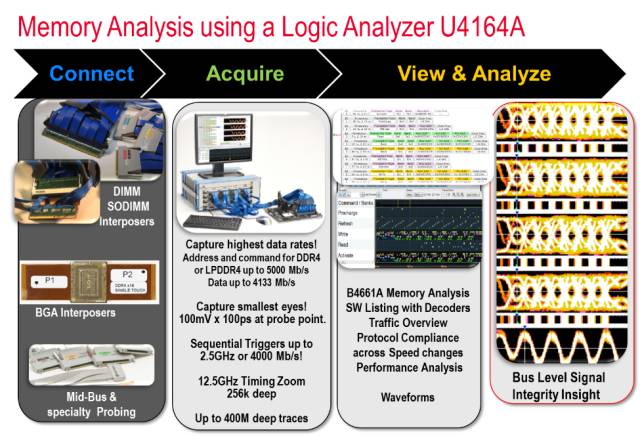

再通过逻辑分析仪的内存软件解析DDR总线的操作和分析性能,可以分析出由于系统中集中的读操作,以及LPDDR4的速率切换导致了电源电压的波动,以及特定命令操作导致的电压跌落现象。(详细技术细节,请点击下载>>>【DDR4眼图测试】进一步了解。)

{ 第四部分 }

NAND memory 颗粒

和 controller 之间的高速接口调试

NANDmemory 颗粒和其controller 之间的高速接口主要分以下几种↘↘↘

M-PHY(UFS)

SD UHS-II

eMMC

ONFi(Open NAND FLASH Interface)

以UFS为例,让我们分别来看这类高速接口的

1、物理层一致性测试

发射端

接收端

接口及互连S参数和阻抗

2、协议层分析和测试

UFS2.1总线的分析验证方法

随着智能手机的爆炸式增长,移动存储技术也发生着巨大的变化,从早期手机内置存储器并且开放MicroSD存储卡接口,到现在多数手机只有内部固定存储器。

这些年eMMC技术被广泛使用,最新eMMC5.1标准理论最高传输速率可以达到400MB/s,但最近移动设备中越来越多采用了JEDEC协会定义的UFS协议。

UFS2.1协议基于MIPI M-PHY G3的物理层标准,使用两个通道,与eMMC比较,简单来说是将从并行改为串行架构,收发双向全双工传输,两路传输吞吐速率可以达到11.6Gbps。除了高速率性能,另外UFS具有很好的功耗性能,在移动领域有替代eMMC的趋势。我在这里总结了一下UFS与eMMC的主要差异:

| UFS | eMMC | |

|---|---|---|

| 当前标准 |

2.1 | 5.1 |

| 物理层 |

M-PHY G3 |

N/A |

| 链路层 |

UniPro v1.6 |

N/A |

| 接口 |

串行 |

并行 |

| 通道数 |

2 |

8 (11 w/ strobe) |

| 双工 |

全双工 |

半双工 |

| 时钟架构 |

嵌入时钟 |

源同步 |

| 理想吞吐速率 |

5.8Gbps x 2 |

HS400 max 3.2Gbps |

| 编码 |

8b/10b, PWM |

N/A |

| 均衡 |

TX & RX (G4) |

N/A |

| 下一代标准 |

UFS3.0, M-PHY G4 11.6Gbps |

N/A |

| 一致性认证 |

UFSA:

MIPI/UNH-IOL:

|

No compliance program |

>>> UFS的物理层测试方案

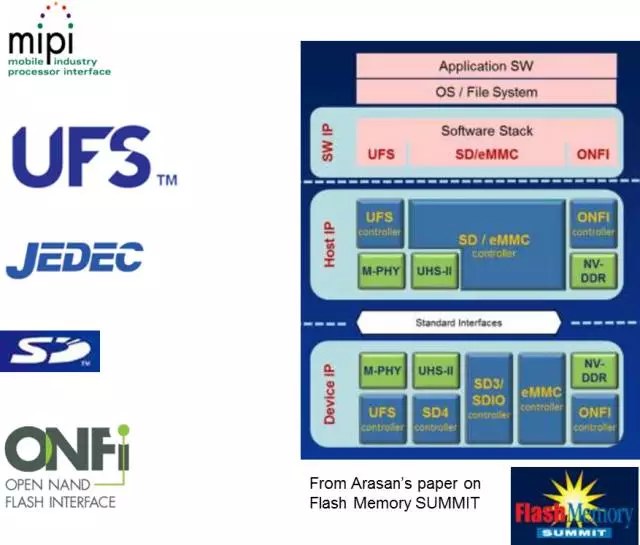

UFS采用分层结构,底层物理层采用MIPI联盟的M-PHY标准,数据链路层为UniPro,再上层协议层采用JEDEC协会定义的UFS协议。

UFS2.1架构如下图所示↘↘↘

▲ 上图引用自Arasan网站

>>> M-PHY物理层主要有如下主要的特点

每个信号通路是单向传输,信号采用差分传输机制,信号有高速HS和低速LS两种模式,高速信号采用8b/10b编码,使用PLL类型端时钟恢复,在突发的开始需要同步信号;低速信号则使用PWM调制方式。M-PHY有两种电压摆幅大幅度LA和小幅度SA,可以工作在端接模式和非端接模式,后一种可以在低功耗要求时使用。

M-PHY一致性测试规范包括了发射端,接收端,接口及互连S参数和阻抗三部分内容。

>>> 发射端测试方案如下:

详情请下载相关文档查看,点击下载>>>

>>> 接收端测试方案如下:

接收端的测试难点有几个方面:

-

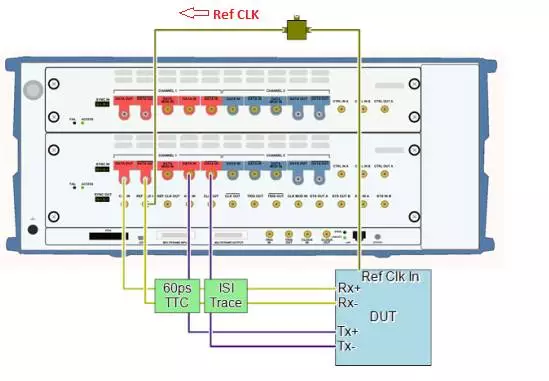

接收测试的原理是,激励压力信号到接收端,环回后测试误码率,压力信号通常包括随机抖动Rj,确定性抖动包括ISI和正弦抖动Sj扫描,激励源允许加入去加重,环回后测试设备需要通过CDR恢复时钟,进而测试误码率。是德科技M8020A误码仪集成经过校准的Rj,BUJ, PJ,SSC等抖动源,内置可调节ISI,可以直接按照规范规定的CH1/CH2的插入损耗要求生成ISI。内置CDR从环回信号恢复时钟测试误码率。

-

在做UFS接收测试时,芯片有可能内置参考时钟如19.2MHz不能外部输入,这就要求误码仪与被测芯片提供的时钟同步,对于G3的信号速率5.8Gb/s,要求内部倍频304倍,如果是G4的速率11.6Gb/s,需要倍频608倍,M8020A的0G6选件可以直接外部参考时钟输入倍频后产生G3/G4要求的速率信号激励给被测件。

-

CTS除了要求接收容忍度测试之外,也会测试2.1.6 – HS-RXLane-to-Lane Skew (TL2L-SKEW-HS-RX),这一项是要求测试接收端的通道与通道间对skew的容忍度,这就要求激励源有2个通道,M8020A误码仪可以支持4通道16.2Gbps的发生和误码检测通道。

>>> 互连S参数和阻抗测试方案:

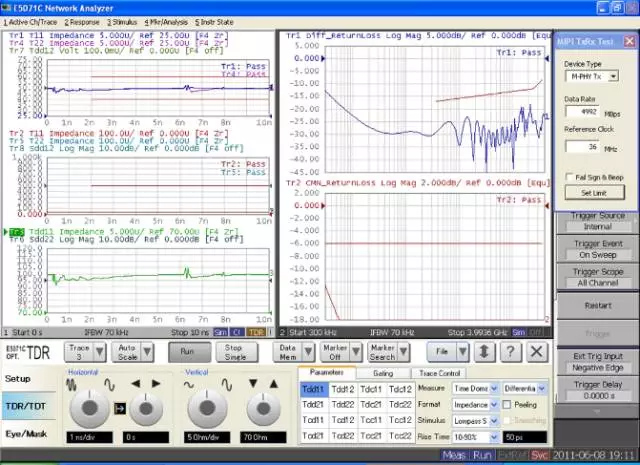

需要注意的是测试SDD21回波损耗的时候,被测件需要在工作状态并发出CRPAT码型的情况下做测试,TDR需要加入大量平均以减少被测信号发射波形的影响,这种测试推荐使用网络仪完成,可以调整发射功率和减少IFBW减少DUT发射信号对测量的影响,是德科技VNA E5071C带有TDR选件功能,可以从频域到时域实现完整的测试要求。

>>> UFS协议层分析和测试方案:

上图展示了是德科技U4431A UFS协议分析仪和捕获分析UFS链路协议的界面,U4431A支持M-PHY G3速率等级,采集深度16GB,可以支持双向各4个lane。

{ 第五部分 }

SSD高速接口的设计与验证

SSD是Solid State Drive也就固态盘的简写,作用如同传统硬盘,在系统掉电后,仍可以保持存储数据和程序。当然也有Intel美光等公司开发基于高速固态存储器技术3DXpoint也可以用于动态访问应用,这里由于篇幅所限,不在本文的讨论范围之内。

相较于机械硬盘,SSD访问速度大幅提升,也有噪音低、不怕碰撞等优点。从这些年的发展来看,SSD容量大幅度提升,成本也逐步降低,在消费领域或者企业市场已经有很大的普及。

现在的SSD多数采用TLC或MLC NANDFlash作为存储介质,除了NAND存储器颗粒之外,在SSD架构中,通常包括SSD控制器实现存储器的访问控制、缓冲器管理和特定的算法,也包括DDR 存储器实现数据缓冲和计算,以及与主机通信的的高速接口。对于DDR的测试方案,前面我们做了介绍,这一部分,我们主要来讨论一下高速接口的部分。

▲ 摘自Coding forSSDs – Part 2: Architecture of an SSD and Benchmarking

SSD控制器主要接口类型的包括PCIe, SAS, SATA, USB等,这里我总结了这几种接口技术的主要差别。

由于标准PCIe和SAS接口技术的高性能和扩展性,一般更多用于企业应用,而SATA和USB接口通常用于个人消费领域。

从使用的接口类型来看,PCIe协会PCISIG定义了除标准接口之外,还支持包括U.2, SATA Express以及m.2接口,并在最近也开发定义了OCulink的电缆接口。从这几种标准来看,以PCIe3.0为代表,采用了更加复杂的编码格式,以提升传输效率,另外发射接收端均衡能力也有很大提升,比如PCIe3.0在规范中定义了链路均衡训练机制,RC和EP芯片通过链路协商调整预加重和接收均衡,使得系统误码率维持在低水平。

首先我们先来了解PCIe总线的情况。2017年10月,PCISIG正式发布了PCIe4.0基础规范1.0版本,这是PCIe规范发展的一个重要里程碑,另外PCIe协会预计会在2019年正式发布PCIe5.0规范。PCIe4.0的传输速度比3.0加倍,达到16GT/s,相信在未来陆续会有支持4.0的CPU、外设产品陆续发布。当然对于NVMe协议来说,短期来说主流还是基于PCIe3.0,未来也有可能有支持4.0的产品。

下面是PCIe3.0/4.0 NVMe SSD设备的发射端和接收端测试方案框图

其中发射端展示的是NVMe设备通过矩阵开关实现2路信号的自动化实测连接图,被测件通过PCIe3.0测试夹具CBB3,将被测件的两路或更多路信号连接到Keysight U3020矩阵开关,再将公共端口差分连接到是德科技Z系列或V系列示波器,通过示波器的Aux Out输出端口经过Balun连接到测试夹具的Rx0,由软件控制产生100MHz时钟触发被测件切换码型和preset。对于NVMe设备接收端测试,M8020A具有极高集成度,内置8阶发射端去加重,内置共模差模干扰,接收均衡,CDR,并具有链路协商机制,如图所示,整个链接环境非常简化,就可以完成接受容忍度测试,并且M8020A也是PCISIG官方推荐的链路均衡测试方案。

对于U.2(SFF-8639)接口,PCISIG发布了一致性测试夹具,下图展示了U.2接口的NVMe SSD卡的发射机测试连接实物图。可以使用SigTest进行参数测量,也可以使用Z或V系列示波器内部的PCIe一致性测试软件N5393F,支持U.2 End Point测试模式,实现U.2参数的自动化一致性测试。

>>> PCIe和NVMe协议测试

U4301B协议分析仪平台,支持PCIe3.0协议解析,支持LTSSM状态机分析,解析EQ链路协商的过程;并且支持NVMe,AHCI等事物层的解码;统计PCIe总线的性能分析。这个分析平台可以支持标准PCIe x 1到 x 16插槽,也支持焊接方式,以及M.2和U.2接口卡的探测。

另外,是德科技的U4305B PCIe训练器可以模拟PCIe3.0的主设备或从设备,训练对端被测件,可以进行LTSSM测试,完成PCIe3.0官方的协议一致性测试。另外,针对NVMe,U4305B可以模拟NVMe主设备,产生NVMe会话,发送NVMe命令,与被测件通信,完成NVMe的一致性测试。是德科技也提供PCIe备板设备N5316A,将U4305B和被测件NVMeSSD插卡都插在备板上实现相关的测试。

>>> SAS TX/RX 测试方案

M8020A可以配置两通道码型发生功能,在Tx测试时可以使用双通道合路产生OOB信号, Rx测试内置ISI可以模拟规范要求的外部ISI损耗要求,并且利用第二通道产生SAS要求的串扰信号。

>>> SATA TX/RX测试方案

下图简化的Tx测试可以强制DUT发送指定的测试码型,也可以利用M8020A误码仪作为BIST信号发生器,训练DUT进入环回并发射指定测试码型,完成自动化的测试。

>>> USB3.1/3.2测试方案

这里展示了越来越普及的Type C接口方式,USB3.1Tx/Rx测试方案,其中N7015A是Type C接口测试夹具,N7018A夹具支持PD和AltMode,并且支持USB3.1 SCD和LBPM的LFPS信号的生成和握手,完成Tx的参数测试。对于Rx测试,M8020A内置ISI功能,可以模拟USB协会规范定义的传输参考通道的插损模型,实现精简连接环境下的Rx接收容忍度测量,并且M8020A也支持CTS中要求的LFPSRx容忍度测量。