Vivado 时序分析(理论篇) 卷一

文章目录

- 引言

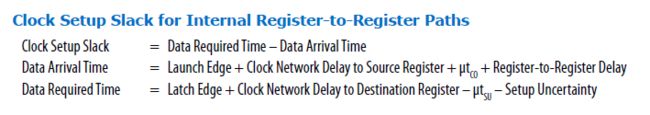

- 1、建立余量

- 2、建立时间余量的Vivado软件分析

- 3、保持时间

- 4、保持时间余量的Vivado软件分析

引言

在之前我的文章中,已经写过时序分析,但当时仅解决了step slack的问题,为了加深进一步的理解,随着资料的不断增多,现在,重新进一步整理,当然这一次整理将是干货的归纳,并且纳入IC学习路线一文中,为IC中的PT工具的时序分析先铺垫道路。

参考文章:https://blog.csdn.net/ciscomonkey/article/details/88046646

1、建立余量

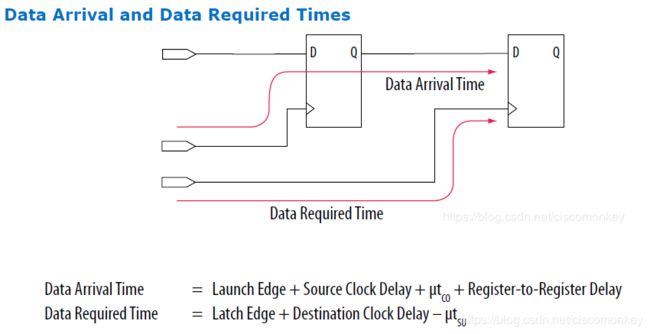

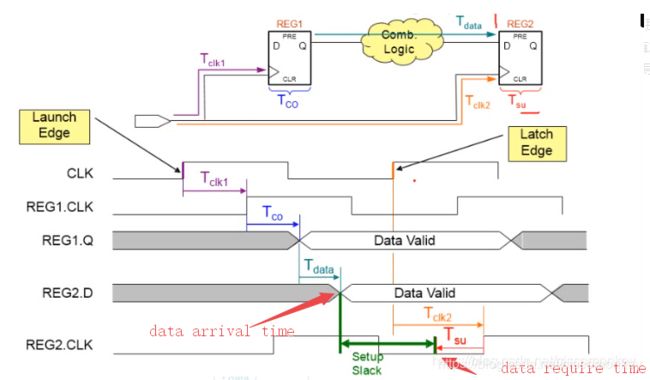

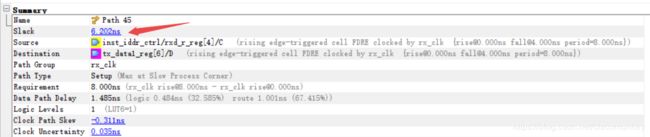

从图中可以看出,data arrival time 的时间点和data require time的时间点,只要两个相减,就是setup slack的值。并且需要保证slack>0.

而Fmax的值=1/(Tcycle -setup slack)

关于这个Fmax的理解:如果要让时钟可以快,更快,更快,显然,setup slack的余量更加充足,更容易让时钟更快,如果slack足够充足,我可以把Tsu这一段整体往前移动,移动,从而时钟的上升沿更快的到来,然而,想一下,如果slack很小很小,你想把Tsu往前提,也提不了,所以时钟快不起来。如果以极限来考虑,也就是说,我可以最多将Tsu提前slack这么一个长度,因此,得到Fmax的公式。

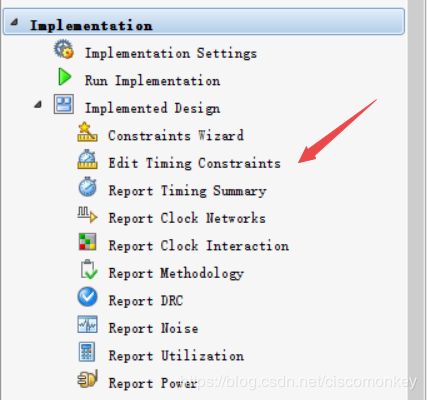

2、建立时间余量的Vivado软件分析

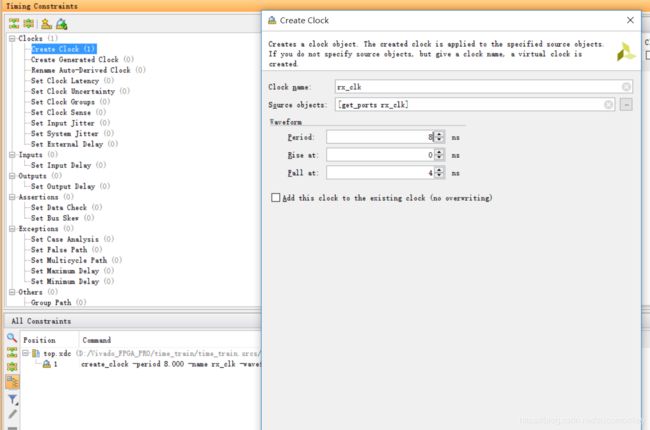

在实现或者综合后,点击编辑时序约束

在进行时序约束前,需要分配管脚,否则时序分析是没有意义的。如下图所示,创建时钟约束。如果系统中使用了PLL,就没必要设置时钟约束,因为系统已经知道了你的时钟。

现在需要重新编译。重新编译后,在Timing summary中。

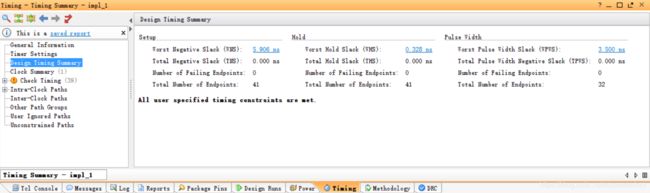

如下图所示,最糟糕的情况下,slack还有5.906ns的余量,而所有负的salck为0,是没有的。

WNS 代表最差负时序裕量 (Worst Negative Slack)

TNS 代表总的负时序裕量 (Total Negative Slack)(所有path-slack 加起来),也就是负时序裕量路径之和。

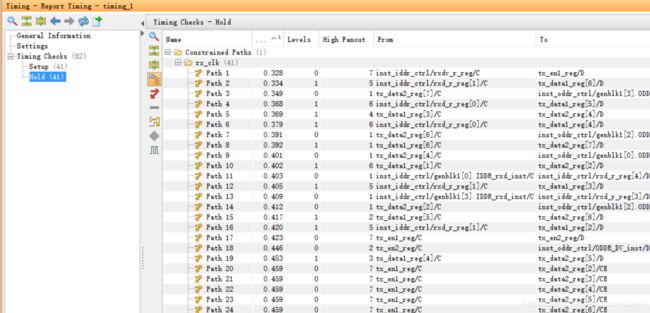

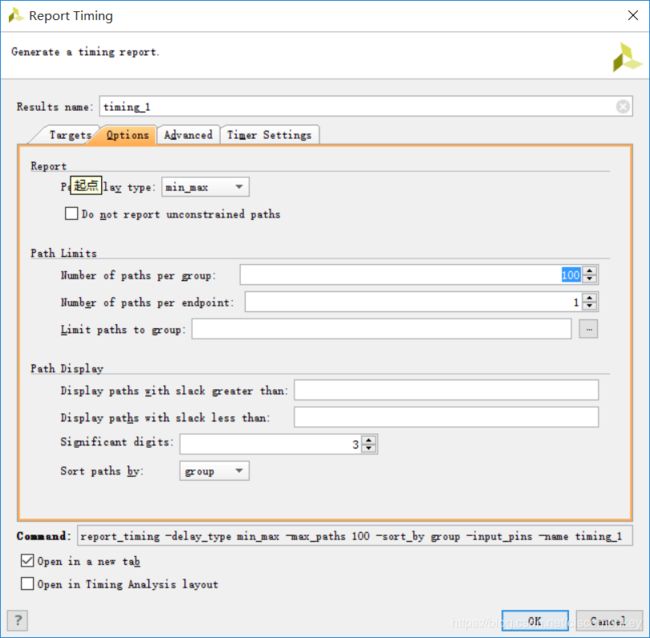

关闭窗口后,然后report timing,报告100条路径

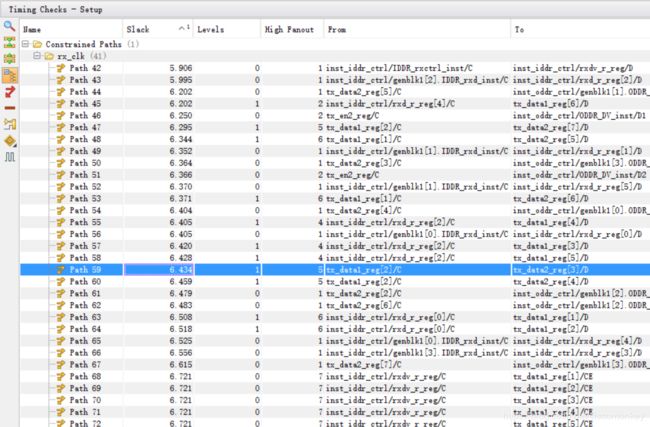

slack代表的余量,level代表该路径是否有组合逻辑,比如if

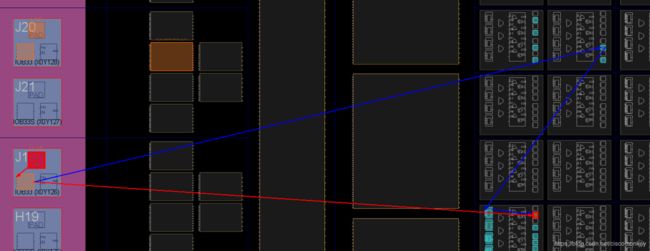

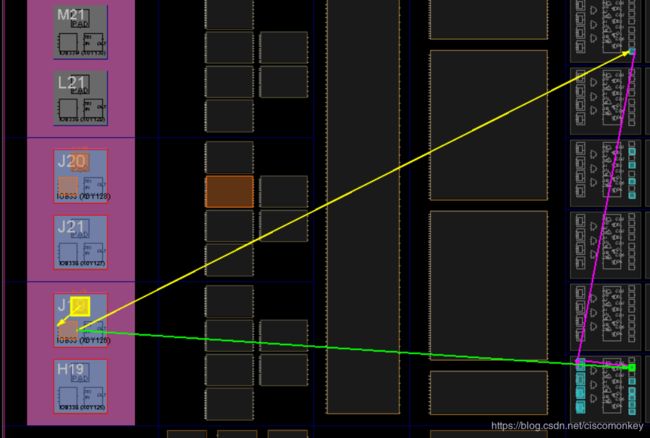

双击某一条路径后,可以对该条路径显示细节,通过点击右键进行highlight标亮后,然后再device中查看,从而可以看到路径

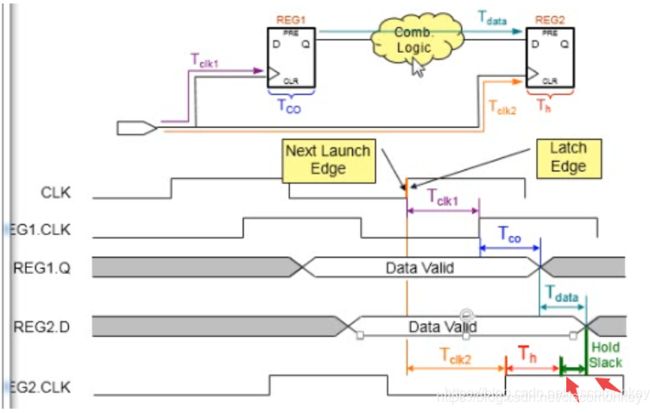

始终要根据此模型

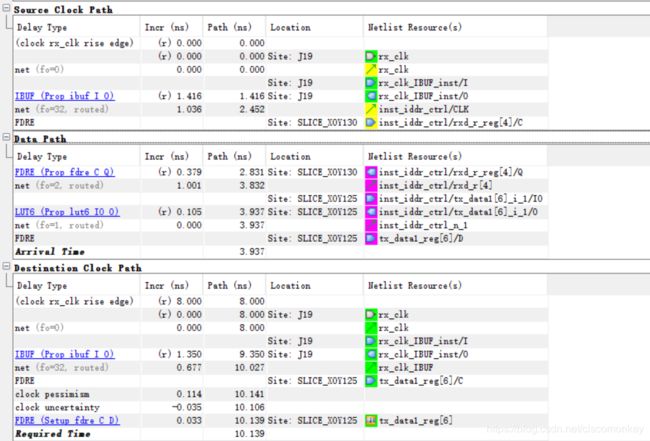

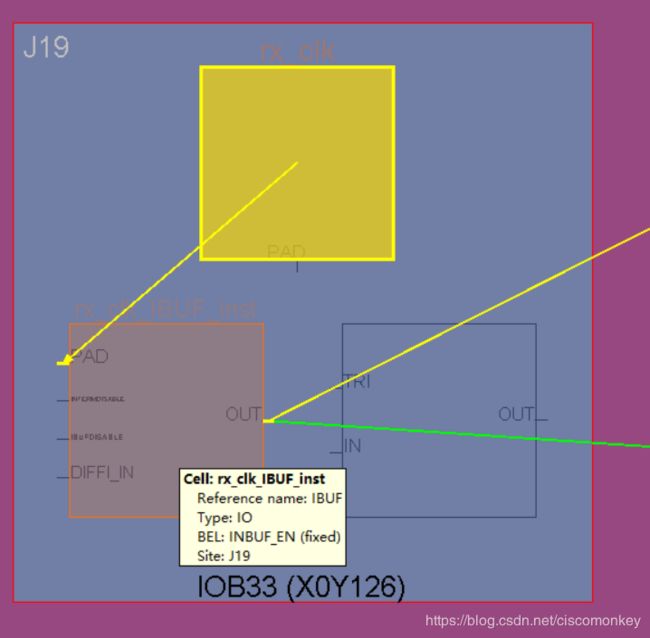

首先通过外部的时钟晶振,时钟通过时钟缓冲器buffer,进行输出,当然一路时钟(黄色)输出给了源寄存器,另一路时钟输出给了目的寄存器。

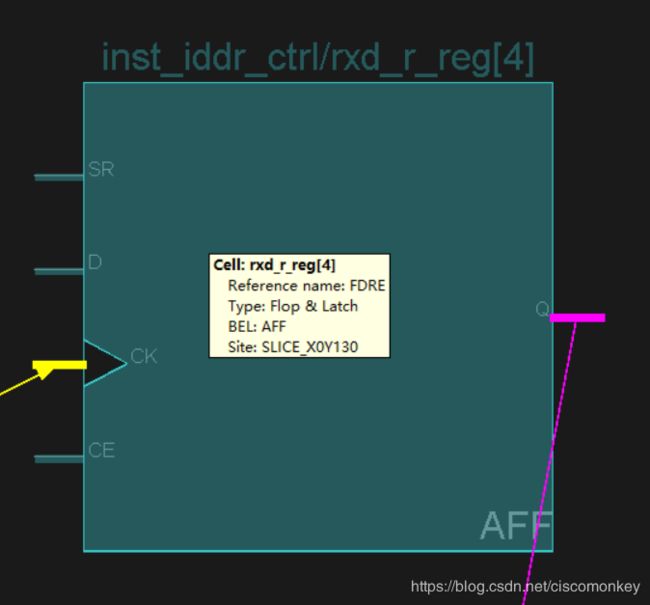

然后看到,第一路时钟给了一个触发器,触发器的类型是FDRE,代表同步复位,复位值为0。

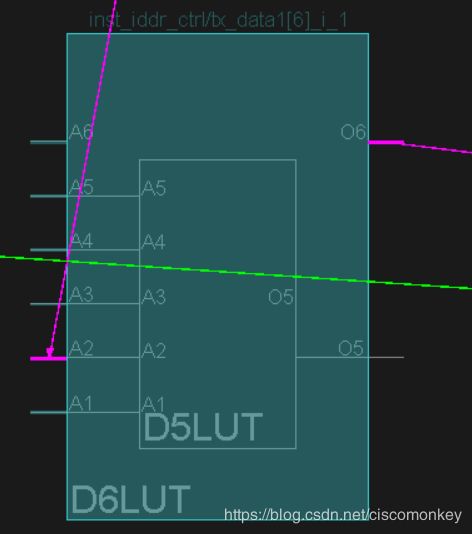

然后数据线经过了一个组合逻辑

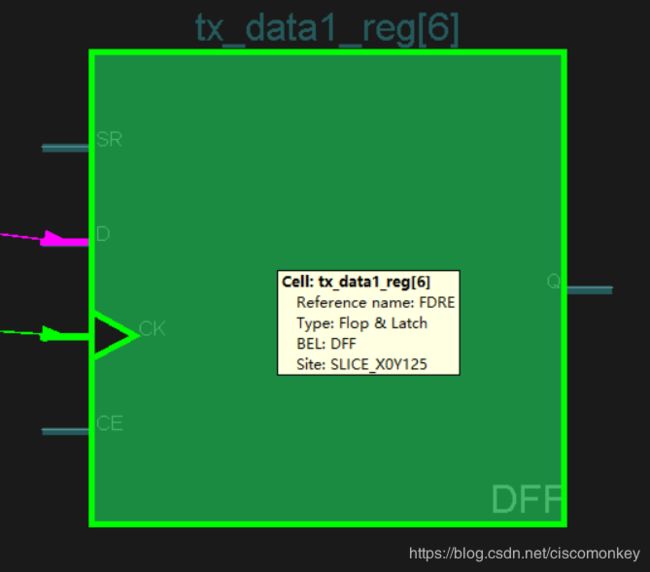

然后数据到达目的寄存器,从而这条路径完全符合我们的经典两级寄存器时序分析模型

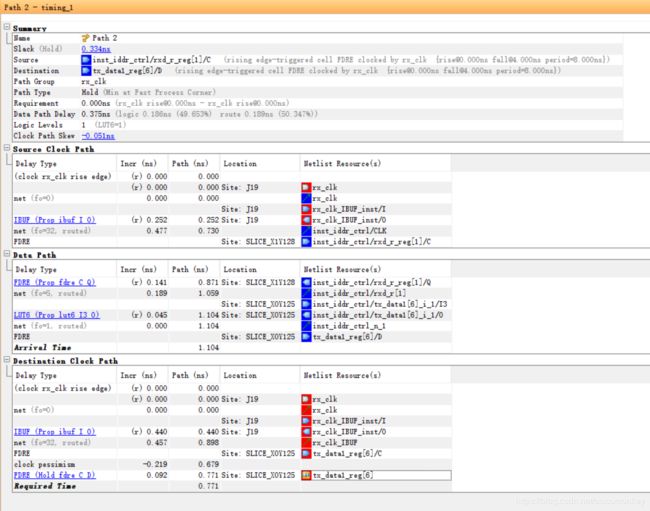

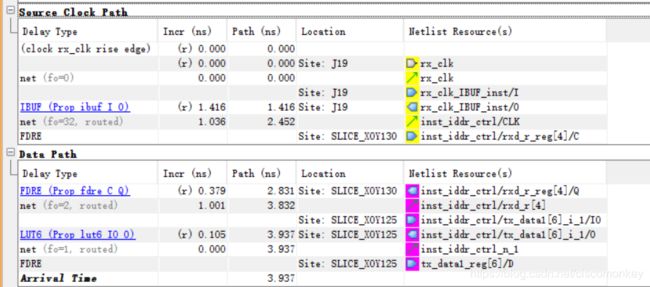

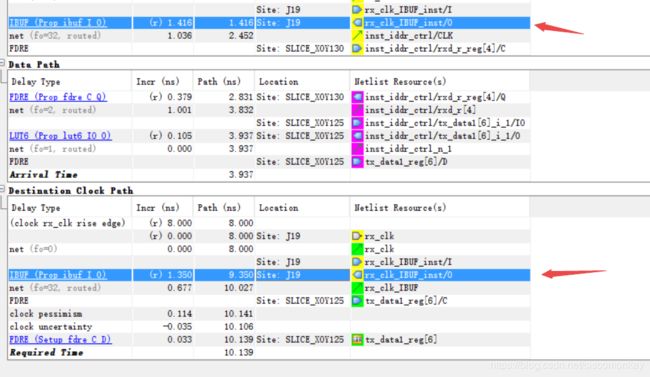

下面来看一下计算的数据

首先是数据到达时间,表里面理出了,经过每一条路径的时间累加,incr代表这条线(器件)增加的时间,path代表总的累加时间,直到计算出累加的时间是3.937.

接着是数据需求时间,在询问后,其实我觉得可这样来理解,真正进入寄存器的采集还需要一定延时,与建立时间之和后,可能为正,也可能为负。

最后用需求时间减去数据到达时间即可。

疑问?

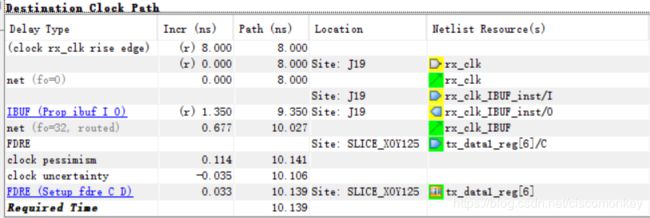

为什么下图经过同样的ibuf,结果会不一样呢?

前面那个相当于TCLK1,后面那个相当于TCLK2

为了以最坏的角度考虑,TCLK1应该取最大值,TCLK2应该取最小值。所以下面的结果不一样,是考虑的最悲观的角度。

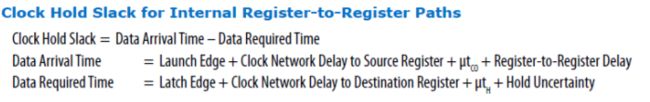

3、保持时间

如下图所示,为了计算hold slack的时间,需要计算两个点

所以hold slack与时钟的快慢(时钟周期)是没有关系的。

所以看出,增加组合逻辑的延时,可以改善hold 的slack