【软件开发底层知识修炼】四 深入浅出处理器之四 结合高速缓存以及TLB与虚拟内存

学习交流加

- 个人qq:

1126137994- 个人微信:

liu1126137994- 学习交流资源分享qq群:

962535112

文章目录

- 0、回顾

- 1、高速缓存(Cache)的引入

- 2、利用TLB加速地址翻译

- 3、Cache与物理内存是如何映射的

- 3.1、直接映射法:

- 3.2、直接映射原理

- 3.3、直接映射法的特点

- 4、总结

上一篇文章学习了(点击链接查看上一篇文章上一篇文章):

-

虚拟内存的概念与交换区的概念

-

MMU的作用

-

虚拟内存机制的意义

- 虚拟内存作为内存管理工具

- 虚拟内存作为内存保护工具

-

页表的概念

-

页命中与缺页

-

程序的局部性在虚拟内存中的作用

-

MMU的地址翻译过程

0、回顾

回顾上一篇文章,这里再补充一下:

- 当页命中时,CPU硬件执行的步骤

注释:VA:虚拟地址 PTEA:页表条目地址 PTE:页表条目 PA物理内存地址

如上图,CPU的执行步骤如下:

- 处理器生成一个虚拟地址,并把它传送给MMU

- MMU生成PTE地址,并从高速缓存/物理内存请求得到它

- 高速缓存/物理内存向MMU返回PTE

- MMU根据得到的PTE索引页表,从而构造物理地址,并把物理地址传送给高速缓存/物理内存

- 高速缓存/物理内存返回请求的数据或者指令给CPU

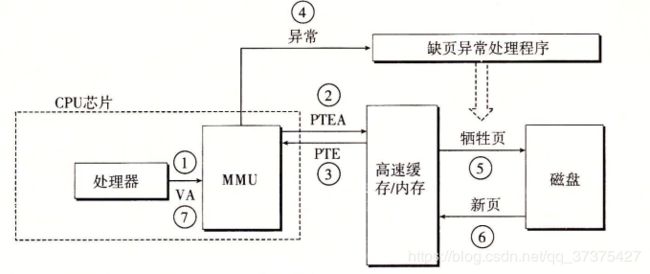

- 当缺页时,CPU的硬件执行过程

注释:VA:虚拟地址 PTEA:页表条目地址 PTE:页表条目

如上图,CPU的执行步骤如下:

- 处理器生成一个虚拟地址,并把它传送给MMU

- MMU生成PTE地址,并从高速缓存/物理内存请求得到它

- 高速缓存/物理内存向MMU返回PTE

- PTE中的有效位是0,所以MMU触发了一次异常,传递CPU中的控制到操作系统内核中的缺页异常处理程序

- 缺页异常处理程序确定出物理内存中的牺牲页,如果这个页面被修改了,就将它换出道磁盘

- 缺页异常处理程序将需要的页面调入到高速缓存/物理内存,并更新内存中的PTE

- 缺页异常处理程序返回到原来的进程,再次执行导致缺页的指令。CPU将引起缺页的地址再次发送给MMU。因为虚拟页面现在缓存在物理内存中了,所以此次就会命中,物理内存就会将所请求的数据或者指令返回给CPU

可以看到,页命中与缺页的前三步,都是一样的。我们还可以总结出一个重要的结论:

页命中完全是由硬件来处理的,而缺页,却是由硬件和操作系统内核共同完成的。

1、高速缓存(Cache)的引入

看看上面分析页命中与缺页的过程中,出现了高速缓存,如果只有物理内存很好理解,现在出现高速缓存是啥意思?

学习过上一篇文章,我们应该可以理解页命中,缺页这些简单的概念以及虚拟地址的寻址过程(如果不明白,建议先学习上一篇文章)。

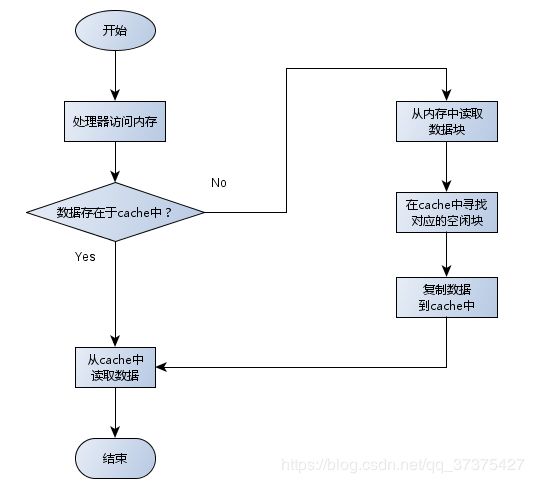

我们知道,CPU寻址时,从内存中获取指令与数据的时间还是相当大的(CPU的速度远远大于内存的速度)。所以高速缓存(Cache)就出现了。

- Cache是一种小容量高速存储器

- Cache的存取速度与CPU的运算速度几乎同量级

- Cache在现代计算机系统中直接内置于处理器芯片中

- 在处理器和内存之间设置cache(精确来讲是将Cache放在MMU与物理内存之间)

- 把内存中被频繁访问的数据和指令复制到cache中

- 页表也在内存中,将被频繁访问的PTE,复制到Cache中

- 大多数情况下,CPU可以直接从cache中取指令与数据

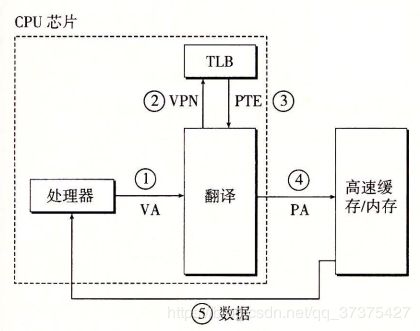

如下图,我们先来看一个高速缓存与虚拟内存结合的例子,看看此时CPU的访问过程:

这个图,其实很好理解!!!当MMU要查询PTEA以及PA时,都先去高速缓存中先查一下,看看有没有,如果高速缓存中有PTEA与PA,直接从高速缓存中获取数相应的PTE与数据。

如果高速缓存中没有相应的PTEA或者PA时,就去物理内存中获取,然后从物理内存中获取之后,将获取到的PTE或者数据再缓存到高速缓存中,然后高速缓存将获取到的数据返回给CPU执行。

注意:因为Cache是放在MMU与物理内存之间的,所以高速缓存无需处理保护问题,因为访问权限的检查是MMU地址翻译过程的一部分。

2、利用TLB加速地址翻译

学到了这里,我们应该很清楚地址翻译的过程了。如果不清楚,就需要看上一篇文章或者深入理解计算机系统第九章。

在地址翻译的过程中,CPU每产生一个虚拟地址(VP),MMU都要去别的地方查询一个PTE。这个别的地方指:高速缓存或者物理内存。

在最坏的情况下(缺页),需要访问两次物理内存。这种开销是极其昂贵的。

在最好的情况下,MMU也需要去高速缓存中获取PTE对应的值。虽然高速缓存已经很快了,但是相对于CPU内部来说,还是有点慢。

那么能不能MMU不去别的地方获取PTE?能不能在MMU内部也搞一个类似于高速缓存的东西,来存储一部分经常被访问的PTE?答案是可以的!!!

在MMU中,有一个小的缓存,称为翻译后备缓冲器(TLB)

如下图示来看看带有TLB的 MMU,且TLB命中时,是如何执行的

- CPU产生一个虚拟地址

- 第二部和第三部是MMU从TLB中取出相应的PTE

- MMU将这个虚拟地址翻译成一个物理地址,并将它发送到高速缓存/物理内存。

- 高速缓存/物理内存将所请求的数据字返回给CPU

我们可以看到,TLB是虚拟寻址的缓存。

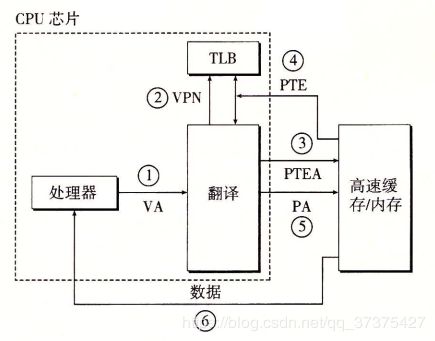

下面再来看看TLB不命中时,是如何执行的

当TLB不命中时,关键点在于,MMU必须从L1高速缓存中获取到相应的PTE,新取出的PTE再放到TLB中,此时可能会覆盖一个已经存在的条目。那么当TLB中有了相应的PTE,MMU再去TLB中查找…

3、Cache与物理内存是如何映射的

这里我们只学习一下直接映射法:

3.1、直接映射法:

-

将cache和物理内存分成固定大小的块(如512byte/块)

-

物理内存中的每一块在cache中都有固定的映射位置

-

对应的映射公式为:

- Pos(cache) = 内存块号 % cache总块数

注意:任意一个物理内存块都可以映射到唯一固定的cache块(物理内存不同的块,可以映射到同一个cache块)。

3.2、直接映射原理

比如我们想要访问某一个物理地址,我们如何知道这个地址是否在cache中?或者如何知道它在cache中的位置?

首先,现在只有一个物理地址,需要根据这个物理地址进行判断。

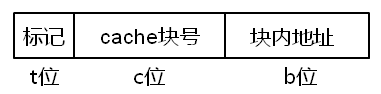

看下面,对物理地址有一个划分:

以上的物理地址分为3部分,都是什么意思呢?

我们利用以下规则来判断;

-

根据物理地址的中间的c位,找到cache中对应的块

-

比较物理地址的高t位,让它与cache中的flag比较,看是否相同

- 如果相同:说明数据在高速缓存中有缓存,那么此时根据物理内存的b位找到cache对应的块中的偏移

- 如果不同:说明数据在缓存中没有缓存,此时就将物理内存中对应的数据复制到cache中

3.3、直接映射法的特点

我们已经知道,直接映射法,很有可能不同的物理内存块映射到相同的cache块。所以直接映射法这样会导致缓存失效。但是直接映射法过程简单,所需耗时短!!

4、总结

本篇文章学会了以下内容;

- 高速缓存的作用

- TLB的作用

- 物理内存与cache之间的映射原理

本文章参考狄泰软件学院相关课程与深入理解计算机系统第九章内容

想学习的可以加狄泰软件学院群,

群聊号码:199546072

本人积累了无数的技术电子书籍与各类技术的视频教程,可以加好友共同探讨学习交流。

学习探讨加个人:

qq:1126137994

微信:liu1126137994