学习笔记--Verilog HDL高级数字设计--第六章组合逻辑与时序逻辑的综合

组合逻辑与时序逻辑的综合

综合引擎能够自动完成一组布尔函数的最简化,并将结果映射成能满足设计目标的硬件实现。(转换,优化,映射)

本章将介绍如何编写易于综合的Verilog模型

综合工具完成的工作:

(1)检测并消除冗余项

(2)查找组合反馈环路

(3)利用无关紧要条件

(4)检测出未使用状态

(5)查找并消除等价状态

(6)进行状态分配

(7)在满足物理工艺的面积和/速度限制下,综合出最优多级逻辑实现。(该步既包括了最优化技术,又有工艺映射内容)

综合简介

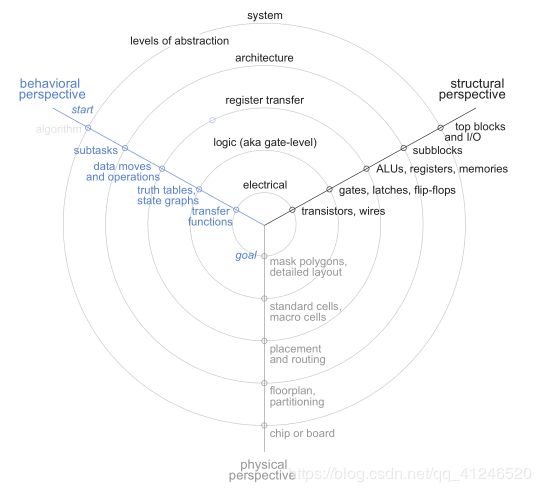

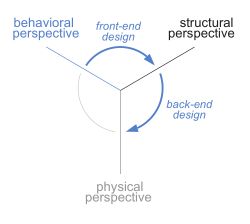

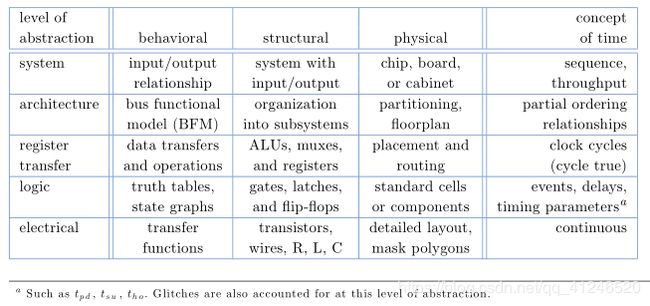

Y形图

三个轴代表看数字电路的三种角度。

同心圆代表不同的抽象程度。

行为描述角度:我们只关心电路和系统的功能,不关心它的具体实现。换句话说,设计被看作是一个black-box,通过产生一些输出符号来响应一些输入符号来处理信息。最重要的是过去输出和当前输入的依赖性,但是输入、输出数据和一些时钟信号之间的时序关系也很重要。

结构描述角度:用组成电路的构件以及它们之间的连接方式(connectivity)作为研究电子电路的结构化方法。行为描述与结构描述之间存在一对多的关系。结构方案通常在电路复杂性、性能、能源效率以及其他实用性方面有所不同。

物理描述角度:我们关心各种硬件组组件和线如何安排在可用的空间中。

不同的抽象层次:

可以看出system和architecture抽象层次无时钟概念。

BFM

以下内容摘抄自我老师的微博:

http://blog.sina.com.cn/s/blog_5e9b181a0100y6lt.html

以做一个MAC的core为例(背板是PCI总线),那么我们需要一个MAC_BFM和PCI_BFM及PCI_BM(PCI behavior. model)。MAC_BFM的主要功能是产生以太网帧(激励源),随机的长度和帧头,内容也是随机的,在发送的同时也将其复制一份到PCI_BM中;PCI_BFM的功能则是仿PCI总线的行为,比如被测收到了一个正确帧后会向PCI总线发送一个请求,PCI_BFM则会去响应它,并将数据收进来;PCI_BM的主要功能是将MAC_BFM发送出来的东西与PCI_BFM接收到的东西做比较,由于它具有了MAC_BFM的发送信息和PCI_BFM的接收信息,只要设计合理,它总是可以自动地、完全地去测试被测是否工作正常,从而实现自动检测。

因此,BFM可以看作是总线接口的行为级模型,他用来测试接在总线上的module。因此,这个测试平台就是BFM。VMM测试模型和VCM模型也许里面就是这样的测试平台的功能集合还有对一些测试激励产生的模型

逻辑综合

综合过程中的转换一定要保证综合前后电路输入-输出的等效性,以及生成电路的可测性。

综合过程中的优化是基于迭代搜索的,先逻辑优化再性能优化。

关键算法:分解(decomposition)、因式分解(factoring)、替代(substitution)和消去(elimination)。

分解

分解操作依据新节点来表示一个单一的布尔函数。这些节点对应多个布尔函数的公共因子,可以用来消除重复逻辑。

设 F = abc + abd + a’c’d’ + b’c’d’

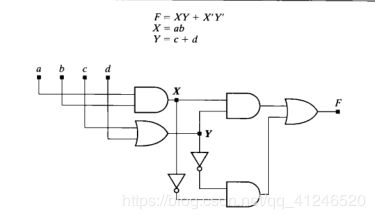

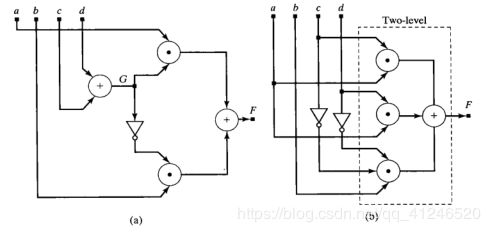

分解操作可以用两个附加内部节点——X = ab,Y = c + d——通过复用形成函数,从而减小硬件电路面积。 分解后电路

分解后电路

因式分解

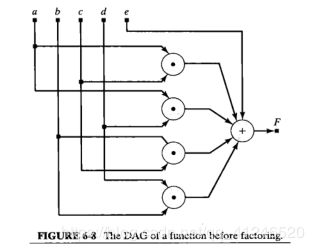

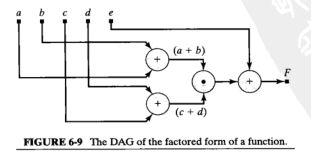

在一组函数中寻找公共因子的过程叫因式分解。通过因式分解可产生一组和之积形式的函数,可以利用它将两级实现的电路转换为等效的多级实现。(使面积减小,但可能性能也变差)

假设F = ac + ad + bc + bd +e可因式分解为F = (a + b)(c + d) + e

符号少逻辑单元便少

符号少逻辑单元便少

替代

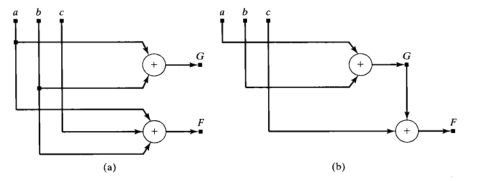

替代操作就是用原有的输入和其他函数表示布尔方程的过程。(减少重复逻辑)

假设*G = a + b, F = a + b + c *

替换之后:F = G + c

a图需要三个加法器,b图需要两个。

消去

消去过程可去除函数中的某个节点并简化电路结构,这一步也称为电路展平。(创建一个更快速的两级结构)

假设F = Ga + G’b, G = c + d

消去之后:F = ac + ad + bc’d’

高级综合

又称为“行为综合”和“结构综合”。高级综合是从一个不包含具体实现细节的输入-输出算法开始的。

执行的两个主要步骤:资源分配和资源调度,以产生一个包含数据通路单元、控制通路单元和存储器的电路结构。

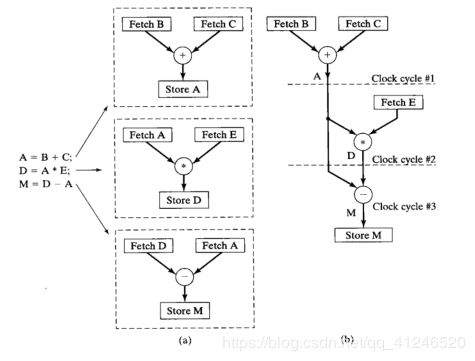

一个假象算法如图:

数据流图(b)显示了数据之间的依赖关系。

资源分配标识出算法中所用的运算符(逻辑单元),并且推断出用于保存算法顺序执行过程中产生的数据所需的存储资源,还将操作符(运算资源)以及存储资源绑定到数据通路资源中。

资源调度将行为描述中的操作分配到特定的时钟周期(隐含状态),以实现算法设定的操作顺序。

这将最终确定在一个给定时钟周期中将要使用的,以及不同时钟周期之间共享的计算单元(操作符)数量。

组合逻辑的综合

利用无关紧要项

在综合时case或if语句中使用x的赋值将被处理成无关紧要项。即在此输入下,不关心case中的赋值情况,以减少实现电路所需的逻辑。

带锁存器的时序逻辑综合

综合要点:

(1)含反馈的组合原语网表和一组连续赋值语句描述可能会被标为一个错误条件,且不可综合。但连续复制语句中使用带反馈的条件操作符时,综合工具会判定这是一种有意生成锁存器的方法(这种情况会用组合逻辑实现,不会在单元库中寻找单元去实现)。

(2)在电平敏感周期性行为中,如果if和case语句只是条件不完整则综合出锁存器;如果条件完备,但出现变量将其指显示地赋给它自身的情况,则综合出带反馈的多路复用器(类似带反馈的使用条件操作符的assign)。

带有触发器的时序逻辑综合

触发器仅有边沿敏感的行为综合而来,但并不是在边沿敏感的行为中赋值的每一个寄存器变量都会综合成触发器。那么就需要考虑一下几个问题。

(1)综合工具如何推导出对触发器的需求的?

(2)边沿敏感行为中被赋值的寄存器变量,什么时候会自动综合成一个触发器?

(3)触发器是由一个时钟信号进行同步的——综合工具如何从其他信号中区分出同步信号来?或者它必须要用特定的标识符来识别么(如clock)?

(4)如果一个设计中包含多级触发器,那么应该怎样描述模型才能确保它们能够并行工作?

综合工具如何推导出对触发器的需求的? && 边沿敏感行为中被赋值的寄存器变量,什么时候会自动综合成一个触发器?

在边沿敏感行为中:

(1)如果该寄存器变量在进行行为描述的范围外被使用。

(2)如果该寄存器变量在未被赋值前就已在行为描述中被用到。(反馈)

(3)如果该寄存器变量仅在行为描述动作的某些分支上被赋值。

综合要点:

当一个变量在被内部行为(而不是外部行为)引用前就被周期性行为赋值,综合过程将消除这个变量。

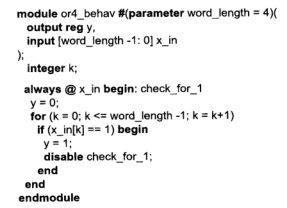

例:

寄存器变量k仅在内部使用(对应第一条)

它被赋值前未被引用(对应第二条),所以变量k仅仅用来支持算法,并不需要实际的硬件存储器,因此它将在综合时被消除。

综合要点:

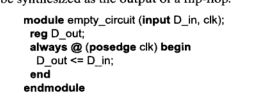

由边沿敏感行为赋值并在该行为之外会用到的变量会被综合为一个触发器输出。

例:

D_out会被消除,但如果将D_out定义为输出端口,则它将被综合为一个触发器输出。

触发器是由一个时钟信号进行同步的——综合工具如何从其他信号中区分出同步信号来?或者它必须要用特定的标识符来识别么(如clock)?

在一个边沿敏感周期性行为的事件控制表达式中,边沿敏感信号由译码的顺序决定哪些是控制信号,哪一个是时钟信号(同步信号)。

如果事件控制表达式对多个信号都是边沿敏感的,那么在该行为描述中必须首先声明if条件语句。

该事件控制表达式的控制信号必须在if条件分支中优先进行译码(例如。首先对复位信号进行译码)。

同步信号不会在if语句条件中被明确地写出,但默认情况下,if语句中最后一个分支的动作必须进行同步操作。

显示状态级的综合

在介绍该内容之前,先来学习一下人工设计状态级的方法,这对后续内容的理解会有帮助。

人工方法设计

设计步骤:

(1)构建状态机的STG

(2)消去等价状态

(3)选取状态码(如二进制码)

(4)对状态编码

(5)求解描述D触发器输入的布尔方程

(6)利用卡诺图化简布尔方程

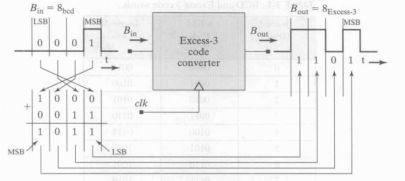

假设要设计一个将串行发送的BCD码Bin转换为一个余3码的串行比特流Bout的转换器。且Bin和Bout都是先从LSB发送。

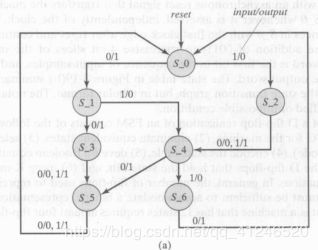

(1)构建状态机的STG

假设Bin[0]为LSB,如果Bin[0]做完加法运算有进位则跳转到S_2,否则跳转到S_1;若Bin[1]有进位则跳转到S_4……

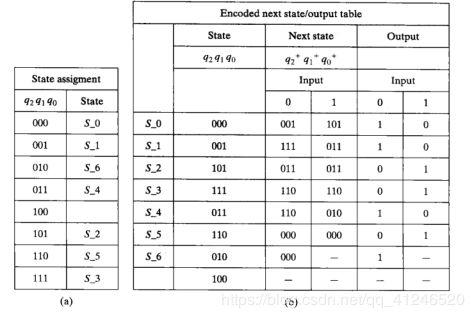

(2)分配码字

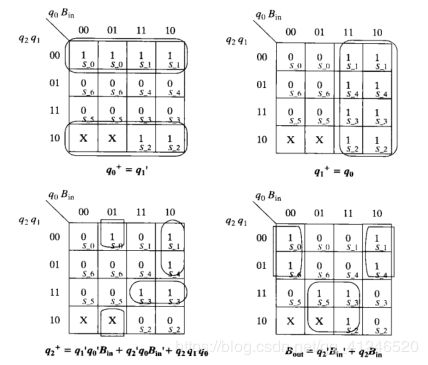

(3)求解并化简布尔方程

将q2+和Bout转换为与非门结构得

![]()

![]()

可以得到原理图为:

状态编码

状态编码决定了保存状态所需要的触发器数量,它会影响状态机的下一状态和输出逻辑复杂度。综合工具内嵌了各种算法以寻找优化的状态分配方案,设计者也可以采取手动方式进行状态编码的分配。

手动分配原则:

(1)如果对于某个给定输入,两个状态会跳转到相同的下一状态,则给它们分配相邻的码字。

(2)对相邻的状态分配相邻的码字。

(3)对于某个给定的输入具有相同的输出的状态,分配相邻的码字。

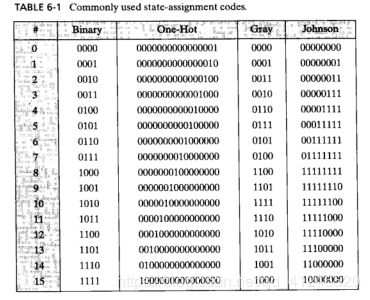

常见的状态分配编码

Gray码和Johson码特点是相邻编码仅有一个位不同,可以减少相邻物理信号线信号同时变化的情况,从而减少串扰的可能。而且在实际硬件操作中发生状态变化时,该类编码可减少通过中间状态的过度时间。

One-Hot编码使用的触发器数目相对较多,但其状态级中只需要对寄存器中的个位进行译码,所以它的译码逻辑比较简单。因此One-Hot编码速度更快,且额外的触发器面积可被译码电路节省的面积抵消。而且使用case语句来描述的One-Hot编码可能与if语句描述产生不同的结果(case是对所有bit进行判断,if可检测单一bit)。

注意,如果一个状态编码没有覆盖所有码值,那么需要附加的逻辑来检查无效状态,并从无效状态中恢复(不会跳转进入无效状态,而可能由噪声将状态级带入无效状态)。这种附加逻辑会影响实现设计所需的面积。

综合要点

一般来说,应避免输入的变化与状态的变化同步进行,除非输入对于跳变沿来说是无关紧要状态。

寄存器逻辑

利用时钟进行同步赋值的变量称为寄存器类型变量。Moore状态机的输出不是寄存器类型变量,但当输入端变化时它不会产生毛刺。

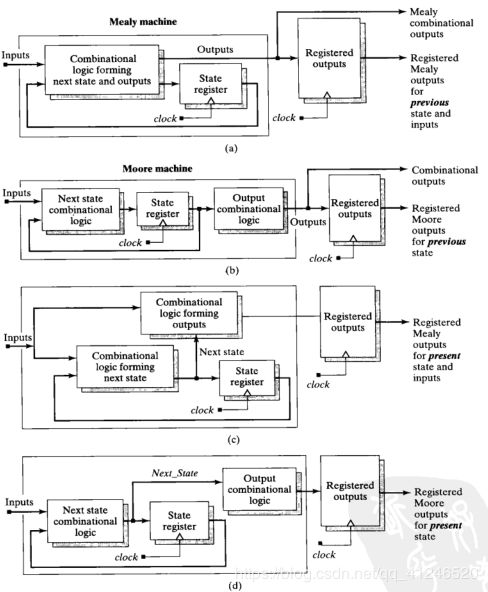

寄存输出的状态机

其中c和d的结构满足寄存器的输出与状态级当前时钟周期的状态相对应。

但是我认为Mealy型状态级的状态转移和输入是相同沿同步时,即使使用c的结构也还是会延迟一个周期输出,因为Mealy输出与当前输入有关,即使能预测下一周期状态也无法预测下一周期的输入信号。

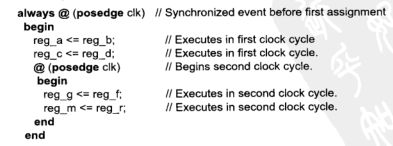

隐式状态机综合

隐式状态机在一个行为中具有一个或多个时钟同步的(边沿敏感的)时间控制表达式。显式状态机的同步行为只能有一个这样的事件控制表达式。隐式状态机中的多个事件表达式将行为动作分配到状态机的不同时钟周期。

隐式状态机不使用明确的reg来表示状态值,而是由周期性 行为中的动作变化来隐性地定义状态。

隐式状态机的限制:每一状态只能由其他一种状态进入,因为状态是由一个时钟周期进入下一时钟周期时行为的进展情况决定的,而一个时钟周期只能从他紧邻的前一个时钟周期进入。

预测综合结果

运算符的综合:①通过综合工具中的专用映射器以某种特殊的方式来处理;②综合工具将会把这些运算符转换成等效的布尔方程组并进行优化。

综合结果的结构将会反映出编译器的语法分析过程(从左到右)和运算符的优先级,设计者可以是用括号来形成子表达式,以影响综合结果。

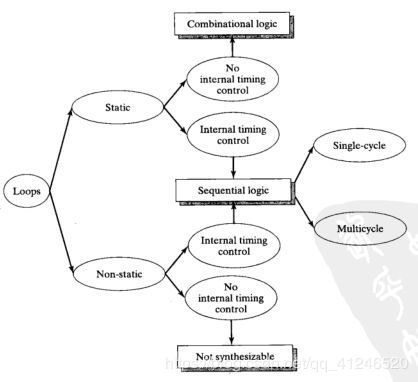

循环的综合

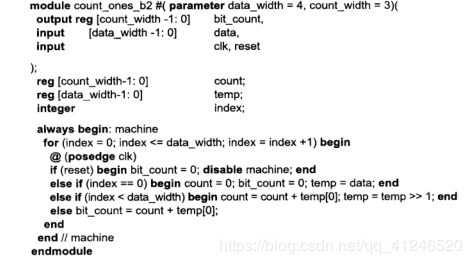

带内嵌定时控制的静态循环

如果一个静态循环包含内嵌的边沿敏感事件控制表达式,该循环的计算行为会被同步,且会分布到一个或多个时钟周期上执行。因此该行为就是循环的每次迭代都在时钟沿之后进行的隐式状态机。

带内嵌定时控制的非静态循环

非静态循环可以实现多周期操作。因为可以将循环的动作分配到多个时钟周期去执行。为了综合,非静态循环的迭代操作必须通过一个同步的边沿敏感的事件控制表达式来分割。

不带内嵌定时控制的非静态循环

我认为语义就是一个带反馈的组合逻辑,能够仿真但不能综合。

状态机替代不可综合循环

循环结构可由等效的可综合时序行为来代替。替代的关键是用显示有限状态机来描述这种行为。