(4)tiny4412移植uboot_2018_07

开发板:tiny4412(1611)

编译器: arm-tiny4412-linux-gnueabi-gcc (gcc version 6.1)

说明:本次移植希望在新版uboot支持sd卡启动方式

文章目录

- 移植中debug方式

- uboot中差异点

- 第一步.修改text地址,增加烧写脚本

- 第二步.修改时钟

- 第三步.支持DRAM

- 第四步.修改trusted zone权限

- 试验

移植中debug方式

1.增加led点灯代码

2.在确定系统时钟初始化完成后,可以使用串口进行调试

(原厂会使用ds-5连接jtag进行单步调试,比较便捷)

uboot中差异点

需要把新版uboot跑起来,其实uboot的差异点也就是板级差异.物料的不同,如DDR的不同之类,当然由这些硬件的差异还可能有一些软件上寄存器配置的差异.

第一步.修改text地址,增加烧写脚本

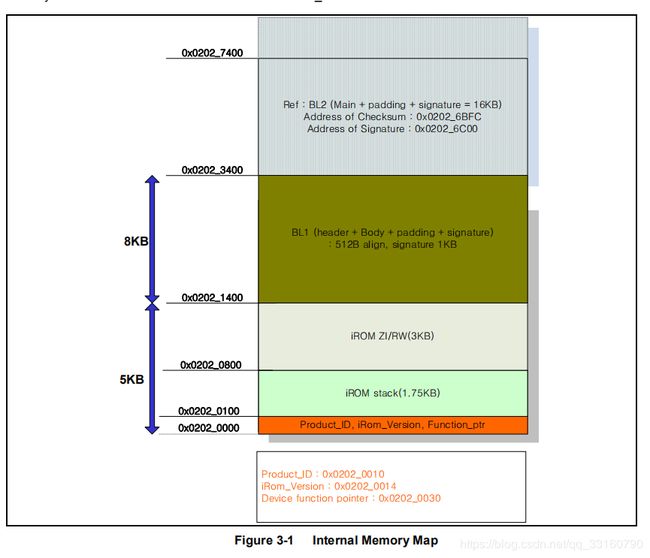

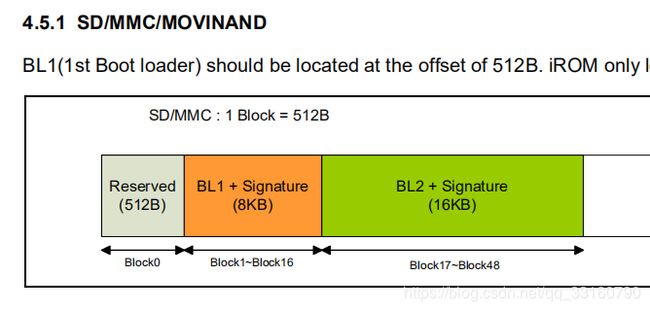

根据三星官方手册可得知,官方默认BL1代码会将BL2(uboot的spl部分)加载到0x02023400地址执行.另外使用sd卡作为介质时,手册给出了BL1、BL2大小和位置。

diff --git a/include/configs/origen.h b/include/configs/origen.h

index 65e1c7c..f964456 100644

--- a/include/configs/origen.h

+++ b/include/configs/origen.h

@@ -46,7 +46,7 @@

/* MMC SPL */

#define COPY_BL2_FNPTR_ADDR 0x02020030

-#define CONFIG_SPL_TEXT_BASE 0x02021410

+#define CONFIG_SPL_TEXT_BASE 0x02023400

#define CONFIG_EXTRA_ENV_SETTINGS \

"loadaddr=0x40007000\0" \

@@ -87,8 +76,9 @@

#define CONFIG_SYS_MMC_ENV_DEV 0

#define CONFIG_ENV_SIZE (16 << 10) /* 16 KB */

#define RESERVE_BLOCK_SIZE (512)

-#define BL1_SIZE (16 << 10) /*16 K reserved for BL1*/

-#define CONFIG_ENV_OFFSET (RESERVE_BLOCK_SIZE + BL1_SIZE)

+#define BL1_SIZE (8 << 10) /*8 K reserved for BL1*/

+#define BL2_SIZE (16 << 10) /*16 K reserved for BL2*/

+#define CONFIG_ENV_OFFSET (RESERVE_BLOCK_SIZE + BL1_SIZE + BL2_SIZE)

#define CONFIG_SPL_MAX_FOOTPRINT (14 * 1024)

第二步.修改时钟

修改完时钟后,就可以使用串口进行debug。我们将APLL改为1400MHZ,MPLL改为800MHZ。串口、SD卡 、MMC卡这些都是使用MPLL作为时钟源。

diff --git a/include/configs/origen.h b/include/configs/origen.h

index 65e1c7c..f964456 100644

--- a/include/configs/origen.h

+++ b/include/configs/origen.h

@@ -99,4 +89,12 @@

#define BL2_START_OFFSET ((CONFIG_ENV_OFFSET + CONFIG_ENV_SIZE)/512)

#define BL2_SIZE_BLOC_COUNT (COPY_BL2_SIZE/512)

+/* uart0 debug for spl */

+#define CONFIG_SPL_SERIAL_SUPPORT

+#define CONFIG_SPL_GPIO_SUPPORT

+#define CONFIG_DEBUG_UART

+#define CONFIG_DEBUG_UART_S5P

+#define CONFIG_DEBUG_UART_BASE 0x13800000 /* UART0 base address */

+#define CONFIG_DEBUG_UART_CLOCK (100000000) /* SCLK_UART0 is 100MHz */

+

#endif /* __CONFIG_H */

diff --git a/arch/arm/mach-exynos/clock_init_exynos4.c b/arch/arm/mach-exynos/clock_init_exynos4.c

index 584e4ba..fda1837 100644

--- a/arch/arm/mach-exynos/clock_init_exynos4.c

+++ b/arch/arm/mach-exynos/clock_init_exynos4.c

@@ -38,42 +38,39 @@

*/

void system_clock_init(void)

{

- struct exynos4_clock *clk =

- (struct exynos4_clock *)samsung_get_base_clock();

+ struct exynos4x12_clock *clk =

+ (struct exynos4x12_clock *)samsung_get_base_clock();

- writel(CLK_SRC_CPU_VAL, &clk->src_cpu);

+ /* APLL= 1400 MHz MPLL=800 MHz */

+

+ writel(0x01000001, &clk->src_cpu);

sdelay(0x10000);

- writel(CLK_SRC_TOP0_VAL, &clk->src_top0);

- writel(CLK_SRC_TOP1_VAL, &clk->src_top1);

- writel(CLK_SRC_DMC_VAL, &clk->src_dmc);

- writel(CLK_SRC_LEFTBUS_VAL, &clk->src_leftbus);

- writel(CLK_SRC_RIGHTBUS_VAL, &clk->src_rightbus);

+ writel(0x10, &clk->src_leftbus);

+ writel(0x10, &clk->src_rightbus);

+ writel(0x110, &clk->src_top0);

+ writel(0x1111000, &clk->src_top1);

+ writel(0x00011000, &clk->src_dmc);

writel(CLK_SRC_FSYS_VAL, &clk->src_fsys);

writel(CLK_SRC_PERIL0_VAL, &clk->src_peril0);

writel(CLK_SRC_CAM_VAL, &clk->src_cam);

writel(CLK_SRC_MFC_VAL, &clk->src_mfc);

writel(CLK_SRC_G3D_VAL, &clk->src_g3d);

- writel(CLK_SRC_LCD0_VAL, &clk->src_lcd0);

sdelay(0x10000);

- writel(CLK_DIV_CPU0_VAL, &clk->div_cpu0);

- writel(CLK_DIV_CPU1_VAL, &clk->div_cpu1);

- writel(CLK_DIV_DMC0_VAL, &clk->div_dmc0);

- writel(CLK_DIV_DMC1_VAL, &clk->div_dmc1);

- writel(CLK_DIV_LEFTBUS_VAL, &clk->div_leftbus);

- writel(CLK_DIV_RIGHTBUS_VAL, &clk->div_rightbus);

- writel(CLK_DIV_TOP_VAL, &clk->div_top);

+ writel(0x1160730, &clk->div_cpu0);

+ writel(0x506, &clk->div_cpu1);

+ writel(0x111113, &clk->div_dmc0);

+ writel(0x1011713, &clk->div_dmc1);

writel(CLK_DIV_FSYS1_VAL, &clk->div_fsys1);

- writel(CLK_DIV_FSYS2_VAL, &clk->div_fsys2);

+ writel(0x4070047, &clk->div_fsys2);

writel(CLK_DIV_FSYS3_VAL, &clk->div_fsys3);

writel(CLK_DIV_PERIL0_VAL, &clk->div_peril0);

writel(CLK_DIV_CAM_VAL, &clk->div_cam);

writel(CLK_DIV_MFC_VAL, &clk->div_mfc);

writel(CLK_DIV_G3D_VAL, &clk->div_g3d);

- writel(CLK_DIV_LCD0_VAL, &clk->div_lcd0);

/* Set PLL locktime */

writel(PLL_LOCKTIME, &clk->apll_lock);

@@ -81,10 +78,10 @@ void system_clock_init(void)

writel(PLL_LOCKTIME, &clk->epll_lock);

writel(PLL_LOCKTIME, &clk->vpll_lock);

- writel(APLL_CON1_VAL, &clk->apll_con1);

- writel(APLL_CON0_VAL, &clk->apll_con0);

- writel(MPLL_CON1_VAL, &clk->mpll_con1);

- writel(MPLL_CON0_VAL, &clk->mpll_con0);

+ writel(0x803800, &clk->apll_con1);

+ writel(0x80af0300, &clk->apll_con0);

+ writel(0x803800, &clk->mpll_con1);

+ writel(0x80640300, &clk->mpll_con0);

writel(EPLL_CON1_VAL, &clk->epll_con1);

writel(EPLL_CON0_VAL, &clk->epll_con0);

writel(VPLL_CON1_VAL, &clk->vpll_con1);

第三步.支持DRAM

这里的寄存器配置不是很清楚的话,可以拿板子自带的uboot。启动后通过md命令查看DMC寄存器的配置。

diff --git a/arch/arm/mach-exynos/dmc_init_exynos4.c b/arch/arm/mach-exynos/dmc_init_exynos4.c

index ecddc72..69e9fd6 100644

--- a/arch/arm/mach-exynos/dmc_init_exynos4.c

+++ b/arch/arm/mach-exynos/dmc_init_exynos4.c

@@ -32,19 +32,19 @@ struct mem_timings mem = {

.direct_cmd_msr = {

DIRECT_CMD1, DIRECT_CMD2, DIRECT_CMD3, DIRECT_CMD4

},

- .timingref = TIMINGREF_VAL,

- .timingrow = TIMINGROW_VAL,

- .timingdata = TIMINGDATA_VAL,

- .timingpower = TIMINGPOWER_VAL,

- .zqcontrol = ZQ_CONTROL_VAL,

- .control0 = CONTROL0_VAL,

- .control1 = CONTROL1_VAL,

- .control2 = CONTROL2_VAL,

- .concontrol = CONCONTROL_VAL,

- .prechconfig = PRECHCONFIG,

- .memcontrol = MEMCONTROL_VAL,

- .memconfig0 = MEMCONFIG0_VAL,

- .memconfig1 = MEMCONFIG1_VAL,

+ .timingref = 0x000000bb,//TIMINGREF_VAL,

+ .timingrow = 0x7a46654f,//TIMINGROW_VAL,

+ .timingdata = 0x46400506,//TIMINGDATA_VAL,

+ .timingpower = 0x52000a3c,//TIMINGPOWER_VAL,

+ .zqcontrol = 0xe3854c03,//ZQ_CONTROL_VAL,

+ .control0 = 0x7110100b,//CONTROL0_VAL,

+ .control1 = 0xe0000086,//CONTROL1_VAL,

+ .control2 = 0x00000000,//CONTROL2_VAL,

+ .concontrol = 0x0fff333a,//CONCONTROL_VAL,

+ .prechconfig = 0xff000000,//PRECHCONFIG,

+ .memcontrol = 0x00302640,//MEMCONTROL_VAL,

+ .memconfig0 = 0x40c01333,//MEMCONFIG0_VAL,

+ .memconfig1 = 0x80e01323,//MEMCONFIG1_VAL,

.dll_resync = FORCE_DLL_RESYNC,

.dll_on = DLL_CONTROL_ON,

};

@@ -124,6 +124,8 @@ static void dmc_init(struct exynos4_dmc *dmc)

writel(mem.memconfig0, &dmc->memconfig0);

writel(mem.memconfig1, &dmc->memconfig1);

+ writel(0x8000001F, &dmc->ivcontrol);

+

/* Config Precharge Policy */

writel(mem.prechconfig, &dmc->prechconfig);

/*

diff --git a/arch/arm/mach-exynos/exynos4_setup.h b/arch/arm/mach-exynos/exynos4_setup.h

index 38735f0..37ce464 100644

--- a/arch/arm/mach-exynos/exynos4_setup.h

+++ b/arch/arm/mach-exynos/exynos4_setup.h

@@ -505,7 +505,7 @@ struct mem_timings {

#define ADD_LAT_PALL (1 << 6)

#define MEM_TYPE_DDR3 (0x6 << 8)

#define MEM_WIDTH_32 (0x2 << 12)

-#define NUM_CHIP_2 (1 << 16)

+#define NUM_CHIP_2 (0 << 16)

#define BL_8 (0x3 << 20)

#define MEMCONTROL_VAL (CLK_STOP_DISABLE | DPWRDN_DISABLE\

| DPWRDN_TYPE | TP_DISABLE | DSREF_DIABLE\

@@ -514,16 +514,16 @@ struct mem_timings {

#define CHIP_BANK_8 (0x3 << 0)

-#define CHIP_ROW_14 (0x2 << 4)

+#define CHIP_ROW_14 (0x3 << 4)

#define CHIP_COL_10 (0x3 << 8)

#define CHIP_MAP_INTERLEAVED (1 << 12)

-#define CHIP_MASK (0xe0 << 16)

+#define CHIP_MASK (0xC0 << 16)

#ifdef CONFIG_MIU_LINEAR

#define CHIP0_BASE (0x40 << 24)

#define CHIP1_BASE (0x60 << 24)

#else

-#define CHIP0_BASE (0x20 << 24)

-#define CHIP1_BASE (0x40 << 24)

+#define CHIP0_BASE (0x40 << 24)

+#define CHIP1_BASE (0x80 << 24)

#endif

#define MEMCONFIG0_VAL (CHIP_BANK_8 | CHIP_ROW_14 | CHIP_COL_10\

| CHIP_MAP_INTERLEAVED | CHIP_MASK | CHIP0_BASE)

第四步.修改trusted zone权限

这里如果不修改的话,会导致部分总线的访问出现问题。

diff --git a/arch/arm/mach-exynos/tzpc.c b/arch/arm/mach-exynos/tzpc.c

index abe8e7f..63605d5 100644

--- a/arch/arm/mach-exynos/tzpc.c

+++ b/arch/arm/mach-exynos/tzpc.c

@@ -17,10 +17,7 @@ void tzpc_init(void)

start = samsung_get_base_tzpc();

- if (cpu_is_exynos5())

- end = start + ((EXYNOS5_NR_TZPC_BANKS - 1) * TZPC_BASE_OFFSET);

- else if (cpu_is_exynos4())

- end = start + ((EXYNOS4_NR_TZPC_BANKS - 1) * TZPC_BASE_OFFSET);

+ end = start + ((EXYNOS4_NR_TZPC_BANKS - 1) * TZPC_BASE_OFFSET);

for (addr = start; addr <= end; addr += TZPC_BASE_OFFSET) {

tzpc = (struct exynos_tzpc *)addr;

@@ -30,11 +27,7 @@ void tzpc_init(void)

writel(DECPROTXSET, &tzpc->decprot0set);

writel(DECPROTXSET, &tzpc->decprot1set);

-

- if (cpu_is_exynos5() && (addr == end))

- break;

-

- writel(DECPROTXSET, &tzpc->decprot2set);

+ writel(0xbd, &tzpc->decprot2set);

writel(DECPROTXSET, &tzpc->decprot3set);

}

}

试验

最终patch,当然整个工程的源码可以在github下载到:

diff --git a/arch/arm/dts/exynos4210-origen.dts b/arch/arm/dts/exynos4210-origen.dts

index 65a5fcd..9f4875a 100644

--- a/arch/arm/dts/exynos4210-origen.dts

+++ b/arch/arm/dts/exynos4210-origen.dts

@@ -15,12 +15,13 @@

compatible = "insignal,origen", "samsung,exynos4210";

chosen {

+ stdout-path = "serial0";

bootargs ="";

};

aliases {

serial0 = "/serial@13800000";

- console = "/serial@13820000";

+ console = "/serial@13800000";

};

};

diff --git a/arch/arm/mach-exynos/clock_init_exynos4.c b/arch/arm/mach-exynos/clock_init_exynos4.c

index 584e4ba..fda1837 100644

--- a/arch/arm/mach-exynos/clock_init_exynos4.c

+++ b/arch/arm/mach-exynos/clock_init_exynos4.c

@@ -38,42 +38,39 @@

*/

void system_clock_init(void)

{

- struct exynos4_clock *clk =

- (struct exynos4_clock *)samsung_get_base_clock();

+ struct exynos4x12_clock *clk =

+ (struct exynos4x12_clock *)samsung_get_base_clock();

- writel(CLK_SRC_CPU_VAL, &clk->src_cpu);

+ /* APLL= 1400 MHz MPLL=800 MHz */

+

+ writel(0x01000001, &clk->src_cpu);

sdelay(0x10000);

- writel(CLK_SRC_TOP0_VAL, &clk->src_top0);

- writel(CLK_SRC_TOP1_VAL, &clk->src_top1);

- writel(CLK_SRC_DMC_VAL, &clk->src_dmc);

- writel(CLK_SRC_LEFTBUS_VAL, &clk->src_leftbus);

- writel(CLK_SRC_RIGHTBUS_VAL, &clk->src_rightbus);

+ writel(0x10, &clk->src_leftbus);

+ writel(0x10, &clk->src_rightbus);

+ writel(0x110, &clk->src_top0);

+ writel(0x1111000, &clk->src_top1);

+ writel(0x00011000, &clk->src_dmc);

writel(CLK_SRC_FSYS_VAL, &clk->src_fsys);

writel(CLK_SRC_PERIL0_VAL, &clk->src_peril0);

writel(CLK_SRC_CAM_VAL, &clk->src_cam);

writel(CLK_SRC_MFC_VAL, &clk->src_mfc);

writel(CLK_SRC_G3D_VAL, &clk->src_g3d);

- writel(CLK_SRC_LCD0_VAL, &clk->src_lcd0);

sdelay(0x10000);

- writel(CLK_DIV_CPU0_VAL, &clk->div_cpu0);

- writel(CLK_DIV_CPU1_VAL, &clk->div_cpu1);

- writel(CLK_DIV_DMC0_VAL, &clk->div_dmc0);

- writel(CLK_DIV_DMC1_VAL, &clk->div_dmc1);

- writel(CLK_DIV_LEFTBUS_VAL, &clk->div_leftbus);

- writel(CLK_DIV_RIGHTBUS_VAL, &clk->div_rightbus);

- writel(CLK_DIV_TOP_VAL, &clk->div_top);

+ writel(0x1160730, &clk->div_cpu0);

+ writel(0x506, &clk->div_cpu1);

+ writel(0x111113, &clk->div_dmc0);

+ writel(0x1011713, &clk->div_dmc1);

writel(CLK_DIV_FSYS1_VAL, &clk->div_fsys1);

- writel(CLK_DIV_FSYS2_VAL, &clk->div_fsys2);

+ writel(0x4070047, &clk->div_fsys2);

writel(CLK_DIV_FSYS3_VAL, &clk->div_fsys3);

writel(CLK_DIV_PERIL0_VAL, &clk->div_peril0);

writel(CLK_DIV_CAM_VAL, &clk->div_cam);

writel(CLK_DIV_MFC_VAL, &clk->div_mfc);

writel(CLK_DIV_G3D_VAL, &clk->div_g3d);

- writel(CLK_DIV_LCD0_VAL, &clk->div_lcd0);

/* Set PLL locktime */

writel(PLL_LOCKTIME, &clk->apll_lock);

@@ -81,10 +78,10 @@ void system_clock_init(void)

writel(PLL_LOCKTIME, &clk->epll_lock);

writel(PLL_LOCKTIME, &clk->vpll_lock);

- writel(APLL_CON1_VAL, &clk->apll_con1);

- writel(APLL_CON0_VAL, &clk->apll_con0);

- writel(MPLL_CON1_VAL, &clk->mpll_con1);

- writel(MPLL_CON0_VAL, &clk->mpll_con0);

+ writel(0x803800, &clk->apll_con1);

+ writel(0x80af0300, &clk->apll_con0);

+ writel(0x803800, &clk->mpll_con1);

+ writel(0x80640300, &clk->mpll_con0);

writel(EPLL_CON1_VAL, &clk->epll_con1);

writel(EPLL_CON0_VAL, &clk->epll_con0);

writel(VPLL_CON1_VAL, &clk->vpll_con1);

diff --git a/arch/arm/mach-exynos/dmc_init_exynos4.c b/arch/arm/mach-exynos/dmc_init_exynos4.c

index ecddc72..69e9fd6 100644

--- a/arch/arm/mach-exynos/dmc_init_exynos4.c

+++ b/arch/arm/mach-exynos/dmc_init_exynos4.c

@@ -32,19 +32,19 @@ struct mem_timings mem = {

.direct_cmd_msr = {

DIRECT_CMD1, DIRECT_CMD2, DIRECT_CMD3, DIRECT_CMD4

},

- .timingref = TIMINGREF_VAL,

- .timingrow = TIMINGROW_VAL,

- .timingdata = TIMINGDATA_VAL,

- .timingpower = TIMINGPOWER_VAL,

- .zqcontrol = ZQ_CONTROL_VAL,

- .control0 = CONTROL0_VAL,

- .control1 = CONTROL1_VAL,

- .control2 = CONTROL2_VAL,

- .concontrol = CONCONTROL_VAL,

- .prechconfig = PRECHCONFIG,

- .memcontrol = MEMCONTROL_VAL,

- .memconfig0 = MEMCONFIG0_VAL,

- .memconfig1 = MEMCONFIG1_VAL,

+ .timingref = 0x000000bb,//TIMINGREF_VAL,

+ .timingrow = 0x7a46654f,//TIMINGROW_VAL,

+ .timingdata = 0x46400506,//TIMINGDATA_VAL,

+ .timingpower = 0x52000a3c,//TIMINGPOWER_VAL,

+ .zqcontrol = 0xe3854c03,//ZQ_CONTROL_VAL,

+ .control0 = 0x7110100b,//CONTROL0_VAL,

+ .control1 = 0xe0000086,//CONTROL1_VAL,

+ .control2 = 0x00000000,//CONTROL2_VAL,

+ .concontrol = 0x0fff333a,//CONCONTROL_VAL,

+ .prechconfig = 0xff000000,//PRECHCONFIG,

+ .memcontrol = 0x00302640,//MEMCONTROL_VAL,

+ .memconfig0 = 0x40c01333,//MEMCONFIG0_VAL,

+ .memconfig1 = 0x80e01323,//MEMCONFIG1_VAL,

.dll_resync = FORCE_DLL_RESYNC,

.dll_on = DLL_CONTROL_ON,

};

@@ -124,6 +124,8 @@ static void dmc_init(struct exynos4_dmc *dmc)

writel(mem.memconfig0, &dmc->memconfig0);

writel(mem.memconfig1, &dmc->memconfig1);

+ writel(0x8000001F, &dmc->ivcontrol);

+

/* Config Precharge Policy */

writel(mem.prechconfig, &dmc->prechconfig);

/*

diff --git a/arch/arm/mach-exynos/exynos4_setup.h b/arch/arm/mach-exynos/exynos4_setup.h

index 38735f0..37ce464 100644

--- a/arch/arm/mach-exynos/exynos4_setup.h

+++ b/arch/arm/mach-exynos/exynos4_setup.h

@@ -505,7 +505,7 @@ struct mem_timings {

#define ADD_LAT_PALL (1 << 6)

#define MEM_TYPE_DDR3 (0x6 << 8)

#define MEM_WIDTH_32 (0x2 << 12)

-#define NUM_CHIP_2 (1 << 16)

+#define NUM_CHIP_2 (0 << 16)

#define BL_8 (0x3 << 20)

#define MEMCONTROL_VAL (CLK_STOP_DISABLE | DPWRDN_DISABLE\

| DPWRDN_TYPE | TP_DISABLE | DSREF_DIABLE\

@@ -514,16 +514,16 @@ struct mem_timings {

#define CHIP_BANK_8 (0x3 << 0)

-#define CHIP_ROW_14 (0x2 << 4)

+#define CHIP_ROW_14 (0x3 << 4)

#define CHIP_COL_10 (0x3 << 8)

#define CHIP_MAP_INTERLEAVED (1 << 12)

-#define CHIP_MASK (0xe0 << 16)

+#define CHIP_MASK (0xC0 << 16)

#ifdef CONFIG_MIU_LINEAR

#define CHIP0_BASE (0x40 << 24)

#define CHIP1_BASE (0x60 << 24)

#else

-#define CHIP0_BASE (0x20 << 24)

-#define CHIP1_BASE (0x40 << 24)

+#define CHIP0_BASE (0x40 << 24)

+#define CHIP1_BASE (0x80 << 24)

#endif

#define MEMCONFIG0_VAL (CHIP_BANK_8 | CHIP_ROW_14 | CHIP_COL_10\

| CHIP_MAP_INTERLEAVED | CHIP_MASK | CHIP0_BASE)

diff --git a/arch/arm/mach-exynos/tzpc.c b/arch/arm/mach-exynos/tzpc.c

index abe8e7f..63605d5 100644

--- a/arch/arm/mach-exynos/tzpc.c

+++ b/arch/arm/mach-exynos/tzpc.c

@@ -17,10 +17,7 @@ void tzpc_init(void)

start = samsung_get_base_tzpc();

- if (cpu_is_exynos5())

- end = start + ((EXYNOS5_NR_TZPC_BANKS - 1) * TZPC_BASE_OFFSET);

- else if (cpu_is_exynos4())

- end = start + ((EXYNOS4_NR_TZPC_BANKS - 1) * TZPC_BASE_OFFSET);

+ end = start + ((EXYNOS4_NR_TZPC_BANKS - 1) * TZPC_BASE_OFFSET);

for (addr = start; addr <= end; addr += TZPC_BASE_OFFSET) {

tzpc = (struct exynos_tzpc *)addr;

@@ -30,11 +27,7 @@ void tzpc_init(void)

writel(DECPROTXSET, &tzpc->decprot0set);

writel(DECPROTXSET, &tzpc->decprot1set);

-

- if (cpu_is_exynos5() && (addr == end))

- break;

-

- writel(DECPROTXSET, &tzpc->decprot2set);

+ writel(0xbd, &tzpc->decprot2set);

writel(DECPROTXSET, &tzpc->decprot3set);

}

}

diff --git a/include/configs/origen.h b/include/configs/origen.h

index 65e1c7c..f964456 100644

--- a/include/configs/origen.h

+++ b/include/configs/origen.h

@@ -46,7 +46,7 @@

/* MMC SPL */

#define COPY_BL2_FNPTR_ADDR 0x02020030

-#define CONFIG_SPL_TEXT_BASE 0x02021410

+#define CONFIG_SPL_TEXT_BASE 0x02023400

#define CONFIG_EXTRA_ENV_SETTINGS \

"loadaddr=0x40007000\0" \

@@ -63,21 +63,10 @@

"bootscript=echo Running bootscript from mmc${mmcdev} ...; " \

"source ${loadaddr}\0"

#define CONFIG_BOOTCOMMAND \

- "if mmc rescan; then " \

- "echo SD/MMC found on device ${mmcdev};" \

- "if run loadbootenv; then " \

- "echo Loaded environment from ${bootenv};" \

- "run importbootenv;" \

- "fi;" \

- "if test -n $uenvcmd; then " \

- "echo Running uenvcmd ...;" \

- "run uenvcmd;" \

- "fi;" \

- "if run loadbootscript; then " \

- "run bootscript; " \

- "fi; " \

- "fi;" \

- "load mmc ${mmcdev} ${loadaddr} uImage; bootm ${loadaddr} "

+ "load mmc 0 0x40007000 uImage;" \

+ "load mmc 0 0x48000000 ramdisk.img;" \

+ "load mmc 0 0x42000000 exynos4412-tiny4412.dtb;" \

+ "bootm 0x40007000 0x48000000 0x42000000"

#define CONFIG_CLK_1000_400_200

@@ -87,8 +76,9 @@

#define CONFIG_SYS_MMC_ENV_DEV 0

#define CONFIG_ENV_SIZE (16 << 10) /* 16 KB */

#define RESERVE_BLOCK_SIZE (512)

-#define BL1_SIZE (16 << 10) /*16 K reserved for BL1*/

-#define CONFIG_ENV_OFFSET (RESERVE_BLOCK_SIZE + BL1_SIZE)

+#define BL1_SIZE (8 << 10) /*8 K reserved for BL1*/

+#define BL2_SIZE (16 << 10) /*16 K reserved for BL2*/

+#define CONFIG_ENV_OFFSET (RESERVE_BLOCK_SIZE + BL1_SIZE + BL2_SIZE)

#define CONFIG_SPL_MAX_FOOTPRINT (14 * 1024)

@@ -99,4 +89,12 @@

#define BL2_START_OFFSET ((CONFIG_ENV_OFFSET + CONFIG_ENV_SIZE)/512)

#define BL2_SIZE_BLOC_COUNT (COPY_BL2_SIZE/512)

+/* uart0 debug for spl */

+#define CONFIG_SPL_SERIAL_SUPPORT

+#define CONFIG_SPL_GPIO_SUPPORT

+#define CONFIG_DEBUG_UART

+#define CONFIG_DEBUG_UART_S5P

+#define CONFIG_DEBUG_UART_BASE 0x13800000 /* UART0 base address */

+#define CONFIG_DEBUG_UART_CLOCK (100000000) /* SCLK_UART0 is 100MHz */

+

#endif /* __CONFIG_H */