【晶体管电路设计】一、晶体管设计概述与共射极放大电路

晶体管设计概述与共射极放大电路

一、概述

晶体管放大电路是模拟电路的核心部分,也是当下大多数集成运放的基本原理。通过学习铃木雅臣的《晶体管电路设计》,希望能对晶体管设计电路有较深入的了解,并对模拟集成电路设计打好基础。

二、晶体管放大原理

晶体管是电流控制器件,通过改变基极电流,可以对集-射极电流进行控制。在常用的电压放大场合下,这种放大效应来源于用电阻将电流转换为电压。在小信号模型分析法中,基极电流的来源是输入电压与基射极动态电阻rbe的比值。rbe通常为kΩ级,故在小信号情形下基极电流很小,可能只有零点几个mA。通过晶体管的放大作用,基极电流以β倍产生在集射极间。以共射极放大电路为例,以上关系可以表示为:

(笔误!图中Re应为Rc)

△Vi/rbe=△ib

从而,集电极产生一个β倍于ib的电流:

△ie=β△ib

进而,输出电压即可通过相对正电源电位来得到:

△Vo=VCC-△ieRc=VCC-β△ibRc=VCC-△Vi·Rc/rbe

从而,我们通过交流耦合以及控制集电极电阻Re,可以得到反相的放大的电压信号。但一般发射极会有一个控制增益的电阻,故上述公式并不实用;在非极端情况设计电路时,我们往往希望电路能对大多数通用晶体管工作,故考虑避免rbe这种依赖元件参数的参量存在于我们的计算中。

同时,在具体计算时考虑基极电流是很繁琐的事情,故在一般设计过程中,以近似计算的方式忽略基极电流的存在(但在某些电路中,虽然忽略了基极电流,但使电路工作仍需要给基级一定的电流驱动)。增益的计算也从rbe设计为外电路电阻。

此外,基射极管压降VBE也是一个非常重要的参量,一般等于0.6V(硅管)。晶体管电路的参数能够由VBE=0.6V和欧姆定律全部求出。

晶体管电路的繁琐之处还在于静态工作点的设置,通常,不仔细的设计会造成输出波形的削波失真。这个问题在设计的初期就可以完美解决。还有很多的经验数值的选取值得学习和记忆。整体设计思路是:定量确定电压和电流,来计算电阻。而且一些关键的电压和电流都有经验值或者由手册提供。

三、共射极放大电路设计

共射极放大电路是典型的反相放大器,应用广泛,效果稳定。首先先把整体设计思路展示出来,再分步骤来解释设计的目的和原理。

1、设计步骤

- 确定供电电压VCC,根据频率曲线/噪声曲线/其他来确定静态发射极电流IE;

- 确定VE,此处VE选取1~2V以吸收温漂;

- 根据VE和IE,计算射极静态电阻RE(认为IE≈IC);

- 确定放大倍数Av,并应用关系Av=RC/RE计算集电极静态电阻RC。至此,静态工作点建立完毕;

- 审查静态工作点是否符合要求:正输出摆幅限=VCC-IE·RC,负输出摆幅限=IE·RC-VE。要保证放大后的输出电压不会超过摆幅限(一般上摆幅限大一些),RC过大会有下侧削波,RC过小会有下侧削波;此外还要确定功率是否超额:PC=VCE·IC;

- 下面确定基极偏置电压:根据VBE=0.6V,易得VB=VE+0.6;通过电阻从电源处分压。由于认为ib较小可忽略,故流经基极分压电阻(上图中R1,R2)的电流IB0应远大于ib。ib近似计算为IC/β,IB0比ib大一个数量级左右即可,故R2=VB/IB0,R1=(VCC-VR2)/IB0;

- 最后确定交流耦合电容值、电源去耦电容值即可。

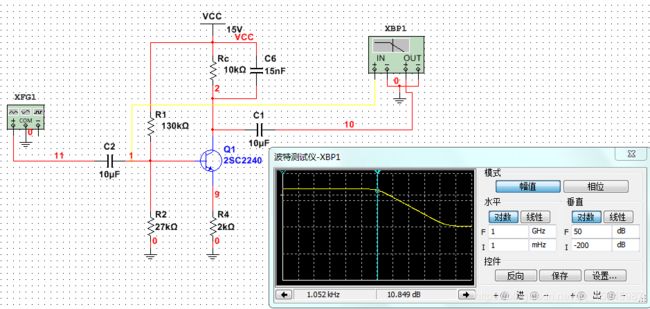

下面先通过一个设计好的共射极放大电路来直观了解下各部分的波形:

如图,电路使用2SC2240管,15V供电,输入输出做交流耦合。各处输出信号如下:浅蓝色波形为输入信号,选择的是1kHz,1Vpp的正弦波,绿色是输出信号,放大5倍左右,而且是反相;蓝色为基极信号,可以看出由于基极偏置电阻的影响,直流电平被抬高;红色为射极信号,与基极信号仅相差一个固定值。

2、电路原理的分析

我们来分析该电路。

首先,进行直流分析,也就是确定静态工作点。在开头的设计流程里,对静态工作点的设计与验证也是首先进行的。根据基极偏置电阻能轻松地算出基极静态电位,根据基射极管压降为常数能确定射极静态电位。从而,根据射极电阻的大小,能求出集射极电流的大小,进而根据电源电压求出集电极静态电位。

为何静态工作点很重要呢?以NPN型晶体管为例,它相当于是两只背靠背的二极管;要想使二极管工作,就要给它合适的偏置以使其合理的导通:基-集二极管是防止内反馈的(其实也引起了内反馈),而基-射极二极管是实现放大的关键。也就是说,设计一种外部电路,使得电流在基-射极二极管中正常流动就可以了。这个思路在射极跟随器带载能力分析中还会提到。

下面求交流电压增益:当输入电压变化△vi时,会引起发射极电流产生交流变化△ie,由于基射极压降是常数,故没有在交流变化中作出贡献,故△ie=vi/RE。从而射极交流输出电压可以确定为vo=△ieRC=vi·RC/RE,从而交流增益为Av=RC/RE。这一结论可以快速分析共射极电路的放大倍数。

输出电源轨分别是VCC和VE,这是由三极管工作时电流特性决定的,且一般没有轨到轨输出。根据输出电源轨和交流放大倍数,就可以对电路进行使用了。

※当输入输出没有进行交流耦合时,输入(尤其是有直流的)会导致输出波形失真。

3、共射极电路的一般设计

了解了电路特性,就可以按照本节开始的设计步骤对共射极电路进行设计了。在分析过程中已经确定了静态工作点和放大倍数,下面对其他部分进行设计。

- 供电电压:根据输出电压的摆幅,我们可以确定电压的大小。通常取电源电压比输出峰峰值大一些;

- 晶体管:根据工作频率、所需功率、噪声大小和β等选择合适的晶体管;

- 发射极电流:通过查阅器件手册,根据频率特性等来确定发射极电流的大小;

- RC和RE:通过射极电压和电流、以及放大倍数来确定,注意审查摆幅上下限以及额定功率;

- 基极偏置电阻:根据VE确定VB,从而确定电源分压电阻。注意流过分压电阻的电流应高过基极电流一至两个数量级,基极电流通过集射极电流除以β算得;

- 耦合电容:交流耦合电容一般取10uF,注意输出级的耦合电容会和下一级的输入阻抗形成高通滤波器,要慎重处理该滤波器的截止频率。

4、电路性能参数

通过交流分析的方法,我们可以求得设计好的电路的一些特性参数,如输入输出阻抗、放大倍数等。

- 输入阻抗:根据交流分析,输入阻抗为基极偏置电阻的并联值;在小信号分析中,还应并联基射极动态电阻rbe;

- 输出阻抗:测定输出阻抗的方法是,给电路加上负载,当输出峰峰值降至空载的一半时,负载阻抗即为输出阻抗。一般共射极放大电路输出阻抗即为集电极电阻RC;

- 放大倍数:由于基极电流的影响(在计算中忽略了),实际放大倍数要比设计值低10%左右,设计公式是比较实用的。

这一部分介绍较为简略,读者可自行设计电路研究。

四、共射极放大电路拓展

对一般的共射极放大电路进行改进,可以获得具有其他特性的各种应用电路。本节介绍提高放大倍数的手段、低压供电电路、差分输出电路、调谐放大电路。

1、提高放大倍数

根据设计电路部分介绍,电压增益主要由集电极电阻RC与发射极电阻RE比值决定,故很自然地想到改变电阻的比值来改变增益;然而问题随之而来:这两个电阻同时负担着确定直流工作点的任务,如果随意改动,则电路很可能失真甚至不工作。

换个角度想,电压增益属于“交流分析”范畴,而静态工作点属于“直流分析”,那么给电路加一些电抗性元件,让交流视角下的比值发生改变,而直流分析时的电阻值不变即可。

通过给射极电阻并联电容,或者拆分电阻并联电容可以达到此目的,如对第一节里的电路进行修改:

关注上图的发射极:在交流分析时,电阻R4被电容短路,此时等效地认为射极电阻只有R7(330Ω)。由信号源与示波器显示,此时信号放大了将近50倍!要比原有设计值(10k/2k=5)大得多,从而实现了电压增益的扩大。如果不将原来射极电阻拆分,而是整个被电容并联,此时将获得最大增益βRC/rbe。

电容容值如何选取呢?要注意,并联电容后,整个电路将具有高通特性,截止频率为f=1/2πRC,如果不需要此高通特性,C容值可选择较大值,47uF~100uF均可。

此外,电容C6的存在还有温度补偿的作用。

2、低压低损耗电路

运放电路若用一节干电池(1.5V)供电有些不太现实,但晶体管电路是可以做到的,关键是利用外加二极管的导通压降抵消基射极电压,并将各部分电流设计小一些。下图电路即使在1.5V供电下仍能将小信号按设计放大:

但缺点是系统最大电压始终在供电电压之下,除非采用其他方法,但电路损耗较小,适合低功耗工作。

3、差分输出电路

全差分运放可以提供双模的输出,而许多传输线路也需要差分传递。晶体管电路也能进行差分输出,除了用到共射极放大电路原理之外,还用到射极输出器的原理。下图展示了差分输出的电路连接:

可见输出了两路形状相同、相位反相的差分信号,集电极信号与输入信号等大反相,射极输出信号与输入信号同相。但是两路信号由于引出的位置不同,故输出阻抗也不同,反相输出的输出阻抗较高(为RC),同相输出的输出阻抗较低,适合驱动负载。反相输出一般接射极输出器后再进行驱动。

此外,基极静态电位尽量设置在VCC与GND中间,以扩大不失真输出范围。

4、滤波器与调谐放大电路

在电路里引入电抗元件,会使电路性质随频率的变化而变化,我们可以利用这种性质设计LPF、HPF,以及高频电路中常用的调谐放大电路。本质上,是利用了电抗元件阻抗随频率变化而变化的特性,进而改变当前频率下的电压增益,往往利用谐振频率处阻抗呈纯阻性且有极值的特点实现选频放大。下面展示了低通、高通和特定频点的选频放大器:

①LPF:

如图构建了一个低通滤波器(bode测试仪的输入放在了基极而不是信号发生器的输出,是因为输入耦合电容会与输入电阻形成高通滤波器,影响观察效果),其截止频率约为1.06kHz,由f=1/2πRcC计算得到。

由正弦稳态分析,RC并联回路阻抗为R/√(1+(wRC)^2),随频率增大,阻抗减小,从而电压增益减小,形成了低通特性。

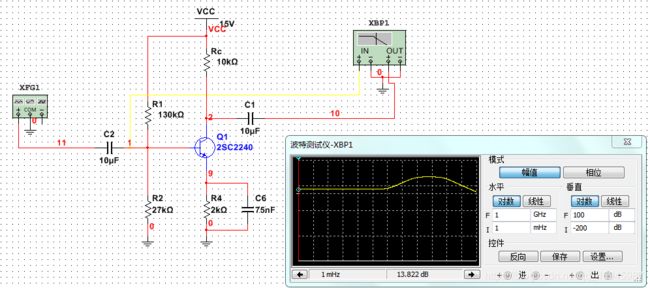

②HPF:

如图构建了一个高通滤波器,其截止频率的计算和LPF类似。

在增益峰点,电压增益达到了50dB,接近晶体管的β值,之后由于晶体管频率特性变差,增益发生衰减。

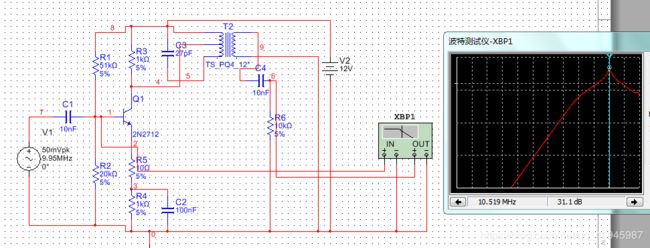

③10.7M选频放大:

将RC替换为谐振频率为10.7MHz的LC网络,可以得到选频放大器,如图所示在10.7M处放大倍数达35dB,而失谐1MHz时的放大倍数就仅有12.6dB。缺点在于通频带稍宽,矩形系数不够好,回路等效品质因数约为65.2,是比较大的。此外,高频去耦电容改成了1uF。

获得了来自老师的一份谐振放大电路,也贴在此处:

五、总结

晶体管放大电路是构成运放电路的基础,而共射极组态是最为常用的放大电路形式。借鉴运放的放大倍数能由两个电阻比值轻松确定的特点,共射极放大器的增益也可以用两电阻比值来近似。对于一般分析时较为头痛的静态工作点,也能用一种比较直观的方式去理解。当对电路的性质有了整体把握,那么对电路的设计也就水到渠成。不过本文的设计方法建立在工程上的近似基础上,对于理论分析或者极端情况下的应用还要参考小信号模型与器件手册。

鄙人水平有限,错漏之处,还请赐教!

风扬江渊

2020.3.21