Vivado入门笔记-SOC-快速入门

简介

开发板:zedbord,其实任意zynq系列,开发流程都差不多。这里通过简单的示例,一步一步操作,就会学会怎么建立SOC架构,并完成配置。

这里创建的是zynq系列soc的最小系统架构,如此可以更方便的理解其体系架构,以及与传统开发的联系。

1. 创建RTL工程

VIvado传统RTL开发的基本流程,略

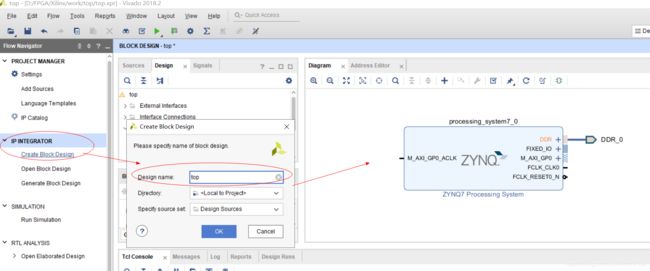

2. 创建IP Integrator Block Design

VIvado传统RTL开发的基本流程,略

创建bd文件:

3. 添加zynq 处理器

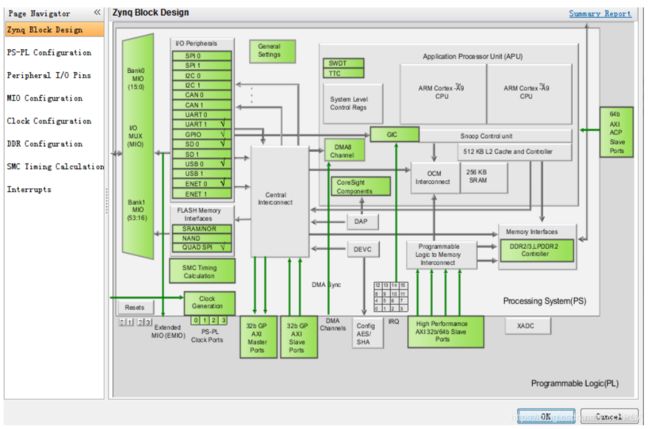

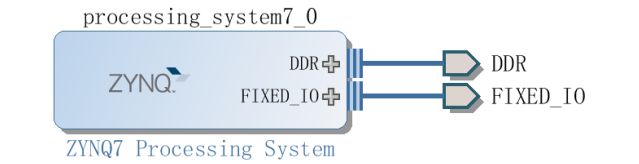

ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。但此时处理是完全未经过配置的,双击处理器进行配置。

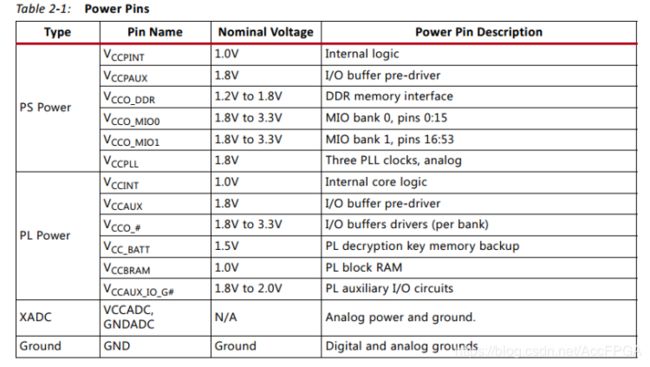

自动添加的外部接口:(参考ug585文档)

FIXED_IO, 是专用的内部固化的外设IO,作用?

54个MIO口,

DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide.

PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence.

PS_CLK: System reference clock

PS_PORB: Power on reset, active low

DDR接口,处理器ddr内存寻址接口;

M_AXI_GP0_ACLK,

M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择

FCLK_CLK0: PL Pabric Clocks,不使用可在Clock Configuration 中disable。

FCLK_RESET0_N:时钟复位使能,可在General中disable 。

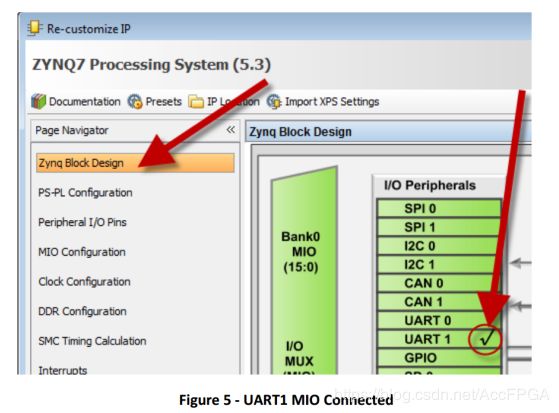

4.配置processing System

配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual

http://www.xilinx.com/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf

通用配置:

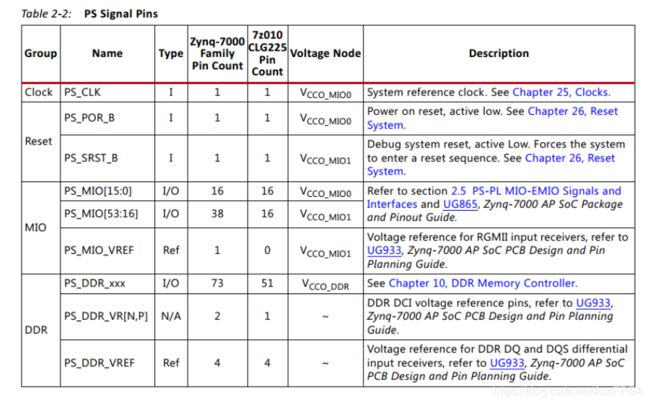

(1) MIO配置:

Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

UART1映射到MIO[48:49] zedboard

Bank 0 IO Voltage:LVCMOS 3.3V zedboard

Bank 1 IO Voltage:LVCMOS 1.8V zedboard

PS与PL电源部分是完全独立,但是无论什么时候有PL电源供电就必须有PS电源供电。PS电源部分为DDR IO口独立供电,还为MIO的两个独立的分区Bank0与Bank1供电。

PS专用的信号pin汇总表2-2,注意,对于MIO pin允许的输入电压取决于slcr, MIO_PIN_xx[IO_Type]和[DisableRcvr] bits, 约束条件被定义在Zynq-7000 AP SoC data sheets, 超出限制的电压输入可能损坏输入buffer。

(2)核对IO配置

选择Zynq Block Design,注意UART1是否已经在IO特性中被连接。

注意勾上:GPIO,以使其它的MIO口能够作处理器的GPIO使用。

(3)General Setting常规设置:设置端口特性

在Zynq Block Design中选择General Setting或在PS-PL Configuration中设置。设置UART1 波特率。

(4)配置Memory和Clocks

即使一个简单的Hello World程序被运行,一些不可缺少的PS elements也必须被配置,它包括DDR3 Memory(用来执行PS应用程序),另外系统时钟也必须被配置。

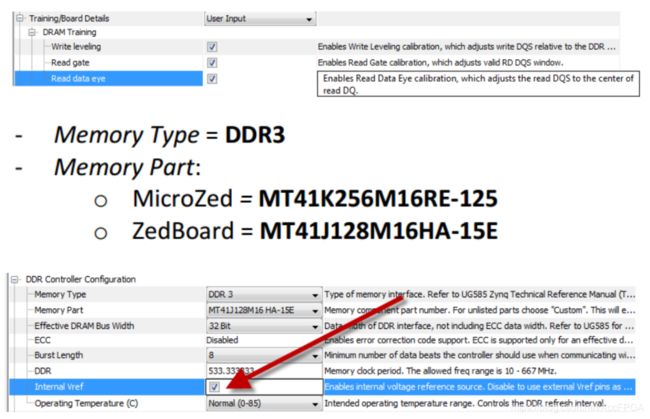

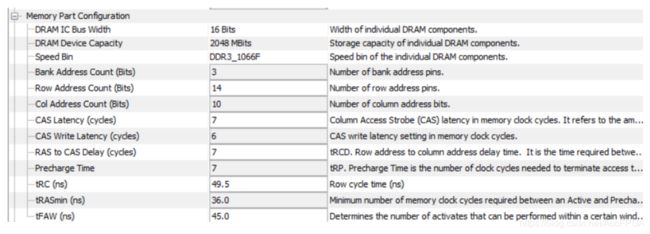

DDR3为zed board开发板上的IC25与IC26,MT41K128M16JT_125.

Clock Configuration: 默认时钟频率与ZedBoard和MicroZed匹配:

IO Peripheral CLocks被指定(SPI、QSPI、CAN、SMC、SDIO、ENET),选择后如何更改,例如SPI?

如果不用FCLK_CLK0,可废除PL Fabric Clock, 同时还需废除AXI connection to the PL,在PS-PL Configuration中的取消对GP Master AXI Tnterface的选择。

也可在PS-PL Configuration中取消对FCLK_RESET的选择。

SPI:时钟要求比cpu_1x频率111.1111Mhz更大,可设160Mhz,然后4分频为10Mhz

使能DDR Configuration:必须设置为PCB使用的DDR设置。因为使用2x16 DDR3配置,所以在DDR Controller Configuration中设置游戏的DRAM总线宽度为32bits。

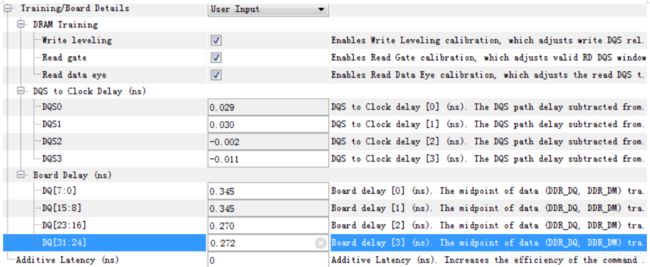

DRAM Training必须全被使能和设置:write level,read gate,read data eye。

保存后完成最小系统设置:其中内部设置的UART1引脚内部设置,未显示出来,其实包含在了FIXED_IO。

展开FIXED_IO可查看被固定的IO口包含了哪些IO口:包含了含有串口UART1的MIO口、处理器的时钟口......。

(5)完成IP 集成文件(bd文件)

完成处理器配置后,为了便于bd文件作为工程的子模块,可以将bd文件例化为HDL文件。展开design Sources,右键点击bd文件创建HDL wrapper。再把HDL文件设为顶层文件或例化在其它工程中。

5.输出设计到SDK(software development kit)

5.1 输出到SDK前先完成硬件设计

在FLow Navigator中点击Generate Bitstream,如没有综合和实现,软件将自动综合布线后产生二进制文件。

Bitstream产生完成后,选择Open Implemented Design才能使能Vivado输出bitstream到SDK。

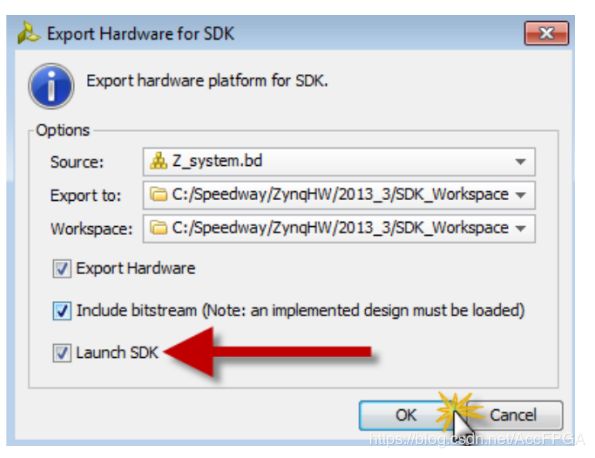

输出到SDK:File —>Export —>Export Hardware for SDK…

5.2 输出到SDK后产生的文件

产生文件夹hw_platform_0

产生文件:

System.xml, 包含系统的地址映射

ps7_init.c和ps7_init.h, 包含ZYNQ processing system初始化代码和DDR,Clocks,PLL,MIO的初始化设置。

ps7_init.html, 将初始化等设置以网页的格式显示出来。

?_wrapper.bit, implemented设计时,PL bitstream产生的二进制文件,用于初始化PL。

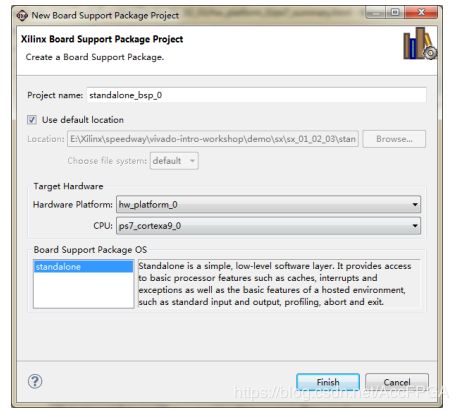

5.3 SDK中创建硬件级支持包(Board Support Package)常规默认设置即可

点击完成后弹出支持包设置

设置标准输入输出设备:stdin、stdout自动设置为uart_1,添加其他外设时可以更改。

设置驱动包:自动列出驱动,不需要的驱动选择‘none’

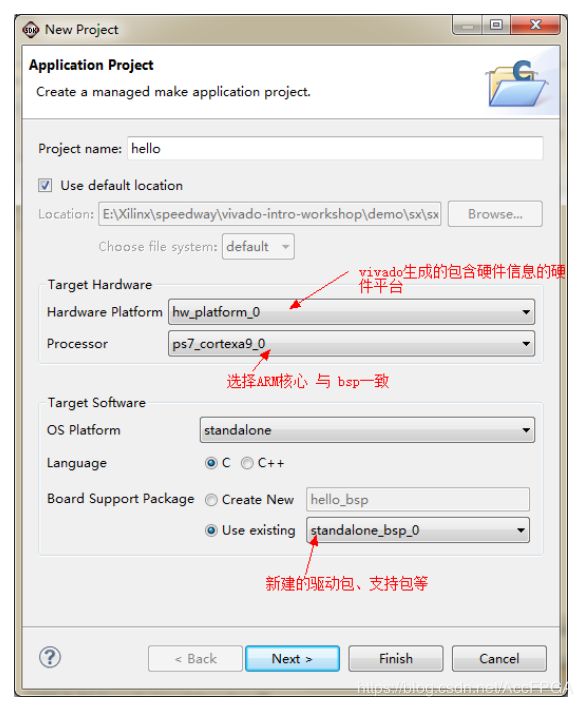

5.4 新建Application Project,使用existing的Board Support Package

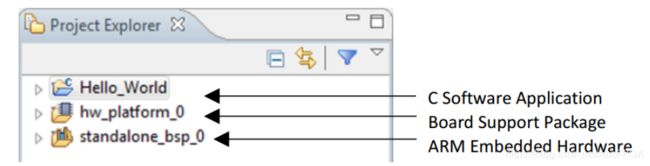

5.5 一个软件工程包含了3个部分:硬件信息、驱动包、软件包

5.6 运行调试程序 右键点击Hello应用程序run as--->run configurations

(1)选择Xilinx C/C++ Application(GDB)然后点击New图标。

(2)选择STDIO连接,连接到Console。如不选择,则直接输出到串口上。

(3)编译完成,生成二进制elf文件。点击Apply和Run,工具编译好下载elf文件到DDR。

JTAG模式:设置MIO2~6为00000

5.7 上电启动配置 利用FSBL模板建立FSBL的boot程序

(1)建立boot启动程序:

新建应用工程Application Project,选择FSBL模板。应用要求xilffs library库支持,如未在建立Board Support Package 时选择该库,可右键点击standalone_bsp_0选择Board Support Package设置。建立完成即可,默认设置。

输出在fsbl程序的Properties>C/C++ Build>Settings>ARM gcc compiler>添加两 个符号:RSA_SUPPORT和FSBL_DEBUG_INFO(用于打开FSBL的输出,可选)>apply>ok。

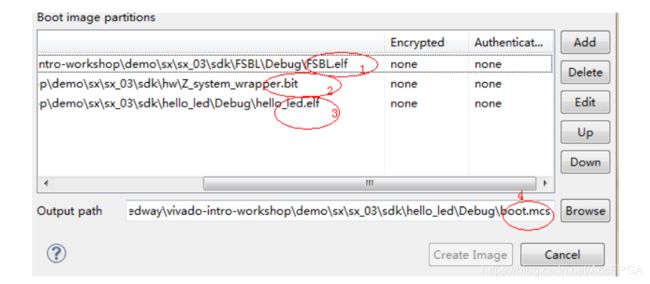

(2)使用Xilinx Tools/Create Zynq Boot Image命令建立镜像文件。

首先在FSBL elf的Browse中选择Boot.elf,该文件会自动添加到下边的文件列表中。然后添加Bitstream,在hw下;再添加LED_Dimmer.elf文件。三者的顺序不能颠倒。最后Create。(需要先编译工程Project—>build all)。在boot image partitions中添加bootloader类型的FSBL生成的.elf文件;添加hw_platform中的硬件.bit二进制文件; 添加软件工程生成的.elf文件;

(3)使用xilinx-tool/Program Flash.选择qspi single,offset可以不填写内容。Program.

(4) 下载文件:QSPI—Flash对应.MSC文件,SD card对应.bin文件

6 其它操作

Zedboard Processing System配置:

最重要的外设配置是boot device,ZYNQ允许使用QSPI、NOR/NAND、SD Card。

QSPI: QSPI固定使用MIO[1-6,8], 其中MIO8为feedback clk, 通常应勾选上。如果有灵感QSPI,选择Dual配置。注意:SRAM/NOR/NAND Flash接口不能被配置,是因为ZYNQ PS仅仅允许一个存储器接口。

USB0: MIO28-39,LVCMOS1.8V

以太网ENET0: MIO[16-27], LVCMOS 1.8V MDIO——MIO[52-53]

SDCARD: SD0——MIO[40-45]; CD=MIO47; WP=MIO46

预设为Zedboard默认值:Presets—>Zedboard

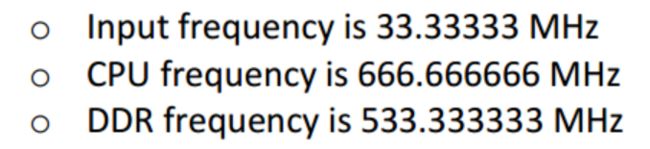

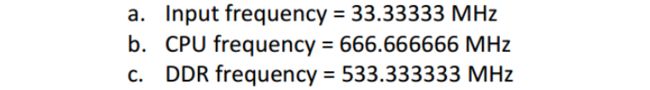

设置PS PLL CLocks:有三个PLL-ARM,DDR和IO,每一个在Zedboard上都使用同样的输入参考时钟33.3333MHz。PLL输出设定好后可以更改为整数倍的其它时钟。

例如:

ARM PLL——1333.33MHz(33.333MHz*40)

DDR PLL——1600MHz(33.333Mhz*48)或1066.667MHz(33.3333*32)

QSPI可设置为200MHz

PS能够驱动4个不同时钟频率给PL例如:

7 绑定PL管脚 管脚约束

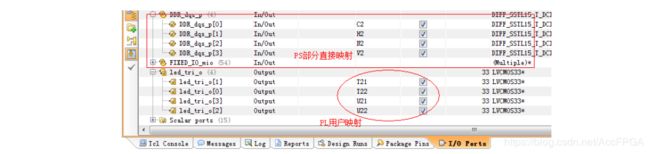

PS部分使用的I/O直接由软件配置,综合后可在I/O Planning中直接查看。

如DDR部分与FIXED部分,为PS指定I/O,综合后直接映射到对应I/O,不需用户单独指定。

方法一:I/O Planing

(1)打开Synthesized Design

(2)菜单Layout——>I/O planing

方法二:xdc约束文件

- 注释语句,语句前加“#”

- IO位置: set_property PACKAGE_PIN

[get_ports ] - IO电平标准:set_property IOSTANDARD

[get_ports ]

例:set_property PACKAGE_PIN U14 [get_ports led1s]

set_property IOSTANDARD LVCMOS33 [get_ports led1s]

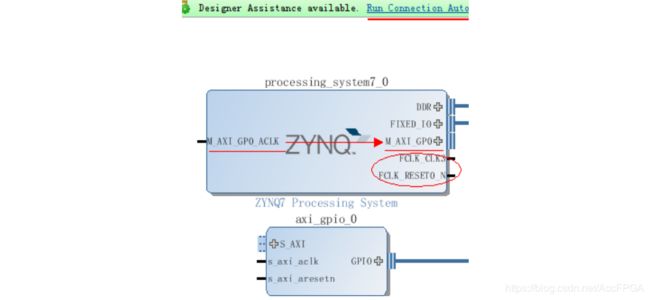

8. 使用GP AXI总线(需要配置的AXI Master,FCLK,FCLK_RESET)

These interfaces are for general-purpose use only and are not intended to achieve high performance.

-

配置,使能AXI Master总线,同时必须为AXI Master配置一个FCLK时钟,和一个FCLK_RESET复位信号。

- 配置完成后处理器增加两个端口:M_AXI_GP0,M_AXI_GP0_ACLK。

- 与两个必须的辅助AXI的信号端口:FCLK_CLK,FCLK_RESET。

-

在bd文件中添加ip: axi_gpio

-

运行自动连接

-

添加Port,连接到axi_gpio的输出口。

5. SDK操作外设AXI_GPIO

- 查找外设:点击system.mss,可以找到外设的驱动和例程,axi_gpio_0,Examples(点击);打开xgpio_example.c。 (板级驱动包standalone_bsp_0中的system.mss对系统使用的驱动包进行了说明)

- 添加头文件:复制examples中的头文件: xparameters.h,xgpio.h;

- 查找外设ID:打开xparameters.h,可以通过右键点击程序中的头文件,选择open declaration打开。XPAR_AXI_GPIO_0_DEVICE_ID。Xparameters.h文件由libgen库自动产生,包含了处理器的各个外设的驱动地址与访问ID

- 访问函数:在头文件xgpio.h中查询xgpio的驱动函数,或参考example。

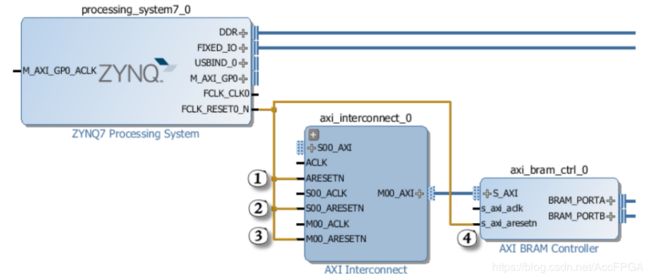

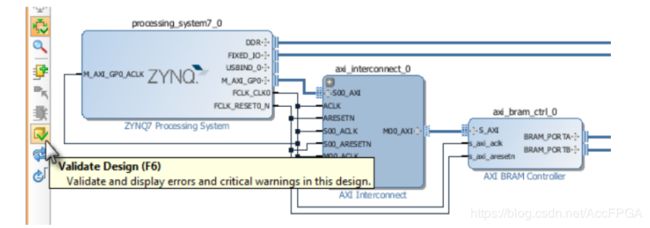

6. AXI BRAM Controller 与AXI Interconnect,

- 在处理器中增添端口:

- 32b GP AXI Master Ports,选择M AXI GP0 Interface

- 选择Clock Configuration,使能FCLK_CLK0,设置为50MHz

- 选择PS-PL Configuration,在General的时钟复位中使能FCLK_RESET0_N

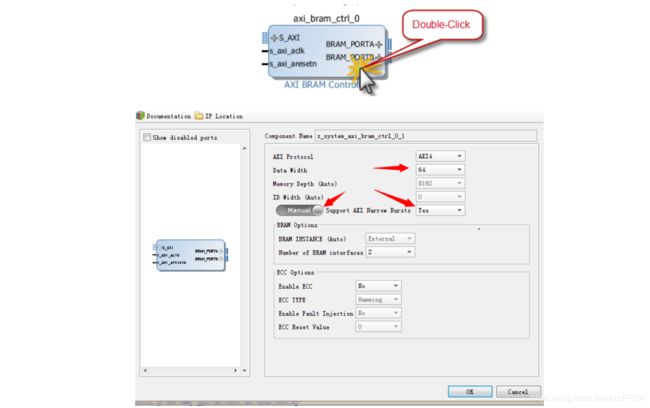

- 使用BRAM控制器,添加IP(AXI BRAM Controll):

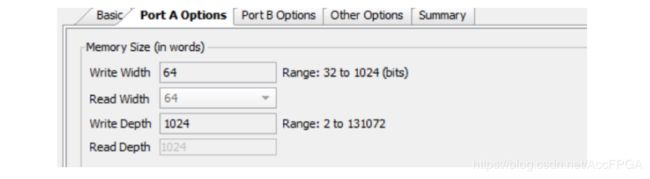

- 设置BRAM控制器:

- 增加数据宽度到64bits,点击OK

- ID Width(Auto)设置成Yes,以支持AXI Narrow Bursts。如果不能设置,将虚拟开关指到Manual再进行设置。

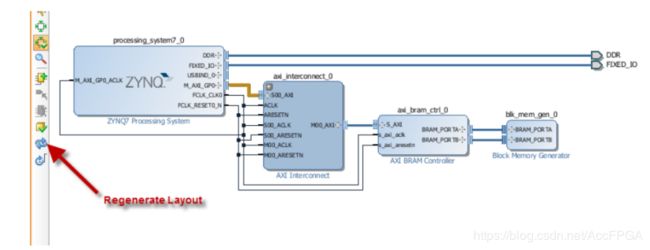

3. 添加存储器IP并双击进行设置:Block Memory Generate

a)选择True Dual Port

b)设置数据宽度:不能设置,默认32bits

4. 添加IP模块:AXI Interconnect,设置interface数量

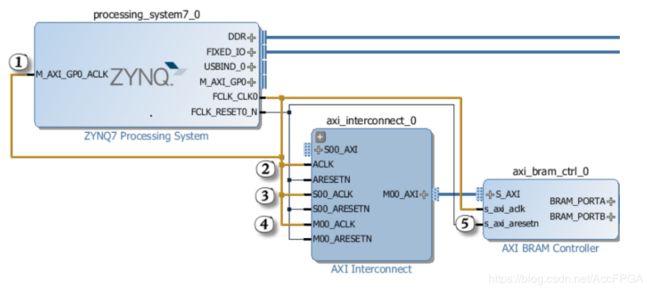

5. 连接各模块:

(1)连接复位:

(2)连接时钟:

(3)连接总线,重新产生布线:

6. 为BRAM在AXI总线上创建地址空间。

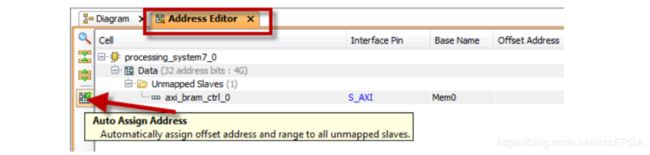

编辑Address Editor >Auto Assign Address

7. 使设计有效化

8. 双击blk_mem模块,点击Port A和Port B选项卡,看数据的宽度的深度,此时已经自动变为64bits宽度。

9. 保存BD文件,创建 HDL Wrapper文件,选择Generate Bitstream。

没使用PL部分,则不用引脚分配,PS部分的引脚在配置时已经指定。

9. 技巧

1. 使用语言模板

在Vivado文本/代码编辑窗口中,点击 ![]() 显示语言模板窗口(Language )

显示语言模板窗口(Language )

2.分析工具

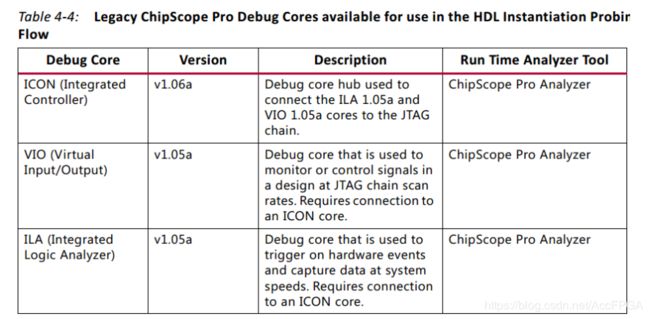

ISE工具:ChipScop Pro Analyzer

See the ChipScope Pro Software and Cores User Guide (UG029)for more information about debugging an ISE Design Suite project.

http://www.xilinx.com/support/documentation/sw_manuals/xilinx14_6/chipscope_pro_sw_cores_ug029.pdf

Vivado工具:Vivado Lab Tool

Programming and Debugging(UG908) [Ref 17]for more information.

3.逻辑分析仪Debugging Logic Designs in Hardware

在设计中使用调试核,则可以在硬件中运行时间逻辑分析器来调试设计。有两种方法:

• ChipScope™ Pro Analyzer: used with ICON v1.x, ILA v1.x, VIO v1.x, and IBERT v2.x debug

cores.

• Vivado® logic analyzer feature: used with new ILA v3.x, VIO v3.x, JTAG-to-AXI Master,

and IBERT 7 Series GTH/GTP/GTX/GTZ v3.x debug cores.