Vivado使用技巧(16):IO延迟的约束方法

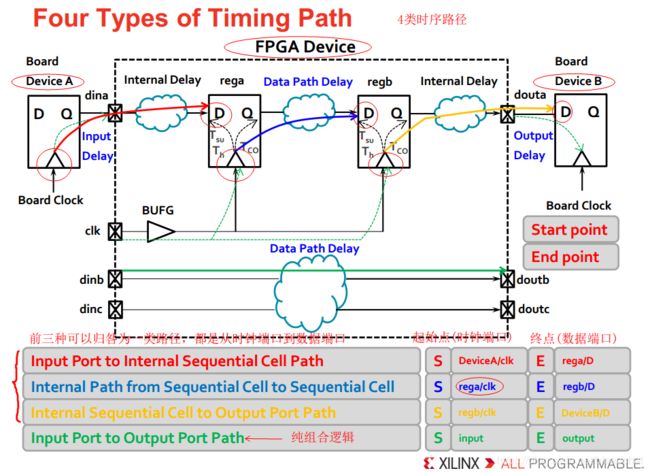

为了对设计外部的时序情况进行精确建模,设计者必须设定输入和输出端口的时序信息。Vivado只能识别出FPGA器件范围内的时序,因此必须使用set_input_delay和set_output_delay命令来设置FPGA范围外的延迟值。两者在含义、约束命令等方面有很多地方是相似的,只不过一个是输入,一个是输出,本文还是分开对两者进行讲述;

输入延迟

set_input_delay命令设定FPGA的输入端口上相对于上游芯片接口时钟边沿的输入路径延迟(不包括FPGA输入端口到第一个触发器数据输入端的延时);输入延迟既指数据从外部芯片经过板级传输到FPGA输入管脚间的相位差,也指相对参考板级时钟间的相位差;输入延迟值可以是正的,也可以是负的,由时钟和数据在FPGA接口处的相对相位决定;

约束时的相对时钟可以是一个设计时钟,也可以是一个虚拟时钟;输入延迟命令的选项包括:

- -min和-max:-min设定的值用于最小延迟分析(保持时间、移除时间);-max设定的值用于最大延迟分析(建立时间、恢复时间);如果约束命令中没有使用这两个选项,输入延迟值会同时应用于min和max;

- -clock_fall:用于指定由相对时钟的下降沿启动的时序路径上的输入延迟约束;如果没有这个选项,Vivado只假定使用相对时钟的上升沿;

- -add_delay:该选项通常用于约束与多个时钟沿相关的输入端口(比如DDR接口),而且必须已经存在一个最大或最小输入延迟约束,设计者使用该命令为同一端口设置其它相对时钟沿的最大或最小输入延迟约束;

输入延迟约束只能应用于输入端口或双向端口(不包括时钟输入端口),不能用于设计内部的管脚,下面给出几个使用输入延迟约束的典型例子:

1.示例一

create_clock -name sysClk -period 10 [get_ports CLK0]

set_input_delay -clock sysClk 2 [get_ports DIN]定义一个主时钟sysClk作为输入延迟的相对时钟,设定的值同时作为最小值(min)分析和最大值(max)分析;

2.示例二

create_clock -name clk_port_virt -period 10

set_input_delay -clock clk_port_virt 2 [get_ports DIN]该例子约束目的与上例相同,只是相对时钟换为一个虚拟时钟;使用虚拟时钟的好处是可以在不改变内部设计时钟的情况下,设定任意的抖动和延迟 ;

3.示例三

create_clock -name sysClk -period 10 [get_ports CLK0]

set_input_delay -clock sysClk -max 4 [get_ports DIN]

set_input_delay -clock sysClk -min 1 [get_ports DIN]该例中最小值分析和最大值分析采用不同的输入延迟值;

4.示例四

create_clock -name sysClk -period 10 [get_ports CLK0]

set_input_delay -clock sysClk 4 [get_ports DIN]

set_output_delay -clock sysClk 1 [get_ports DOUT]如果两个I/O端口之间仅有组合逻辑路径,没有任何时序单元,必须相对于虚拟时钟为I/O端口定义输入与输出延迟。上例中DIN和DOUT之间的组合逻辑路径约束为5ns(10-1-4);

5.示例五

create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_IN]

set_input_delay -clock clk_ddr -max 2.1 [get_ports DDR_IN]

set_input_delay -clock clk_ddr -max 1.9 [get_ports DDR_IN] -clock_fall -add_delay

set_input_delay -clock clk_ddr -min 0.9 [get_ports DDR_IN]

set_input_delay -clock clk_ddr -min 1.1 [get_ports DDR_IN] -clock_fall -add_delay这里相对时钟为DDR的时钟,最小值分析和最大值分析采用不同的输入延迟值;约束的一端是器件外部时钟的上升沿和下降沿启动的数据,另一端是器件内部同时对上升沿和下降沿敏感的触发器的输入数据;

输出延迟

set_output_delay命令设定数据从FPGA输出端口上(都是相对于数据源的时钟来说)到下一级芯片输入端口的输出路径延迟;输出延迟既指数据从FPGA的输出管脚通过板级传输到另一个器件间的相位差,也指相对参考板级时钟间的相位差;输出延迟值同样也可以是正的或负的,由时钟和数据在FPGA器件外的相对相位决定;

约束时的相对时钟可以是一个设计时钟,也可以是一个虚拟时钟;输出延迟命令的选项基本与输入延迟约束相同,还是陈列如下:

同样,输出延迟约束只能应用于输出端口或双向端口,不能用于设计内部的管脚;下面给出几个使用输出延迟约束的典型例子:

- -min和-max:-min设定的值用于最小延迟分析(保持时间、移除时间);-max设定的值用于最大延迟分析(建立时间、恢复时间);如果约束命令中没有使用这两个选项,输入延迟值会同时应用于min和max;

- -clock_fall:用于指定由相对时钟的下降沿捕获的时序路径上的输出延迟约束;如果没有这个选项,Vivado只假定使用相对时钟的上升沿;

- -add_delay:该选项通常用于约束与多个时钟沿相关的输出端口(比如DDR接口同时使用上升沿和下降沿,或者输出端口与几个使用不同时钟的器件相连),而且必须已经存在一个最大或最小输入延迟约束,设计者使用该命令为同一端口设置其它相对时钟沿的最大或最小输入延迟约束;

1.示例一

create_clock -name sysClk -period 10 [get_ports CLK0]

set_output_delay -clock sysClk 6 [get_ports DOUT]定义一个主时钟sysClk作为输出延迟的相对时钟,设定的值同时作为最小值(min)分析和最大值(max)分析;

2.示例二

create_clock -name clk_port_virt -period 10

set_output_delay -clock clk_port_virt 6 [get_ports DOUT]该例子约束目的与上例相同,只是相对时钟换为一个虚拟时钟;使用虚拟时钟的好处是可以在不改变内部设计时钟的情况下,设定任意的抖动和延迟;

3.示例三

create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_IN]

set_output_delay -clock clk_ddr -max 2.1 [get_ports DDR_OUT]

set_output_delay -clock clk_ddr -max 1.9 [get_ports DDR_OUT] -clock_fall -add_delay

set_output_delay -clock clk_ddr -min 0.9 [get_ports DDR_OUT]

set_output_delay -clock clk_ddr -min 1.1 [get_ports DDR_OUT] -clock_fall -add_delay这里相对时钟为DDR的时钟,最小值分析和最大值分析采用不同的输出延迟值;约束的一端是器件外部时钟的上升沿和下降沿启动的数据,另一端是器件内部同时对上升沿和下降沿敏感的触发器的输出数据 ;