I2C总线设计规范之基础篇

I2C通信协议分析

常用IIC接口通用器件的器件地址是由种类型号,及寻址码组成的,共7位。如格式如下:D7 D6 D5 D4 D3 D2 D1 D0

1、器件类型由:D7-D4 共4位决定的。这是由半导公司生产时就已固定此类型的了,也就是说这4位已是固定的。

2、用户自定义地址码:D3-D1共3位。这是由用户自己设置的,通常的作法如EEPROM这些器件是由外部IC的3个引脚所组合电平决定的(用常用的名字如A0,A1,A2)。这也就是寻址码。所以为什么同一IIC总线上同一型号的IC只能最多共挂8片同种类芯片的原因了。

3、最低一位就是R/W位。

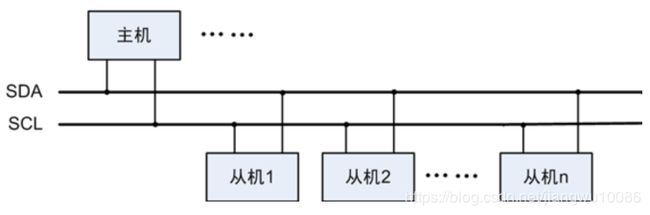

在现代电子系统中,有为数众多的IC需要进行相互之间以及与外界的通信。为了提供硬件的效率和简化电路的设计,PHILIPS开发了一种用于内部IC控制的简单的双向两线串行总线I2C。I2C总线支持任何一种IC制造工艺,并且PHILIPS和其他厂商提供了种类非常丰富的I2C兼容芯片。作为一个专利的控制总线,I2C已经成为世界性的工业标准。

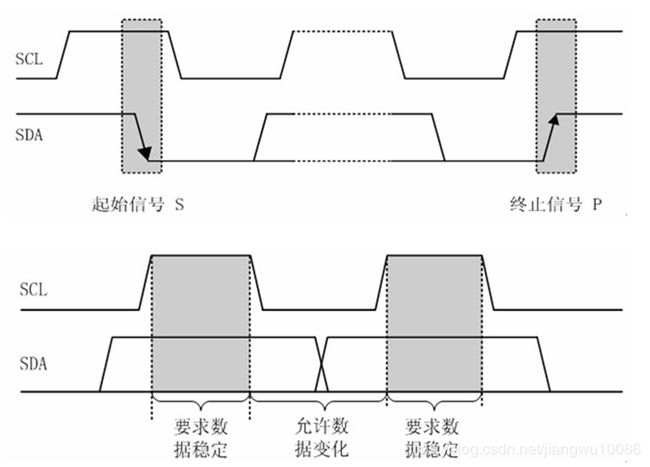

起始和终止信号:

SCL线为高电平期间,SDA线由高电平向低电平的变化表示起始信号;SCL线为高电平期间,SDA线由低电平向高电平的变化表示终止信号。

有效数据信号:

I2C总线进行数据传送时,时钟信号为高电平期间,数据线上的数据必须保持稳定,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。

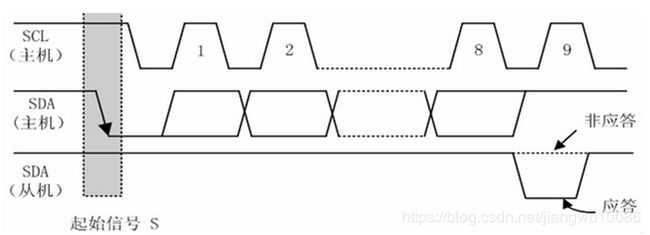

数据传送格式:

每一个字节必须保证是8位长度。数据传送时,先传送最高位(MSB),每一个被传送的字节后面都必须跟随一位应答位(即一帧共有9位)。如果一段时间内没有收到从机的应答信号,则自动认为从机已正确接收到数据。

I2C上拉电阻

由于I2C接口采用Open Drain机制,器件本身只能输出低电平,无法主动输出高电平,只能通过外部上拉电阻RP将信号线拉至高电平。因此I2C总线上的上拉电阻是必须的。

SDA 和 SCL 都是双向线路。连接到总线的器件的输出级必须是漏极开路或集电极开路,都通过一个电流源或上拉电阻连接到正的电源电压,这样才能够实现“线与”功能。当总线空闲时,这 2 条线路都是高电平。总线速率越高,总线上拉电阻要越小。

一般IO端口的驱动能力在2mA~4mA量级。如果RP阻值过小,VDD灌入端口的电流将较大,这导致端口输出的低电平值增大(I2C协议规定,端口输出低电平的最高允许值为0.4V);如果灌入端口的电流过大,还可能损坏端口。故通常上拉电阻应选取不低于1K的电阻(当VDD=3V时,灌入电流不超过3mA)。

上拉电阻RP的计算公式:

最小值为(通常取最大电流为3mA);

最大值为(T=1us 100KHz,T=0.3us 400KHz,是Bus capacitance);

实际应用中,I2C的上拉电阻和阻抗匹配一点关系都没有,纯属open drain上拉。电阻放哪端都一样,离master近了,离slave就远,反过来也一样。主要是担心速率问题,上拉电阻可以减小到2K甚至1K,布线尽可能减少寄生电容的影响。这个速率问题,取决于上拉电阻和线上电容形成的RC延时,RC延时越大,波形越偏离方波趋向于正弦波,上升边缘越平缓,时间越长,则不确定电平的时间就越长,set up time和hold time越长,valid data reading time越短,数据读写正确的概率就越低,所以减小上拉电阻和寄生电容才是正解。

建议:上拉电阻应安置在OD输出端附近。当I2C总线上主从器件(Master & Slave)两端均为OD输出时,电阻放置在信号路径的中间位置。当主设备端是软件模拟时序,而从设备是OD输出时,应将电阻安置在靠近从设备的位置。

I2C局限性

I2C 没有规定的电缆长度,唯一的限制是I2C 总线规范,它规定I2C 的最大电容是400pF,I2C 总线上的负载电容不能超过400pF。如下图所示,当I2C 总线上器件逐渐增多时,总线负载电容也相应增加。当总的负载电容大于400pF 时,就不能可靠的工作。

I2C 总线中存在的不少的局限性,如:

- 7位地址长度,不允许地址冲突;

- 总线上器件的数量和总线长度受限于总线的负载能力;

- 各器件的传输电平和时钟要保持一致;

- 总线的器件不能够进行直接热插拔。

对I2C总线的时钟同步和总线仲裁的深入理解

每一个I2C总线器件内部的SDA、SCL引脚电路结构都是一样的,引脚的输出驱动与输入缓冲连在一起。其中输出为漏极开路的场效应管、输入缓冲为一只高输入阻抗的同相器[1]。这种电路具有两个特点:

- 由于SDA、SCL为漏极开路结构,借助于外部的上拉电阻实现了信号的“线与”逻辑;

- 引脚在输出信号的同时还将引脚上的电平进行检测,检测是否与刚才输出一致。为 “时钟同步”和“总线仲裁”提供硬件基础。

I2C设备对总线的操作仅有“把线路接地”——输出逻辑0。基于I2C总线的设计,线路上不可能出现电平冲突现象。如果一设备发送逻辑0,其他发送逻辑1,那么线路看到的只有逻辑0。也就是说,如果出现电平冲突,发送逻辑0的始终是“赢家”。总线的物理接法允许主设备往总线写数据的同事读取数据。这样两主设备争总线的时候“赢家”并不知道竞争的发生,只有“输家”发现了冲突——当写一个逻辑1,却读到了0——而退出竞争。

时钟同步:如果被控器希望主控器降低传送速度可以通过将SCL主动拉低延长其低电平时间的方法来通知主控器,当主控器在准备下一次传送发现SCL的电平被拉低时就进行等待,直至被控器完成操作并释放SCL线的控制控制权。这样以来,主控器实际上受到被控器的时钟同步控制。可见SCL线上的低电平是由时钟低电平最长的器件决定;高电平的时间由高电平时间最短的器件决定。这就是时钟同步,它解决了I2C总线的速度同步。

总线仲裁:假设主控器1要发送的数据DATA1为“101 ……”;主控器2要发送的数据DATA2为“1001 ……”总线被启动后两个主控器在每发送一个数据位时都要对自己的输出电平进行检测,只要检测的电平与自己发出的电平一致,他们就会继续占用总线。在这种情况下总线还是得不到仲裁。当主控器1发送第3位数据“1”时(主控器2发送“0” ),由于“线与”的结果SDA上的电平为“0”,这样当主控器1检测自己的输出电平时,就会测到一个与自身不相符的“0”电平。这时主控器1只好放弃对总线的控制权;因此主控器2就成为总线的唯一主宰者。

不难看出:

① 对于整个仲裁过程主控器1和主控器2都不会丢失数据;

② 各个主控器没有对总线实施控制的优先级别;

③总线控制随即而定,他们遵循“低电平优先”的原则,即谁先发送低电平谁就会掌握对总线的控制权。

根据上面的描述,“时钟同步”与“总线仲裁”可以总结如下规律:

①主控器通过检测SCL上的电平来调节与从器件的速度同步问题——时钟同步;

②主控器通过检测SDA上自身发送的电平来判断是否发生总线“冲突”——总线仲裁。因此,I2C总线的“时钟同步”与“总线仲裁”是靠器件自身接口的特殊结构得以实现的。