Xilinx PCIE DMA 仿真环境搭建

目录

1、前言

2、仿真环境搭建

3、BMD工程的PIO仿真

4、xapp1052DMA仿真

4.1 testcase

4.2 配置cfg_bus_mstr_enable

4.3 WR DMA仿真

4.4 RD DMA仿真

1、前言

在阅读本文之前,建议刚接触PCIE的读者,请按顺序逐一阅读下面几个内容:

五、Xilinx PCIE CORE学习;

六、Xilinx PCIE DMA--Sparten6/Kintex-7 BMD

七、Xilinx PCIE DMA 仿真环境搭建

win10 jungo windriver

本文在上一篇博客 “六、Xilinx PCIE DMA--Sparten6/Kintex-7 BMD 搭建” 的基础上,讲解如何使用modelsim对建好的BMD工程,搭建仿真环境。

本文搭建了BMD的仿真环境, 通过PIO仿真验证搭建BMD工程的完整性。

通过xapp1052 DMA仿真,举例分析DMA的数据流。

软件环境: ISE14.4/ISE14.7。xapp1052是在vivado环境下运行。

2、仿真环境搭建

在 “Xilinx PCIE DMA--Sparten6/Kintex-7 BMD 搭建” 基础上,

进行下面步骤:

(1)首先,example_design文件夹下的文件全部删除;

(2)章节3里所有代码层次的.V文件,都复制到example_design文件夹里;

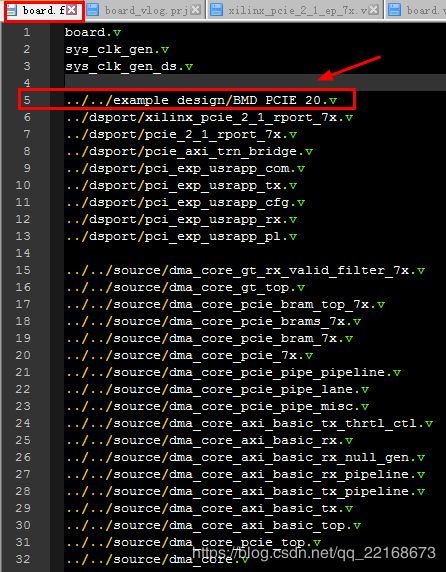

(3)修改\ipcore_dir\dma_core\simulation\functional文件夹里的board.f文件,

将以前PIO的相关内容,替换为下图中红色框框内容。

注意,第五行BMD_PCIE_20.v必须放在最前面编译。

修改后的board.f文件如下图所示。

(4)运行do simulate_mti.do文件后,

可能会报告xilinx_pcie_2_1_ep_7x.v文件里一些管脚未连接的错误信息,注释掉这些行即可。

(注释的过程中,可能会不小心将有用的信号线也给屏蔽掉了。因此,注释的过程中,需要格外小心!)

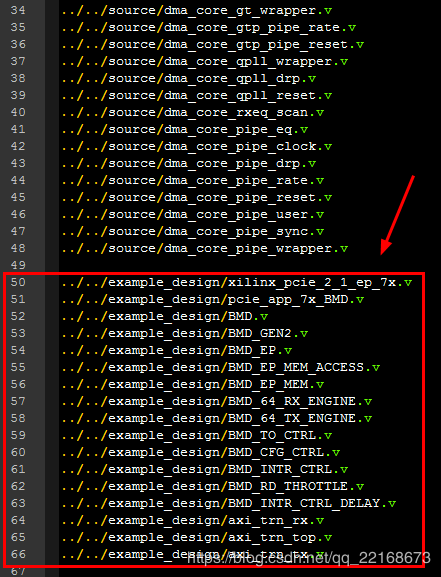

修改后的board.f文件如下图所示:

../../example_design/xilinx_pcie_2_1_ep_7x.v

../../example_design/pcie_app_7x_BMD.v

../../example_design/BMD.v

../../example_design/BMD_GEN2.v

../../example_design/BMD_EP.v

../../example_design/BMD_EP_MEM_ACCESS.v

../../example_design/BMD_EP_MEM.v

../../example_design/BMD_64_RX_ENGINE.v

../../example_design/BMD_64_TX_ENGINE.v

../../example_design/BMD_TO_CTRL.v

../../example_design/BMD_CFG_CTRL.v

../../example_design/BMD_INTR_CTRL.v

../../example_design/BMD_RD_THROTTLE.v

../../example_design/BMD_INTR_CTRL_DELAY.v

../../example_design/axi_trn_rx.v

../../example_design/axi_trn_top.v

../../example_design/axi_trn_tx.v

3、BMD工程的PIO仿真

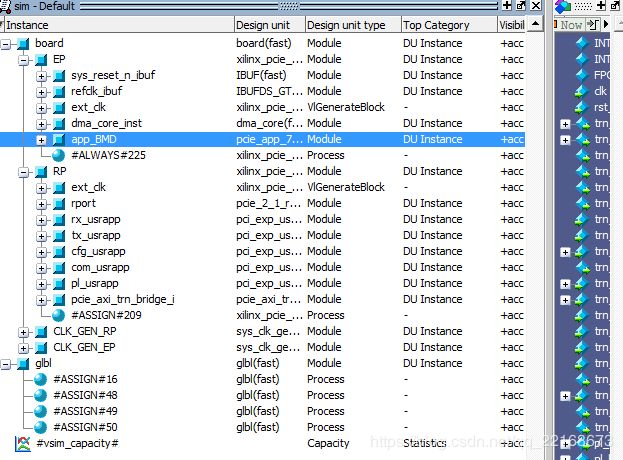

接下来可以进行对该BMD工程的仿真。运行do simulate_mti.do以后,可以看到仿真的层次结构如下图所示。

3.1可能遇到的问题

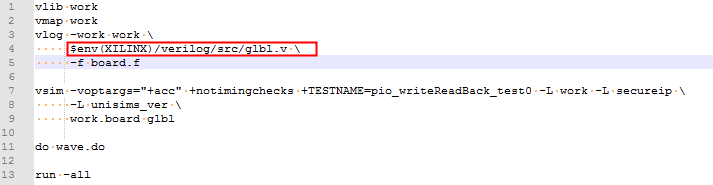

(1)若运行do simulate_mti.do后,modelsim报下面的错误,

打开该文件,可以看到下面的指令,将下面红色圈的部分替换为ISE安装目录下glbl文件的路径即可。

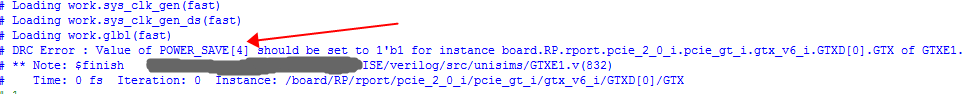

(2)在对Sparten6 pcie仿真时,还modelsim还可能出现下面的错误。

解决方法,将ipcore_dir\pcie_test\simulation\dsport\gtx_wrapper_v6.v文件里的POWER_SAVE[4]设置为1即可解决。

3.2仿真介绍

board:是testbench的顶层;

EP :是章节3里搭建的BMD工程,是Endpoint;

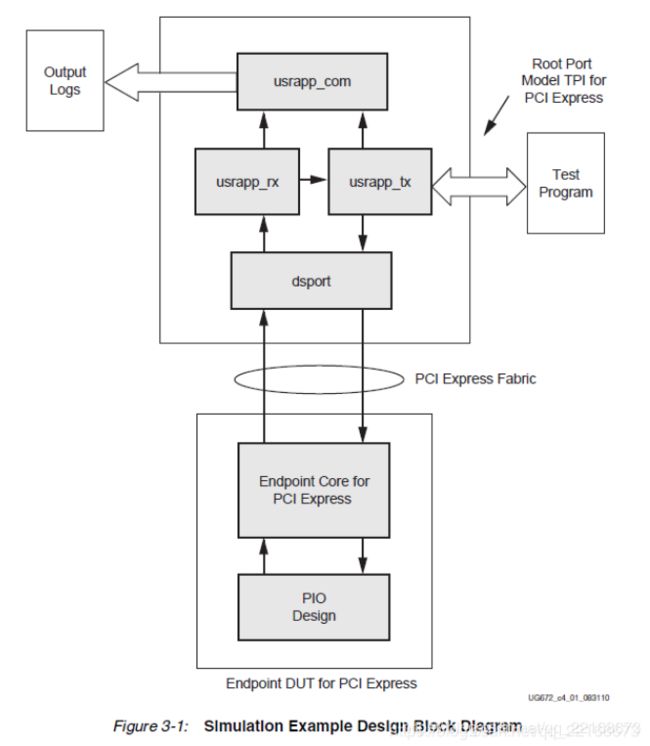

RP :是模拟PC的相关测试环境,如下面有图搭建的测试环境。

dma_core_inst:是例化的PCIE DMA IP Core;

app_BMD :是例化的BMD操作工程。

按照上面的步骤,是可以正确搭建DMA仿真平台的;可以通过PIO仿真验证该平台代码工程的完整性。

但,如果想进行DMA仿真的话,可能还会遇到一些问题,比如:工程搭建的过程中,误将有用的信号线给注释掉了;DMA testcase的配置步骤;如何使能cfg_bus_mstr_enable。

下面会以下xapp1052 DMA仿真进行举例说明。

4、xapp1052DMA仿真

4.1 testcase

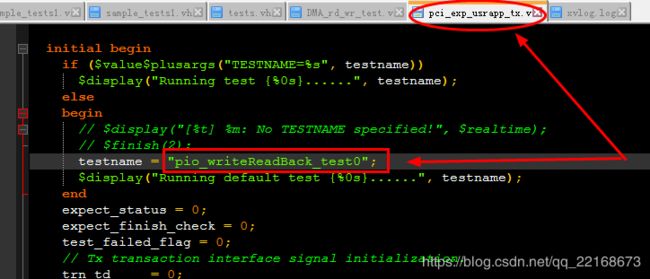

首先,由于xapp1052是在vivado平台下开发的,其testname的引入方式与ISE平台是有区别的。

在vivado的工程里,testname的引入,则不是在simulate_mti.do文件里,其是在pci_exp_usrapp_tx.v文件里引用的。如下图所示

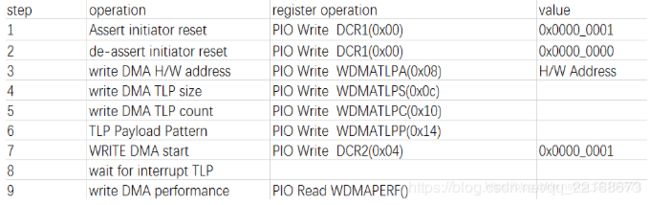

其次,testcase的设计,按照xapp1052中PDF给的配置过程即可。

下面再附上xapp1052给的读写配置步骤吧。

本文提供一种testcase示例。

在本testcase中,配置的是MWR存储器写访问事物,TLP size 是32(十进制),TLP count是20(十进制),TLP pattern是32'haa55_aa55。也即在启动DMA传输的时候,FPGA将会给RP端发送20个TLP数据包,每个TLP数据包含有32个DW,每个DM=32'haa55_aa55。

下载链接: https://download.csdn.net/download/qq_22168673/11607712

将上面链接里的testcase粘贴复制到sample_tests1.vh文件里即可。

4.2 配置cfg_bus_mstr_enable

这里需要注意:

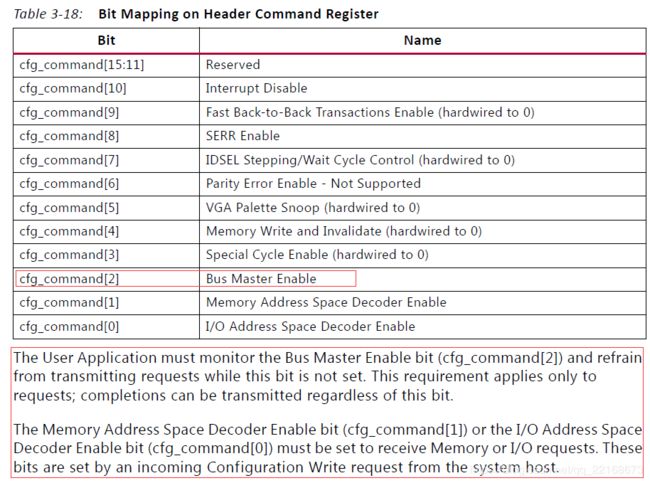

make sure you set the Bus master enable bit on both RP and Endpoint.

在准备好testcase之后,需要修改pci_exp_usrapp_tx.v文件里的有个参数。

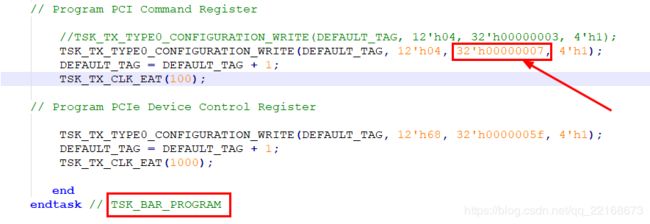

将下图中TSK_BAR_PROGRAM任务中的的value修改为32'h0000_0007即可,该数值是配置cfg_command寄存器使用的。

但,下图的修改,仅是使能EP 端的cfg_bus_mstr_enable。

RP端的Bus master enable 需要在testcase里进行配置。

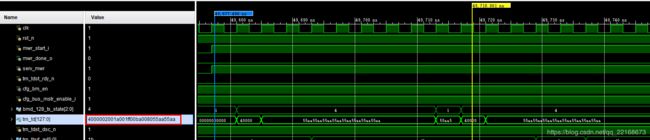

4.3 WR DMA仿真

该仿真,配置步骤参考xapp1052的PDF中配置步骤,RP端模拟PC的相关操作,给EP寄存器进行配置,然后FPGA作为master发起WMR存储器写访问事物,将数据以DMA数据流的方式发送给RP端。

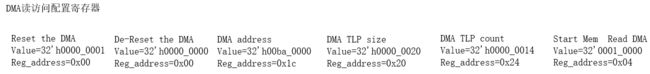

下图中reg_address的值应该参考xapp1052的配置步骤设置,下图后期再修改。

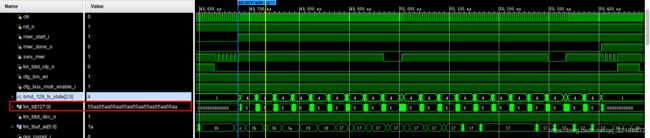

通过下图,可以看到TX连续发送了20个TLP数据包,每个TLP数据包含有32个DW,每个DM=32'haa55_aa55。

然后,再观察第二个TLP头包,可以分析存储器写地址的变化情况。

4.4 RD DMA仿真

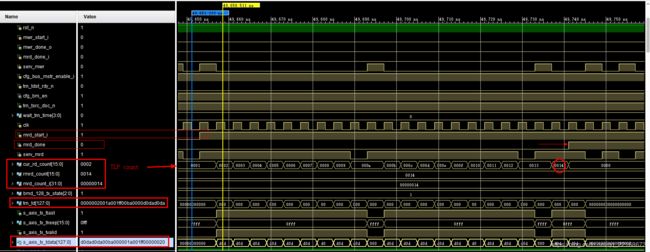

参考xapp1052里的步骤,写testcase,配置 DMA RD的寄存器。

将FPGA配置称为master,之后启动DMA;然后,FPGA会连续发送多个(TLP COUNT)MRd读请求事务;RP端接收到FPGA 发送的MRd事务后,会返回CPLD 数据包。

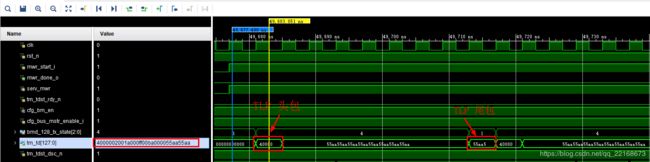

首先是以PIO的方式,配置寄存器信息。如下图所示。

当FPGA接收到RP以PIO方式配置的启动DMA标志后,会连续发送多个(TLP count)MRd存储器读请求事务。该testcase中,是配置20个存储器读请求,即TLP count=20(十进制)。

当RP接收到FPGA发起的存储器读请求之后,会返回CPLD事务。

但是,这里可能会遇到RP_rx端口接收到EP端FPGA发来的读请求之后,RP并没有给FPGA返回CPLD的情况。

应该是,RP端没有发送CPLD DMA数据流的相关task,这部分需要自己设计task、实现RP 返回DMA 的CPLD事务TLP包。

这个问题,论坛里也有相关讨论,大家可以看看

https://forums.xilinx.com/t5/PCI-Express/in-simulation-BMD-Not-read-request-and-completions/m-p/177106

另外一个仿真中大家可能会遇到的问题是,RP端可能接收不到EP发送的DMA MWr写访问事务TLP。这个问题的话,可以看看本文最后的参考文献3,将其中的3行配置信息写到init初始化配置task里试试。

最后,本文提供一种DMA 读访问的testcase示例,

下载链接: https://download.csdn.net/download/qq_22168673/11609362

>>点击这里返回导航页<<

参考文献:

| 作者 | 博客 |

| 1、Buyi_Shizi | xapp1052之dma_test.v |

| 2、Jack-Xu | 一步一步开始FPGA逻辑设计 - 高速接口之PCIe |

| 3、shiyinjita | 关于xilinx的pcie仿真说明!!!!pcie仿真建议看一下 |

| 4、yf869778412 | 如何使用xilinx pcie的源代码 |