vivado2017.4开发vc707(virtex7)(一)上电调试

开学之初老师扔给作者一块开发板vc707 让作者把上面的资源都用一用 准备开始下一步工作。原本想在网上找这块板子的一些中文开发资料,实在是有点少,所以就决定记录下自己的开发过程,与各位相互印证。

安装和license在网上down一下就好了,这里就不写了。

先给vc707上个电,用数据线将板子连上电脑,一般来说是需要下载驱动的,弄一个驱动精灵,扫描一下,然后直接安装就可以了。去网上找这个驱动也是可以的。vc707的手册是UG885,去xilinx官网下一个就行。

然后打开vivado。

该软件以前没有使用过。先跑一个流水灯看看再说。

2.next

3.名字和目录

4.

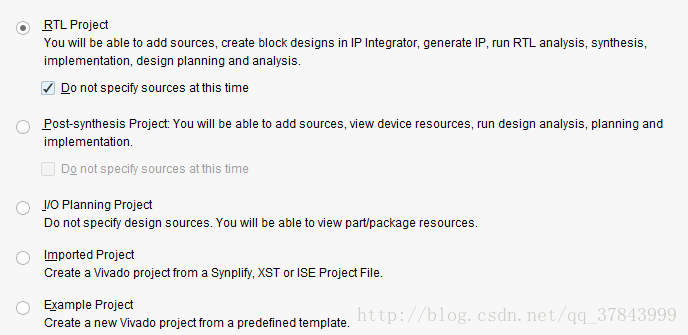

在这里作者讲一下这几个选项的区别。

(1)RTL project

做FPGA的肯定都知道RTL级,简单的就说verilog代码, 行为级就是不一定可以综合的,什么都可以写。RTL级就是行为级里面可以用综合器综合的,综合之后就是门级。这里的RTL project就是可以用来综合的工程,咱们一般就用这个就可以了。

(2)Post-Synthesis Projects

翻译过来是 综合后的工程。这种工程,就是直接添加综合后的网表,然后和前面的RTL工程没什么区别,也是实现布局布线。例如 .ngc, .edif, .edn, .ncd, .dcp这样的文件。可能是本人电脑不够强大,用vivado跑综合实在是有点慢,之后可能会考虑用其他综合工具。

(3)I/O Planning Projects

设置I/O口等等,感觉这个选项没有太大的作用,就看一下I/O布局之类的。

(4)Imported Project

导入其他工具写好的工程。

(5)Example Project

按照预定义的模板建立一个工程。

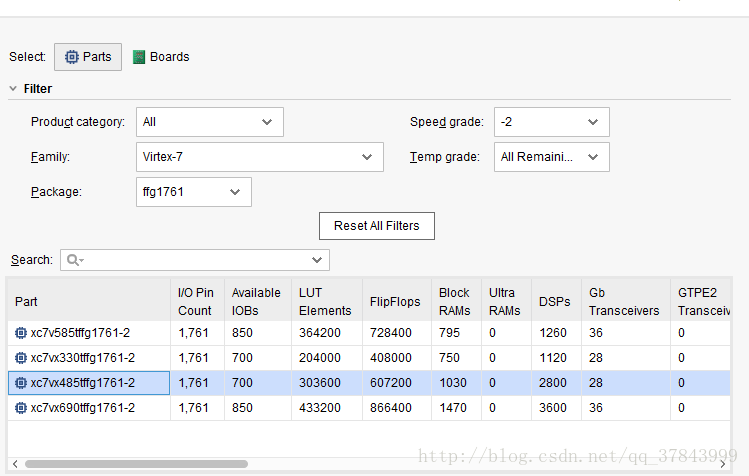

我们选择第一个,VC707的型号如下

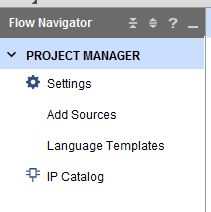

创建之后, add sourse

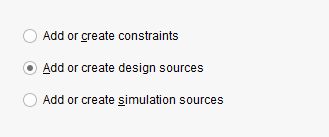

第一个是约束 第二个是普通的文件 第三个是 仿真文件 先选第二个。创建之后开始写代码。

由于板子上只有差分时钟,所以我们需要用上差分转单端的原语。

对于差分时钟信号 ,我们使用IBUFGDS来替代IBUFDS。注意:vc707的reset按钮 按下去的时候 电平是1 ;

这里使用了一个clock ip 把200MHZ转换为5MHZ了。

module top_led(

input sys_clk_p, // 开发板上差分输入时钟 200Mhz

input sys_clk_n,

input rst,

output reg [7:0] led

);

wire sys_clk_ibufg;

wire clk;

IBUFGDS #

(

.DIFF_TERM ("FALSE"),

.IBUF_LOW_PWR ("FALSE")

)

u_ibufg_sys_clk

(

.I (sys_clk_p), //差分时钟正端输入

.IB (sys_clk_n), // 差分时钟负端输入

.O (sys_clk_ibufg) //时钟缓冲输出

);

reg [26:0]count;

clk_wiz_0 instance_name

(

// Clock out ports

.clk_out1(clk), // output clk_out1 5MHZ

// Status and control signals

.reset(rst), // input reset

.locked(), // output locked

// Clock in ports

.clk_in1(sys_clk_ibufg));

always@(posedge clk or posedge rst)begin

if(rst)begin

count <= 0;

led <= 8'b10101010;

end

else begin

if(count ==26'd2499999)begin

count<= 0;

led<={led[6:0],led[7]};

end

else count <=count+1;

end

end

endmodule再添加约束文件

set_property PACKAGE_PIN E19 [get_ports sys_clk_p]

set_property IOSTANDARD LVDS [get_ports sys_clk_p]

set_property PACKAGE_PIN E18 [get_ports sys_clk_n]

set_property IOSTANDARD LVDS [get_ports sys_clk_n]

set_property PACKAGE_PIN AV40 [get_ports rst]

set_property IOSTANDARD LVCMOS18 [get_ports rst]

set_property PACKAGE_PIN AM39 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {led[0]}]

set_property PACKAGE_PIN AN39 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {led[1]}]

set_property PACKAGE_PIN AR37 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {led[2]}]

set_property PACKAGE_PIN AT37 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {led[3]}]

set_property PACKAGE_PIN AR35 [get_ports {led[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {led[4]}]

set_property PACKAGE_PIN AP41 [get_ports {led[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {led[5]}]

set_property PACKAGE_PIN AP42 [get_ports {led[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {led[6]}]

set_property PACKAGE_PIN AU39 [get_ports {led[7]}]

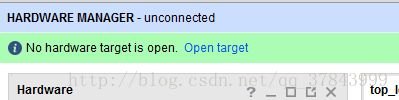

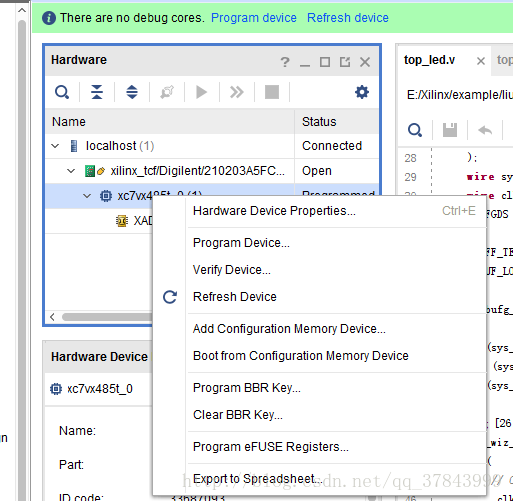

set_property IOSTANDARD LVCMOS18 [get_ports {led[7]}]然后就跑一个bit文件出来 。打开hardware mannager,给板子上电,

这里自动寻找一下。如果找不到,看看是不是没上电 ,JTAG线是不是插错位置了,驱动是不是下好了。

点 program Device,编程完成之后就可以看到现象了。