2019.6.17 Xilinx FPGA Zynq DMA驱动 Linux测试

PL端参考本文:

http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html

https://blog.csdn.net/qq_20091945/article/details/70194026

github:

*使用 vivado2018.2 ,linaro15.4,设备树卡一半内存,设置一半留给操作系统,一半留给FPGA做共享内存,参考微博: https://blog.csdn.net/weixin_40604731/article/details/88751053

*本文为在linux操作系统下的DMA操作,裸机可直接调用API。如有错误之处还请不吝赐教!

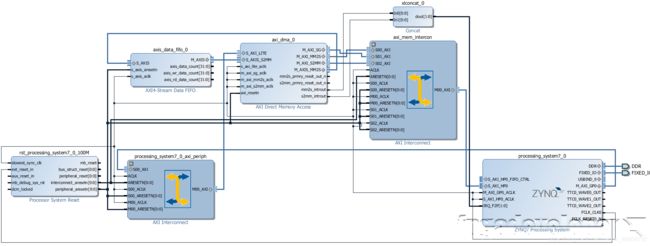

1、PL端连接图(参考PL端参考文本)

2、DMA驱动

*本文DDR为1G,卡一本内存512MB,所以从物理基地址 0x20000000 开始,到0x40000000 为FPGA共享内存。

- 驱动程序,需要在vivado sdk中创建新的linux 应用,生成./elf,直接在linux系统中运行。

#include 主程序

int main()

{

if (FAILURE == dma_init())

exit(1);

for (int i = 0; i < TEST_LENGTH; i++)

{

psrc[i] = TEST_VALUE + i;

}

printf("Plaintext: \n");

memdump(psrc, TEST_LENGTH);

if (FAILURE == dma_start(TEST_LENGTH))

exit(1);

if (FAILURE == dma_sync())

exit(1);

for (int i = 0; i < TEST_LENGTH; i++)

{

printf("%d ",pdest[i]);

}

memdump(pdest, TEST_LENGTH);

}