58--FPGA vivado 两路信号相位差估算

DDS1:20.915MHz,相位偏移为0

DDS2:20.915MHz,相位偏移为pi(可调)

DDS3:20MHz

实验任务:求DDS2和DDS1两路信号的相位差

低通滤波器:

coe文件:

; XILINX CORE Generator™Distributed Arithmetic FIR filter coefficient (.COE) File

; Generated by MATLAB® 9.2 and the DSP System Toolbox 9.4.

; Generated on: 11-Jun-2020 10:12:58

Radix = 16;

Coefficient_Width = 16;

CoefData = 03c3,

0e4e,

2211,

3cd8,

5755,

67f6,

67f6,

5755,

3cd8,

2211,

0e4e,

03c3;

f1=20.915MHz,

f0=20MHz

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2020/06/10 17:13:03

// Design Name:

// Module Name: lpfct

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module lpfct(

input clk,

input s_axis_config_tvalid_dds2,

input s_axis_data_tvalid_fir,

input [15:0]poff2,

input s_axis_cartesian_tvalid,

output [31:0]multda1,

output [31:0]multda2,

output [39:0]firout1,

output [39:0]firout2,

output [39:0]firout3,

output [39:0]firout4,

output [15:0]ct1,

output [15:0]ct2,

output [16:0]obj,

output reg [16:0]fix_down

);

wire [15:0]cos1,cos2,cos3,sin3;

wire [31:0]multda3,multda4;

wire m_axis_phase_tvalid_dds1;

wire m_axis_data_tvalid_dds1;

wire [15:0]m_axis_phase_tdata_dds1;

dds1 your_instance_name (

.aclk(clk), // input wire aclk

.m_axis_data_tvalid( m_axis_data_tvalid_dds1), // output wire m_axis_data_tvalid

.m_axis_data_tdata(cos1), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid_dds1), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata_dds1) // output wire [15 : 0] m_axis_phase_tdata

);

wire m_axis_data_tvalid_dds2;

dds2 dds_2 (

.aclk(clk), // input wire aclk

.s_axis_config_tvalid(s_axis_config_tvalid_dds2), // input wire s_axis_config_tvalid

.s_axis_config_tdata(poff2), // input wire [15 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid_dds2), // output wire m_axis_data_tvalid

.m_axis_data_tdata(cos2) // output wire [15 : 0] m_axis_data_tdata

);

/*dds2 ddds(

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid_dds2), // output wire m_axis_data_tvalid

.m_axis_data_tdata(cos2) // output wire [15 : 0] m_axis_data_tdata

);*/

wire m_axis_data_tvalid_dds3sin;

wire m_axis_data_tvalid_dds3cos;

wire m_axis_phase_tvalid_sin3;

wire m_axis_phase_tvalid_cos3;

wire [15:0]m_axis_phase_tdata_sin3;

dds3_sin abc(

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid_dds3sin), // output wire m_axis_data_tvalid

.m_axis_data_tdata(sin3), // output wire [15 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid_sin3), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata_sin3) // output wire [15 : 0] m_axis_phase_tdata

);

wire m_axis_data_tvalid_sin3;

dds_3cos abc2 (

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid_dds3cos), // output wire m_axis_data_tvalid

.m_axis_data_tdata(cos3) // output wire [15 : 0] m_axis_data_tdata

);

mult_gen_0 mult (

.CLK(clk), // input wire CLK

.A(cos1), // input wire [15 : 0] A

.B(cos3), // input wire [15 : 0] B

.P(multda1) // output wire [31 : 0] P

);

mult_gen_0 mult2 (

.CLK(clk), // input wire CLK

.A(cos1), // input wire [15 : 0] A

.B(-sin3+1'b1), // input wire [15 : 0] B

.P(multda2) // output wire [31 : 0] P

);

mult_gen_0 mult3 (

.CLK(clk), // input wire CLK

.A(cos2), // input wire [15 : 0] A

.B(cos3), // input wire [15 : 0] B

.P(multda3) // output wire [31 : 0] P

);

mult_gen_0 mult4 (

.CLK(clk), // input wire CLK

.A(cos2), // input wire [15 : 0] A

.B(-sin3+1'b1), // input wire [15 : 0] B

.P(multda4) // output wire [31 : 0] P

);

wire s_axis_data_tready_fir1,s_axis_data_tready_fir2,s_axis_data_tready_fir3,s_axis_data_tready_fir4;

wire m_axis_data_tvalid_fir1,m_axis_data_tvalid_fir2,m_axis_data_tvalid_fir3,m_axis_data_tvalid_fir4;

fir_compiler_0 fir1 (

.aclk(clk), // input wire aclk

.s_axis_data_tvalid(s_axis_data_tvalid_fir), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready_fir1), // output wire s_axis_data_tready

.s_axis_data_tdata(multda1[30:15]), // input wire [15 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid_fir1), // output wire m_axis_data_tvalid

.m_axis_data_tdata(firout1) // output wire [39 : 0] m_axis_data_tdata

);

fir_compiler_0 fir2 (

.aclk(clk), // input wire aclk

.s_axis_data_tvalid(s_axis_data_tvalid_fir), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready_fir2), // output wire s_axis_data_tready

.s_axis_data_tdata(multda2[30:15]), // input wire [15 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid_fir2), // output wire m_axis_data_tvalid

.m_axis_data_tdata(firout2) // output wire [39 : 0] m_axis_data_tdata

);

fir_compiler_0 fir3 (

.aclk(clk), // input wire aclk

.s_axis_data_tvalid(s_axis_data_tvalid_fir), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready_fir3), // output wire s_axis_data_tready

.s_axis_data_tdata(multda3[30:15]), // input wire [15 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid_fir3), // output wire m_axis_data_tvalid

.m_axis_data_tdata(firout3) // output wire [39 : 0] m_axis_data_tdata

);

fir_compiler_0 fir4 (

.aclk(clk), // input wire aclk

.s_axis_data_tvalid(s_axis_data_tvalid_fir), // input wire s_axis_data_tvalid

.s_axis_data_tready(s_axis_data_tready_fir4), // output wire s_axis_data_tready

.s_axis_data_tdata(multda4[30:15]), // input wire [15 : 0] s_axis_data_tdata

.m_axis_data_tvalid(m_axis_data_tvalid_fir4), // output wire m_axis_data_tvalid

.m_axis_data_tdata(firout4) // output wire [39 : 0] m_axis_data_tdata

);

wire m_axis_dout_tvalid_cor1,m_axis_dout_tvalid_cor2;

cordic_0 cor1 (

.aclk(clk), // input wire aclk

.s_axis_cartesian_tvalid(s_axis_cartesian_tvalid), // input wire s_axis_cartesian_tvalid

.s_axis_cartesian_tdata({firout2[39:24],firout1[39:24]}), // input wire [31 : 0] s_axis_cartesian_tdata

.m_axis_dout_tvalid(m_axis_dout_tvalid_cor1), // output wire m_axis_dout_tvalid

.m_axis_dout_tdata(ct1) // output wire [15 : 0] m_axis_dout_tdata

);

cordic_0 cor2 (

.aclk(clk), // input wire aclk

.s_axis_cartesian_tvalid(s_axis_cartesian_tvalid), // input wire s_axis_cartesian_tvalid

.s_axis_cartesian_tdata({firout4[39:24],firout3[39:24]}), // input wire [31 : 0] s_axis_cartesian_tdata

.m_axis_dout_tvalid(m_axis_dout_tvalid_cor2), // output wire m_axis_dout_tvalid

.m_axis_dout_tdata(ct2) // output wire [15 : 0] m_axis_dout_tdata

);

c_addsub_0 sub (

.A(ct2), // input wire [15 : 0] A

.B(ct1), // input wire [15 : 0] B

.CLK(clk), // input wire CLK

.S(obj) // output wire [16 : 0] S

);

always@(posedge clk)begin

if(obj[16]==1'b0)

begin

if(obj==17'd0)begin

fix_down <= 17'b0;

end

else begin

fix_down<=obj;

end

end

else begin

if(obj[15:0]>16'b011_0010_1111_1000)begin

fix_down <= 17'b0011_0010_0100_00001 + obj+ 17'b0011_0010_0100_00001;

end

end

end

endmodule

```csharp

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2020/06/10 18:31:33

// Design Name:

// Module Name: tbtst

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module tbtst(

);

reg clk;

reg s_axis_config_tvalid_dds2;

reg s_axis_data_tvalid_fir;

reg [15:0]poff2;

reg s_axis_cartesian_tvalid;

wire [31:0]multda2;

wire [31:0]multda1;

wire [39:0]firout1;

wire [39:0]firout2;

wire [39:0]firout3;

wire [39:0]firout4;

wire [15:0]ct1,ct2;

wire [16:0]obj;

wire [16:0]fix_down;

lpfct u1(.clk(clk),.s_axis_config_tvalid_dds2(s_axis_config_tvalid_dds2),.poff2(poff2),

.multda2(multda2),.multda1(multda1),.s_axis_data_tvalid_fir(s_axis_data_tvalid_fir),.firout1(firout1),

.firout2(firout2),.firout3(firout3),.firout4(firout4),.s_axis_cartesian_tvalid(s_axis_cartesian_tvalid),

.ct1(ct1),.ct2(ct2),.obj(obj),.fix_down(fix_down)

);

initial begin

clk<=1'b0;

s_axis_config_tvalid_dds2<=1'b1;

s_axis_data_tvalid_fir<=1'b1;

s_axis_cartesian_tvalid<=1'b1;

poff2<=16'd32768;

#60000 poff2<=16'd16384;

end

always #5 clk<=~clk;

endmodule

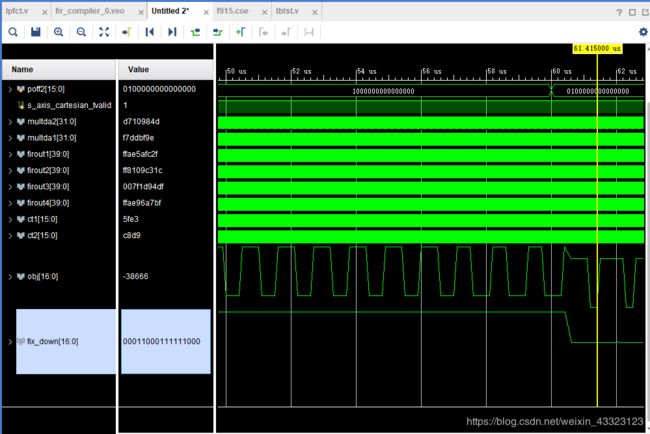

仿真波形:

相位控制字为2^15时(相位宽度为16),相位差为0011.0010001101001=3.1378,接近pi

相位控制字为2^14时,相位差为1.56与pi/2=1.57相近。

文章参考

https://blog.csdn.net/qq_39809425/article/details/94211249

我是仿照这篇博客来完成的…不过原理分析是按照更简易的数学方法来写的。